Запоминающая матрица

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (11) 525156 (61) Дополнительное к авт. свид-ву(22) Заявлено 25.03.75 (21) 21 16915 24 с присоединением заявки № (23) Приоритет— (43) Опубликовано 15.08.76. Бюллетень № 30 (45) Дата опубликования описания 21.02.77 (51) M. Кл.

Я- 11 С 11/00

Государстаенный комитет

Соаета Министров СССР по делам изобретений и открытий (53} УДК 681.327.66 (008,8) (72) Авторы изобретения

F. П. Балашов, М. С. Куприянов и Г. A. Петров (71) Заявитель

Ленинградский ордена Ленина электротехнический институт им. B. И. Ульянова (Ленина) (54) ЗАПОМИНАИШАЯ MATPHLIA

Изобретение относится к области вычислительной техники и может быть использовано при построении устройств хранения дискретной информацич.

Известньа матрицы запоминающих устройств (ЗУ), содержащие элементы памят9. объединенные по строкам и столбцам, и логические элементы.

Известна матрица ЗУ,. содержащая числовые линейки„состоящие из элементов памя- 10 ти, разрядные и адресные шины )1). Недостатком такой матрицы является низкая помехоустойчивость.

Наиболее близкой по технической сущности к данному изобретению является матрица 15

ЗУ, содержащая числовые линейки, состоящие из элементов памяти, соединенных с адресной шиной, и основных логических элементов И, подключенных к шине считывания .постоянной информации, и разрядные шины 20 (21.

Недостатком такой матрицы является низкая надежность.

Цель изобретения — повышение надежности матрицы ЗУ. 25

Это достигается тем, что матрица содер жит в каждой числовой линейке дополнительные логические элементы И, каждый из которых подключен к выходу соответствующего элемента памяти, разрядной шине и шине считывания оперативной информации, а основные логические элементы И подключены к соответствующим адресной и разрядной шж нам.

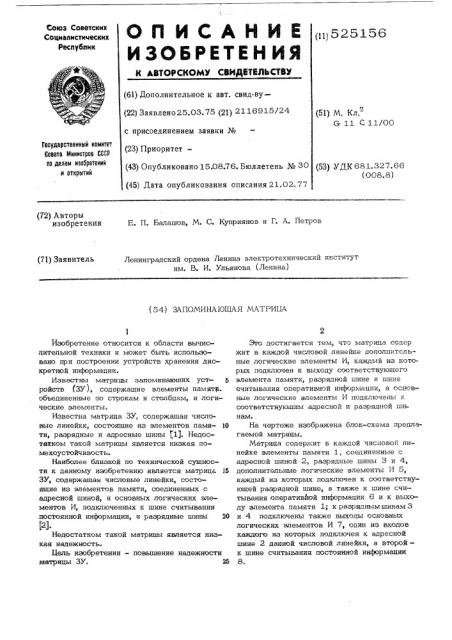

На чертеже изображена блок-схема предлагаемой матрицы.

Матрица содержит в каждой числовой линейке элементы памяти 1, соединенные с адресной шиной 2, разрядные шины 3 и Ф, дополнительные логические элементы И 5, каждый из которых подключен к соответствующей разрядной шине, а также к шине считывания оперативйой информации 6 и к выходу элемента памяти 1; к разряднымшинам3 и 4 подключены также выходы основных логических элементов И 7, один из входов каждоГо из которых подключен к адресной шине 2 данной числовой линейки, а второй— к шине считывания постоянной информации

3

Если в данном разряде хранится "0" постоянного числа, то к логическому элементу

И 7 подключена, например, разрядная шина

3, если "1 ; — то разрядная шина 4.

При записи информации в матрицу подают-5 ся сигналы на одну из адресных шин 2, разрядные шины 3 и 4 и шину считывания оперативной информации 6. Если в данный разряд записывается единица, то сигнал поступает по разрядной шине 4 через логический элемент И 5 в элемент памяти 1. При этом элемент памяти был в единичном сос1 тоянии, то изменение его состояниянепроисходит, Если элемент памяти был в нулевом состоянии, происходит изменение его состо- 15 яния на противоположное.

При записи нуля в данный разряд сигнал подается на разрядную шину 3, в остальном процесс записи "0" аналогичен процессу записи "1". 20

Для считывания оперативной информации сигналы подаются на одну из адресных шин 2 и шину считывания оперативной информации 6.

Если элемент памяти хранил "1", то 26 открывается логический элемент И 5 и появляется информация на разрядной шине 4, если элемент памяти хранил "0", то открывается другой логический элемент И 5 и информация появляется на разрядной шине 3. ЗО

При считывании постоянной информации сигналы подаются на одну из адресных шин

2 и шину считывания постоянной информации

8. Если в данном разряде хранится "0" постоянного числа, то открывается логичес- б кий элемент И 7 и информация появляется на разрядной шине 4.

Из рассмотрения режимов работы матрицы следует, что логические элементы И 5 работают в режиме двусторонней проводимости. В качестве такого логического элемента может служить, например, МОП-транзистор, у которого исток исток взаимозаменяемы.

Анализ режимов работы матрицы показывает, что сигнал считывания постоянной информации не влияет на состояние элементов памяти и поэтому к его форме и величине не предъявляются жесткие требования.

Формула изобретения

Запоминающая матрица, содержащая числовые линейки, состоящие из элементов памяти, соединенных с адресной шиной, и основных логических элементов И, подключенных к шине считывания постоянной информации, и разрядные шины, о т л и ч а ющ а я с я тем, что, с целью повышения надежности матрицы, она содержит в каждой числовой линейке дополнительные логические элементы И, каждый из которых подключен к выходу соответствующего элемента памяти, разрядной шине и шине считывания оперативной информации, а основные логические элементы И подключены к соответствующим адресной и разрядной шинам.

Источники информации, принятые во внимание при экспертизе:

1 . Авт. св, № 342222 кл. &11 С 11/40, опубл. 04. 07. 1 97 О, 2. Хоу, Мейли "Электроника", 1971 r., № 17, с. 49 (прототип) ..

525156

Составитель Ю. Розенталь

Н. Каменская Техред И. Ковач Корректор И. Гоксич

Редактор

Заказ 5088/581 Тираж 723

БНИИПИ Государственного комитета по делам изобретений

13 3035, Москва, Ж-35, Раушская

Филиал ППП "Патент"„г. Ужгород, ул. Проектная, 4

1 1

1

Подаисное

Совета Министров СССР и открытий наб., д, 4/5