Электрический аналоговый накопитель

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11) 525164 (61) Дополнительное к авт. свид-ву(22) Заявлено 27.03.75(21) 2117693/24 с присоединением заявки № (23) Приоритет (43) Опубликоваио15.08.76.Бюллетень № 30 (45) Дата опубликования описания 15.02.77

2 (51) М. Кл.

G 11 С 27/00

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий (53) УДК628.327.66 (088.8) (72) Авторы изобРЕтенин А. Д. Табаков, И, Н. Мазов и П. П. Втулкин (71) Заявитель (54) ЭЛЕКТРИЧЕСКИЙ АНАЛОГОВЫЙ НАКОПИТЕЛЬ

Изобретение относится к вычислительной технике и может быть использовано при аналого-цифровом преобразовании изменяющегося во времени напряжения входного сигнала в цифровой код.

Известны электрические аналоговые накопители на транзисторах, предназначенные для запоминания напряжения, поданного на конденсатор (1).

Наиболее близким к данному изобретению щ по своей технической сущности является электрический аналоговый накопитель, содержащий дифференциальный усилитель, соединенный с первым генератором тока, причем первый вход дифференциального усили- 1б теля соединен со входом накопителя, à ïåðвый и второй выходы - со входами первого и второго оконечных усилителей соответственно, между выходами оконечных усилителей включены соединенные последовательно оп диоды, общая точка соединенич которых подключена к блоку запоминания, выполненному на конденсаторе, и входу буферного усилителя, выход которого соединен с выходом накопителя и со вторым входом дифференци- 25 ального усилителя, выход первого оконечного усилителя соединен с третьим генератором тока, а выход второго оконечного усилителя соединен со вторым генератором тока (21.

XGpBKTepHoH особенностью указанного накопителя является работа в двух режимах: слежение за входным сигналом и хранение запомненных значений входного сигнала.

Переключение из одного режима в другой осуществляется сигналом управления.

Недостатком такого накопителя являетая запаздывание выключения оконечных усилите--.. лей и запирания диодов относительно фронта управляющего сигнала, переключающего накопитель в режим хранения. Запаздывание вызвано инерционными свойствами дифференциального усилителя, т. к. сигнал управления сначала выключает дифференциальный усилитель, и лишь после этого выключаются оконечные усилители и запираются последовательно соединенные диоды.

Запаздывание приводит к возникновению ошибки при измерении входных сигналов, изменяющихся во времени.

Например, при входном сигнале

U5 У Ь. in mt где У вЂ” амплитуда входного сигнала, ц> — частота 5 задержка выключения диодов относительно фронта управляющего сигнала, называемая апертурным временем 7се, приводит к появлению апертурной ошибки h е1-, определяемой как изменение входного сигнала за Я время Те1.

В установившемся режиме работы напряжение на запоминающем конденсаторе равно

У5, с малой погрешностью.

Изменение U „вэ времени определяется 15 как с Ug„

LU УЕЕЕ С Е.Е

Е Ф и имеет максимальное значение прие.=п, т.-е. ") = coU, а максимальная величина ошибки е1С из-за апертурного времени:

Q =03 U I„

Келью изобретения является повышение точности работы накопителя за счет уменьшения величины апертурного времени.

Зто достигается тем, что в схему накопителя введены согласующий и коммутирующий блоки, выполненные на транзисторах, причем базы транзисторов согласующего блока подключены к выходу накопителя, коллектор первого транзистора сэгласующего блока сэедичен с шинэй питания, а коллектор втэрэгэ транзистора сэгласующегэ блэка — с первым генератором тэка, эмиттер каждэгэ из транзисторов согласующего блэ- g) ка соединен с выхэдэм сээтветствую.цегэ оконечного усилителя, база транзистора кэммутирующегэ блэка соединена с командным зхэдэм накопителя, кэллектэр — сэ вторым генератором тэка, а эмиттер — с третьим 45 генеэатэрэее тэка.

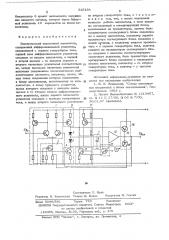

На чертеже представлена схема накопителя

Дифференциальный усилитель 1 соединен с первым генератэээм 2 тэка и подключен 59 первым входом zo входу накопителя, а перВьем и вторыеч! вьехэдэм ко входам первого оконечнэго усилителя 3 и второго оконечного усилителя 4 соэтьетственнс.

Между выхэдами оконечных усилителей 55

3,4 включены разделительные элементы— диоды 5 и 6, соединенные последовательно.

Обц,ая тачка диодов 5, 6 соединена с блоком

7 запоминания вьепэлненным на конденсаторе

8. Транзистор 9 коммутирующего блока 10 6О соединен коллектором со вторым генератором

li тока, а эмиттером — с третьим генератором 12 тока. База транзистора 9 соединена с командным входом накопителя.

Вход буферного усилителя 13 подключен к общей точке диодов 5, б,а выход — к выходу накопителя и ко второму входу дифференциального усилителя 1.

Выход первого оконечного усилителя 3 соединен с третьим генератором 12 тока, выход второго оконечного усилителя 4— со вторым генератором 11 тока. Базы первого и второго транзисторов 14 и 15 согласующего блэка 16 соединены с выходом накопителя, коллектор первого транзистора 14 — с шиной питания +E, коллектор второго транзистора 15 — с первым генератором 2 тока,эмиттер каждого из транзисторов

14 и 15 согласующего блока 16 соединен с выходом соответствующего оконечного усилителя 3 и 4.

В режиме слежения за напряжением вход« ного сигнала дифференциальный усилитель

1 включен и усиливает разность напряжений сигналов У.„и 05,„и через первый и второй оконечные усилители 3, 4 и разде лительные элементы-диоды 5, 6 заряжает конденсатор 8., напряжение с которого через буферный усилитель 13 с коэффициентом усиления К=Х передается на выход накопите ля, где устанавливается напряжение Ugb,ïðaêтически равное Ugq и совпадающее с ним пэ фазе. еери этом транзисторы 14, 15 согласующего блока 16 выключены.

При переключении накопителя в режим хранения отрицательным перепадом управляющего сигнала (. „> выключается транзис тор 9 коммутирующего блока 10, включаются второй и третий генераторы 11, 12 тока„и транзисторы 14, 15 согласующего блока 16. Г1ри включении транзистора 15 начинает выключаться транзиеч эр первого гечератора 2 тока. В результате в начале переходного процесса второй и третий генеpaTopsr Toxa leper a " Ha ce6a ToK oKoHezных усилителей 3,4„. находящихся еще во включенном состоянии и тем самым сокращают время переключения разделительньех элементов-диодов 5, 6. Диоды 5, 6 начинают запираться и предотвращают разряд кочденсатора 8.

В конце переходного процесса в результате выключения дифференциального усилителя lзапираются оконечные усилители 3,4.Задержка их выключения обусловлена инерционными свойствами дифференциального усилителя 1. На коллекторах транзисторов оконечных усилителей 3, 4 устанавливаются потенциалы эмиетеров эткрывшихся транзисторов 14, 15 согласуеэщего блока 16. Диоды 5, 6 заперты.

5251

Составитель Е. Брик

Редактор Н. Каменская Техред И. Ковач Корректор И. Гоксич

Заказ 5088/581 Тираж 723 Подписное

БНИИПИ Государственного комитета Совета Министров по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

СССР

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Конденсатор 8 хранит запомненное напряжение входного сигнала, которое через буферный усилитель 13 передается на выход накопителя.

Формула изобретения

Злектрический аналоговый накопитель, содержащий дифференциальный усилитель, 1О соединенный с первым генератором тока, первый вход дифференциального усилителя соединен со входом накопителя, а первый и второй выходы - со входами первого и второго оконечных усилителей соответствен- д но, между выходами оконечных усилителей включены соединенные последовательно разделительные элементы, например, диоды, общая точка соединения которых подключена к блоку запоминания, выполненному на кон- 2О денсаторе, и входу буферного усилителя, выход которого соединен с выходом накопителя и со вторым входом дифференциального усилителя, выход первого оконечного усилителя соединен с третьим генератором 5 тока, а выход второго оконечного усилителя1 5 со вторым генератором тока, о т л и ч а юшийся тем, что, с целью повышения точности работы накопителя, в него введены согласующий и коммутирующий блоки, выполненные на транзисторах, причем базы транзисторов согласующего блока подключе-, ны к выходу накопителя, коллектор первого транзистора согласующего блока соединен с шиной питания, а коллектор второго транзистора — с первым генератором тока, эмиттер каждого из транзисторов согласующего блока соединен с выходом соответствующего оконечного усилителя, база транзистора коммутирующего блока соединена с командным входом накопителя, коллектор - co вторым генератором тока, а эмиттер — с третьим генератором тока.

Источники ниформации принятые во внимание при экспертизе изобретения:

1. В. Н. Жовинский, "Схемы запоминания напряжений и блоки запаздывания", Госэнергоиздат, 1 963 г.

2. Патент Великобритании ¹ 1213457, кл. G 11 С 27/00, Cj 06 Q 7/00, 30. 0 1. 67 (прототип ) .