Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Союз Советскии

Со (и)525241

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОФАУ СЗИДИЙЛЬСТВМ (61) Дополнительное к авт. свид-ву (22) Заявлено 11.04.75 (21) 2123 30/21 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано15.08.7ЮБюллетень ¹ 30 (45) Дата опубликования описання05.11.76 (51) М. Кл.

Н 03 К 13/17

Гаоударстввииый ионитвт

Совета Министров СССР во деяая ивоорвтвиий и втираний (53) УДК681.325 (088.8) (72) Автор изобретения

В. Я. Загурский

Институт электроники и вычислительной техники

АН Латвийской CCP (71) Заявитель (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к импульсной технике, в частности, к устройствам.аналого-цифрового преобразования, и может быть использовано в системах обработки информации. 5

Известны аналого-цифровые преобразователи с обратной связью, в которых осуществляется следящее уравновешивание, имеющие весьма сложную структуру и относительно низкое быстродействие fl) . тв

Известен также аналого-пифровой преобразователь параллельного уравновешивания с высоким быстродействием, структура которого существенно упрощена (2). Он содержит генератор стробимпульсов, выход которого соединен с управляющими входами схем сравнения, первые аналоговые входы которых подключены к источнику преобразуемого сигнала, вторые аналоговые входы — к узлам резистивного делителя, один 20 вывод которого подключен к выходу источника эталонного напряжения, а другой вывод — к обшей шине, первые выходы каждой схемы сравнения через соответствующие элементы И соединены с первыми вхо- 25 дами триггеров, а вторые выходы всех схем сравнения, кроме схемы сравнения младшего разряда, подключены к вторым входам элементов И предыдущих разрядов, второй выход схемы сравнения младшего разряда соединен через элемент ИЛИ с вторыми входами триггеров, второй вход элемента

ИЛИ подключен к выходу элемента И младшего разряда и входу инвертора, причем третьи входы всех элементов И, кроме старшего разряда, и вход элемента И старшего разряда через линию задержки подключены к выходу генератора стробимпульсов.

Недостатки известного устройства следующие. Количество цифровых управляемых сопротивлений, ключей и входов логических элементов возрастает в зависимости ст количества разрядов, причем возрастание происходит по геометрической -.)огрессии. Это сильно усложняет структуру преобразователя, ограничивает максимальное число разрядов и за уменьшения надежности работы.

Синхронизация работы преобразователя осуществляется только по отношению к выводу пифрового кода, а сшчхронизапня переход5243. предыдущих разрядов, второй выход 8 схемы сравнения младшего разряда соединен через элемент 12 ИЛИ со вторыми входами 16 триггеров, второй вход элемента 12 ИЛИ под- ключен к выходу элемента 11 И младшего разряда и входу инвертора 13, причем третьи входы всех элементов ll и кроме старшего разряда, и вход элемента И старшего разряда через линию задержки 4 подключены к щ выходу генератора стробимпульсов 3, управляющие входы аналоговых кгаочей 1 3 подключены к выходам триггеров 14, сигнальные входы через соответствующие резисторы - к обшей шине,.а выходы - к втои> рому входу 2 схемы сравнения 6 младшего разряда. Резисторы резистивного делите- ля 9, включенные последовательно, имеют герон в зависимости от разрядности и упрощает конструкщпо преобразователя. ЗО

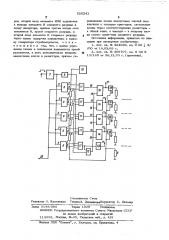

На чертеже показана блок-схема предлагаемого преобразователя где: 1 - управляющий вход генератора стробимпульсов, 2аналоговые входы схемы сравнения, 3 - ге35:. единицах следующим рядом:16; 8; 4; 2; 1, (начинря со старшего разряда), на выходах 17 сигналы соответствуют логиче кому нулю; генератор стробимпульсов 3 выключен, на входах 5, 15, 16 и выходах 7, источник эталонного напряжении, 11 - эле- 4О мент И, 12 - элемент ИЛИ, 13 — инвертор, l4 - триггер, 15 - первый вход триггера, |

16» второй вход триггера, 17 — выход параллельного кода, 18 — аналоговый ключ, 19 - выход аналогового ключа, 20 - входная шина.

Выход генератора стробимпульсов 3 соединен с управляющими входами 5 схем срав-. l пения 6, первые аналоговые входы к орых, подключены к входной шине 19 преобразова- 156 теля, вторые аналоговые входы 2 - к узлам резистивного делителя 9, один вывод которо- го подключен к выходу источника эталонного напряжения 10, а другой — к общей шине, первые выходы 7 каждой схемы сравнения через соответствующие элементы 11 И сое- динены с первыми входами 15 триггеров 14, а вторые выходы 8 всех схем сравнения,. I кроме схемы сравнения младшего разряда, подкачены к вторым входам элементов И

Ю ных процессов непосредственно в самом преобразователе отсутству т. Эуо, в особенности при неидеальности элементов, при

1 водит к хаотичному наложению переходных процессов переключения схем сравнения при ! резких изменениях входного напряжения, триггеров и логических элементов. Поэтоьф схемы сравнения работают в тяжелом режи-: ме многократного несинхронного переключе- ния из одного состояния в другое иэ-за

| помех, возникающих на выходах триггеров, что снижает надежность работы преобразо- I вателя.

Целью изобретения является упрощение схемы преобразователя и увеличение надежности его работы.

Это достигается тем, что в преобразо1 ватель дополнительно введены аналоговые ключи и резисторы, причем управляющие входы аналоговых ключей подключены к выходам триггеров, сигнальные входы через соответствующие резисторы — к обшей ши7 не, а выходы - к второму входу схемы ! сравнения младшего разряда.

Ч акая структупа I преобразователя пось- i воляет исключить прогрессивное возрастание количества логических. элементов, ключей, цифровых управляемых сопротивлений, триг 1 нератор стробимпульсов, 4 - линия эадержкь, 5 — управляющий вход схемы сравнения, 6 — схемы сравнения, 7 — первый выход схемы сравнения, 8 — второй выход схемы сравнения, 9 - резистивный делитель, 10распределение весов в соответствии с двоич ным законом, то есть, резистор 9, подключенный к источнику эталонного напрйжения

10 имеет вес, равный восьми условным единицам, следующий - четырем, следующийдвум и так далее до одного. Напьлжение на аналоговом входе 2 схемы сравнения 6,младшего разряда определяется весом парал-, лельно включенных аналоговых ключей 18 ,и резистора резистивного делителя 9 vaagщего разряда, суммарный вес которых равен 1. За исходное примем состояние, когр8 входное напряжение равно нулю, а на входе 1 отсутствует управляющий потенциал.

В исходном состоянии все аналоговые ключи 18 включены и на входах 2 схем сравнения 6, напряжения представлены в условных

J.

8 - сигналы логического нуля.

Преобразователь работает следующим образом.

При подаче разрешающего потенциала на вход 1 включается генератор 3 и начинается периодический опрос импульсными сигналами логической единицы схем сравнения 6. Через интервал Г, определяемый линией задержки 4, осуществляется опрос элементов

11 И. Величина Г определяется задержкой, срабатывания схем сравнения 6 и может быть весьма малой (единицы нс ).

Предположим, что по входу 20 действует напряжение величиной одиннадцать условных единйц. При воздействии стробимпульса происходит срабатывание всех, кроме старшей, схем сравнения 6, в результате чего на выходах 7 появляется сигнал логической единицы, а на выходах 8 - логический ноль„

Срабатывание логических элементов 11 И во всех разрядах, кроме четвертого, вэаим! 6252

;но блокируется. Действующий через время сигнал производит опрос элементов 11 И

1 при установившихся состояниях выходов 7, 18 схем сравнения 6, поэтому1ломехи на вы» ходах алементов 11 И отсутствуют. Это су» 5 шестверно увеличивает надежность работы преобразователя.

Сигнал с выхода элемента 11 И третье« го разряда включит по входу 15 триггер 14. На выходе 17 атогс разряда появится сиi, N нал! логическок* единьцы и аналоговый ключ (18 отк иочит цифровое управляемое сопротив ление от выхода 19. В результате суммар-! ный вес резистора младшего разряда иэменится, а именно увеличится пропорц:го- 15 нально весу включенного разряда, то есть на во".åìü условных единиц. Таким образом . шкала порогов схем сравнения 6 изменится в соответствии со следующим разбиением ,в условных еди..идах напряжения 24; 16; 90 ;12; 10; 9 (начиная со старшего разряда).

Следующий стробимпульс произведет опрос . схем сравнения 6,, в результате чего сработает триггер разряда, соответствующего

2 . Шкала порогов изменится в соответс г-!

Бии с числами: 26; 18;l14; 12„ 11.

8 следующем такте сработает схема

9 ,сравнения младшего разряда 2, произойдет установка через элемент 12 ИЛИ всех триггеров, причем переход 1- О на выходах ЗО

17 всех разрядов фиксирует код, соответ ствующий коду 1, а отсутствие такого перехода, соответствует коду О, И данном случае,начиная со старшего разряда, будем иметь код,01011, то есть одиннадцать.

Период повторения стробимпульсов равен суммарной задержке в последовательной цепи: чогический элемент 11 И, триггер 14, аналоговый ключ, 18. Таким образом, в зависимости от применяемых элементов,аоста-4О точно лишь варьировать частоту повторения ! строГ мпульсов, чтобы обеспечить синхронизацию переходных процессов в преобразовареле. Очевидно, что воздействие уравновешивающего напряжения на схему сравнения

I происходит в промежутках между стробирую шими сигналами, что облегчает режим ее работы в динамике. Опрос схем сравнения производится в установившемся режиме. Это бО

lyMeBtmaeT динамическую погрешность и увеl личивает надежность работы.

Режим разоты преобразователя является ! квазпадаптивным по отношению к величине ,и скорос-;и измерения входного сигнала. При

) малой скорости, изменения входного сигнала

Г .! время преобразования определяется числом строб:.",. зяий: в зависимости от величины (1нап.:яжения на входе 20 может потребовать, ся одно или несколько стробирований до мо.

69 мента выдачи параллельного кода. Например, 41

6 для напряжения, равного одиннадцати условным единицам потребовалось три стробимпу п са, для напряжения, равного1семнадцати условным единицам - два. В первом случае необходимое время преобразования состоит из двух периодов повторения стробнмпульсов, во втором — иэ одного.

1Количество стробимпульсов определяетСя срабатыванием схемы сравнения 6 младmего разряда 2 . Если напряжение по вхо-у 20 превышает пороговое напряжение а ее входе 2, а запрещающий сигнал с выхода 8 схемы сравнения 6 предшествуюmего разряда отсутствует, то сигнал с вы» хода 7 схемы сравнения 6 младшего разряда фиксирует окончание цикла преобразования, Если напряжение на входе 20 меньше порогового на входе 2 схемы сравнения

6 младшего разряда, то сигнал на выходе 8 этой схемы также фиксирует окончание цикла преобразования. Такой принцип действия дает преимушества при резких изменениях входного напряжения больших величин веса младшего разряда. Если резкое изменение величины входного напряжения совпадает с темпом преобразования, то цикл преобразования не прерывается, а точная оценка выдается в конце цикла.

Если ато изменение не согласовано, то цикл преобразования прекращается, при атом выдается значение напряжения в цифровом коде до момента изменения и начинается новый цикл преобразования, Таким образом, обеспечивается квазиадаптивный выбор длиельности цикла преобразования в зависимоси от скорости изменения и знака производной входного напряжения. Это увеличивает надежность работы. а

Формула изобретения

Аналого-цифровой преобразователь, содержащий генератор стробимпульсов, выход кс орого соединен с управляющими входами хем сравнения, первые аналоговые входы которых подключены к входной шине цреЬбраэователя, вторые аналоговые входы - к узлам резистивного делителя, один вывод которого подключен к выходу источника эт лонного напряжения, а другой вывод - к об шей шине, первые выходы каждой схемы сравнения через соответствующие алементы И соединены с первыми входами триггеров, а вторые выходы всех схем сравнения, кроме схемы сравнения младшего разряда, подкюпочены к вторым входам элементов И предыдуших разрядов, второй выход схемы срав нения млады его разряда соединен через элемент ИЛИ со вторыми входами тригге525241

Составитель Стом

Редактор К. Каменская ТехредА. ДемьяноваКорректор С. Шекмар

Заказ 5148/565 Тираж 102 9 Подписное

БНИНПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж.-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 ров, второй вход элемента ИЛИ подключен к выходу элемента И младшего разряда и входу инвертора, причем третьи входы всех элементов И, кроме старшего разряда, и второй вход элемента И старшего разряда через линию задержки подключены к выходу генератора стробимпульсов, о т л и— чаю щийс я тем, что, с целью упрощения схемы и повышения надежности преобразователя, в него дополнительно введены аналоговые ключи и резисторы, причем уп8 равляющие входы аналоговых ключей подключены к выходам триггеров, сигнальные входы через соответствующие резисторы— х общей шине, а выходы — к второму входу схемы сравнния младшего разряда.

Источники информации, принятые во внимание при экспертизе изобретения:

1, Авт. св, ¹ 324639, кл. С. 06 ) 3/

/00 от 18.03.68 r.

2. Авт. св. № 369707, кл. Н 03 К

13/185 от 28.12.70 r. (прототип).