Устройство для сопряжения процессора обмена с каналами связи

Иллюстрации

Показать всеРеферат

(61) Дополнительное к авт, свид-ву (22) Заявлено 09.08.74 (21) 2050487/24 (51) М. Кл.а

6 06 т ЗР00 с присоединением заявки № (23) Приоритет

Гааударатааннь.1 иамнтат

Савата Ииниатраа CCCP аа далая изааретаний и аткрь.тий (43) Опубликовано 25 08 76Бюллетень №З1 (45) Дата опубликования описания 19.11,76 (53) УДК 681.326 (088. 8) В.В. Моргунов, И.Н. Смирнов и С.Е. Иванов

/

1

Х (72) Авторы изобретения (71) Заявитель

{54) УСТРОЙСТВО ЗЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА

ОБМЕНА С КАНАЛАМИ СВЯЗИ

Изобретение относится к вычислительной технике и может быть применено при органиэации обмана информацией процессора обмене (аппаратуры первичной обработки информации) с группой дискретных каналов связи, 5 в частности может быть применено на узлах обработки информации или узлах коммутации сообшений в автоматизированных системах управления.

Известно устройство с избирательным уп- и равлением вводом-выводом, включвюшее в себя блоки регистров связи 1.1). Каждая битовая позиция регистра связи может служить для управления подключенного внешнего устройства. Имеется возможность по одйой ко- l5 маиде осушествить адресацию регистра связи с точностью до разряда, байта, полуслова или слова для минимизации процесса подбора вычислителя для устройства ввода-вывода с различными характеристиками. Однако в этом устройстве отсутствует возможность непосредственного управления длиной массива информации, вводимой в процессор или выводимой из процессора в последовательном коде с точностью до бита„ а также с точ,ностью до определенного такта дискретного канала связи. Кроме того, ртсутствует воэможность выдачи команд нв внешние устрой ства с точностью до определенного такта канале связи.

Из известных устройств для сопряжения процессоров обмена с каналами связи наиболее близким к предлагаемому является устр6ф ство..тсодержвщее центральный блок управления, выходы которого цодключенй соответственно к управляющим входам блока связи с каналами,: коммутатора, регистра служебных признаков, а входы - к первому и второму выходам блока связи с каналами, первому выходу регистра служебных признаков и в ходу дешифратора, вход которого соединен с первым выходом счетчика данных и первым входом формирователя адреса оперативной памяти, выход которого подключен к первому выходу устройства, второй вход» »к третьему выходу блока связи с каналами, соединенного информационными входами и выходами и упрввляюшим входом с каналами связи.

Вход и второй выход устройства подключены соответственного к входу и выходу коммута3 < Чi:>, СО(ill!i!i -1 .<<<)ГО <(ВУ><"! ОРО>!><ИЛ!И СВЯ. <ЕМ И

, > i и("тf>< >К1 fifii»ll >х, />()1 ист f )Ом служ(6!и !х

»! !1:!»)!к(1» и с !(."т И<к<>м ц>»!»ьix 21. е !11!<<)ко ..)то g(T f >(. Иств(. Ei< (>бесII(чиPrr)(т

<)< > >л>< >>«»ое ти < )бме!!<> с кп><еiiiaxill <.Вязи, ко= т(>рь!() f>ii(. с lи Al<1 !!я Обл ()н бейтами или Tf)( бу))< у»ряв <е»ия режимами р;!60ты. Кроме

ТОГ О) В -)TOt! >f TPOll(.ÒB(Е)51ИНЯ Инфо!)МЯ!!ИОН<& и! ix меlссие)ОВ 1<0 v0)<(, бе !ть зеленя с то"!—

1»)с I E Н ДО p»3pEIEEE) что HP ВСВГдя jjfE06EIO с т<> !Ки зрения ик дел).не>1!пей программной обработки;; требование HEI обслуживание, вырабатываемое Но окончании обмена зедане<ы) м и(.ивом данных, не вызывает прерывание !

»рограммы процессора, а опрашивается про- 15

Грамм Ой, что увеличивает время реакции ня это требование. В этом устройстве исполь)yE(ETc)я счетчик адреса и счетчик длины информационного массива, что увеличивает объем оборудования устройства. 2О

Цель изобретения — увеличение производительности и повышение коэффициента исИОльзОВаниЯ Оборудования устрОйстВа.

Постигается это благодаря тому, что В устройство введен шифратор адреса абонента, блоки управления поразрядным обменом, управления счетным входом, обмена байтами и обмена служебными сигналами, управлякшие входы которых соединены с соответ< твуюшими выходами центрального блока управления, я его вход подключен к выхс

fIy блоке обмена служебными сигналам)е.

Вход шифратора адреса подключен к третьему выходу блока связи с каналами, выход — к Входу процессора обмена. Блок управле»ия поразряднь!м обменол< соединен двухстг>1)онними связями с регистром данных и блоком связи с каналами и подключен входом к Второму выходу счетчика данных, две входа которого подключены к соответству)<.—

<цим выходам блока управления счетным

Входом. Второй Выход регистра служебны.;. признаков соед11нен с входом блока управления счетным Входом, блоки обмена бяйтямя

45 и >бменя служебныл(и сигналами соединены с каналами связи, блок обмена байтами соо динен двухсторонними связями с регистром данных.

Счетчик данных содержашийся В устр()йу

5О стве, не только подсчитывает число Вводе»ПЫХ KBQHTOB ИпфОРМЕЦИИ, НО И ВЬШОЛНЯЕГ функции счетчике адреса Oliepf

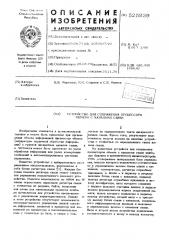

Ня чертеже fEE»I() схеме устройства.

Оня содержит центральный блок 1 упре! ления, блок 2 связи с кан»лами, Вклк>чякший для пример» три модуля Обл <»я 2

1>ЛОК 3 О<)!. (: fiH <))!Уже! >ii! л . и с»Г!<(!) <(<л>!1, ".<>if>Hт01) 4 яд!К c(i або!<Онге, реГистр, > (..i<1>(1 00()ТОЯНИЯ <>Е)()1!ОНТЕ), РЕI EICTf) < > f10»i!k!X, кОммутQT(>f) 7, <)лок 8 уп, " Ei; l(!<ия 1<< >(лi:)---!

)Яднь<м < бм01<ол(, 1>)<ок,) Обме<>я бяi! нъ!х, дешифратор 13, формирователь .) 4 япf cB Опее)етивно<1 ????????????, ??????????)>1 1,">-1 9, 20-20 и моды 21-23, 24, — 24, 2".

25 у<:тре)йстве. В со тев регистре ."> 0)!ОВ<1 состе)я!(ия ябо»(.пт) Входят регистры 6, 10 и счетчик 12 дяннь<х.

Устройство работает следуюше!л1 обрезом.

На входы 2.> — 25 устройстве и далее на входы блока 2 связи с каналал)и при Il( разрядном обмене с каналами связи поступак)т последовательности информационных импульсов, а ня входь< 24,— 24 устрэйст ва — последовательности тактовых импульсов. По каждому тактовому импульсу блок

2 связи с каналами осушествляет запоминание информационного разряда и выдачу требования на обслуживание в центральный блок

1 управления, который, если он не занят обслуживанием других требований, осушестВляет выборку требования на обслуживаиие.

Сигнал выборки с выхода центрального блока 1 управления поступает не вход блоке

2 связи с каналами и последовательно прс ходит через Все модули 2 - 2 блока 2 свя< ь зи с каналами. Нервый же модуль, выдавший требование еа Обмен, блокирует дальнейшее прохождение сигнала выборки и вь— дает В центральный блок управления по цепи обмена служебными сигналами сигнал готовности к работе и адрес абонента со своего выходя.

При получении сигнала готовности к работе центральный блок 1 управления осушестВляет чтение из оперативного зацоминаюшего устройства (ОЗЪ ) слова состояния абонента (ССЛ), которое с входя 21 через коммутатор 7 по сигналу с выходе центрального блока управления, поступяюшему на управляк ший вход коммутатора 7, записывается в регистр 10 служебных признаков и счетчик 12 данны,.. Регистр 10 служебных признаков содержит признак направления обмена, признак управления, признак обмена байтами, KOторые с Выходе регистре служебных признаков поступают не вход центрального блоке

1 управления. Счетчик 12 дынных указывает количествBQ квантов информации (разрядов, байтов), которыми необходимо обменяться с каналом связи по данному ССА.

При поразрядном обмене признаки управления и обмена байтами равны нулю.

Адрес ячейки ОЗУ, из КОТОрОй осу» ествляется чгение ССА, Определяется кодол< не

Вьi ходе форл>ировятеля ) 4 адреса Оперативной памяти, который формирует его в соотE+ tOт НИИ С ап>> Oi > М <.>OHRIITA, ПОС Г Ч1НК:! EIKl на Bxoll форл1нро1:-ателя 14 адрес» (-. в11х<1да блока 2, В у; тпайстве 3а каждым нбене п.ам закрепляется фиксированная область ОЗУ, которая ра;.1бн ь >е l си HB две IIDL> 30HE>1.. ране- 5 с

Н>1Е КОДа НОЛ1Еза ПОДЗОН Ь: OC„ " 1>ЧРСТВ11ЯЕTСR в каждом . Одул» блока 2 связи с к:=паламн.

После чтения CCA центральный опок 1 уп . равления осушествпяет считывание иэ;ЗУ байта данных, который через коммутатор 7 )0 записывается в регистр 6 данных. Адрес байта данных определяется формирователем

14 адреса оперативной памяти в соответствии с адресом абонента, поступаюшим на вход формирователя 14 и стари ими разрядами счетчика 12 данных, поступаюших с выхода последнего на вход формирователя

14 адреса оперативной памяти.

При вводе Йо сигналу, поступаюшему с выхода центрального блока 1 управления на вход блока 8 управления поразрядным обменом, производится запись информационного разряда иэ блока 2 связи с каналами через блок 8 управленияпоразрядным обменом в соответствуюший разряд регистра 6 25 данных. Номер разряда рег.".стра данных определяется значением трех младших разрядов счетчика 12 данных, сигналы с вы: хода которь.х поступа от »а вход блока 8 управления поразрядным обменом. Затем 30 содержимое. регистра 6 данных через коммутатор 7 с выхода 15 устройства записывается в ОЗУ.

В конце цикла обмена с одним иэ модулей блока 2 по сигналу, поступаюшему с выхода центрального блока 1 управления на вход блока 11 управления счетным входом, последний вырабатывает сигнал, который с выхода поступает HB вход счетчика 12 данных и производит вычитание еци- 4О ницы из счетчика данных. Если при этом содержимое счетчика данных становится равным нулю, то дешифратор 13, на вход к<>торого поступает значение счетчика данных. выдает с выхода сигнал, поступаюший на вход центрального блока 1 управления, по которому последний вырабатывает сигнал на одном из выходов. По этому сигналу шифратор 4 адреса абонента выпает с выхода код прерывания, который с выхода 17 устройства поступает в систему прерывания процессора в соответствии с адресом або нента, поступаюшим на вход шифратора 4.

Кроме того, центральный блок 1 управления вырабатывает сигнал изменения номера подзоны, KQTopE>IA по цепи обл PHG управляк1шими сигчаламн поступает в блок 2 связи с каналами. Зате1- производится запись

С;СЛ в ОЗУ через коммутатор 7. 60

Способ «бмена при поразрядном выводе отличается тем, что последовательность тактовых импульсов каналов связи посту паюших на входь1 24, — 24 устройства, осу1нести яет считывание информационных символов, которые с выходов 201 - 20

5 устройства поступают в каналы связи. Крсьме тога, после чтения байта данных по ОЗУ в регистр 6 данных производится пересылка содержимого одного из разрядов регистра 6 данных через блок 8 управления поразрядным обменом, в соответствуюший модуль блока 2. Номер выводимого разряда регистра 6 данных определяется также, как,при поразрядном вводе.

При обмене байтами на входы 24 - 24

3 устройства поступают запросы на ввод или вывод, по которым блок 2 связи с каналами выдает требование на обслуживание в центральный блок 1 управления. После выборки центральным блоком управления данного абонента он осушествляет чтение из

ОЗУ, ССА и байта данных. При этом в регистре 10 служебнь1х признаков признак обмена байтами равен единице, и поэтому по сигналу с выхода центрального блока управления, поступаюшего на вход блока 9 обмена байтами, осушествляется выдача байта с ре--истра б данных через блок 9 обмена байтами и выход 19 устройства в каналы связи. Байт дапн1>1 сопровождается признаком данных, выдаваел1ым в каналы связи из блока 3 обмена служебными сигналами при поступлении на вход последнего сигнала с выхода центрального блока 1 управления.

Кроме того, с вь хода соответствуюшего модуля блока 2 в каналы связи поступает разрешение на обмен. После приема байта данных канал связи выдает об этом сигнал, который с входа 2= устройства через блок

3 обмена служебными сигналами поступает на вход центрального блока 1 управления.

По этому сигналу центральный блок 1 управления закан ивает цикл обмена с данным каналом связи также, как и при поразрядном обмене. Отличие заключается в том, что блок 11 управления счетным входом производит вычитание восьми иэ счетчика 12 данных, посылая сигнал на вход счетчика данных.

При вводе байт данных поступает íà вход блока 9 обмена байтами, а затем в регистр

6 данных, после того как в ответ на тактсм. вый импульс от канала связи блок 2 выдает разрешение на обмен в соответствуюший канал связи.

Управление режимами работы каналов >связи осушествляется в том случае, когда при обслуживании требования от блока 2 из ОЗУ считывается ССД, содержашее признак, пр,паления. В этом случае, йезависимо от то.= о, какими квантами информации производится обмен с данш.м каналом связи„осушествляется выдача байта управления с регистра

6 данных через блок 9 обмен а байтами на выход 19 устройства. При этом через блок

3 обмена служебными сигналами выдается признак управленич,. по которому соответствующий канал связи воспринимает байт дан- И ных в качестве управляюшего и производит

I изменение режима работы (переход с передачи на прием, изменение скорости передачи, отключение и т.п.).

Обмену массивом информации с каналОм свЯзи МОжет предшестВОВать Один байт управления, поэтому после выдачи байта управления признак управления в регистре

10 служебных признаков по сигналу с выхода центрального блока 1 управления, устанавливается в нулевое состояние, а требование на обмен, храняшееся в блоке 2 связи с каналами, не гасится.

В дальнейшем осушествляется обмен дан2Ь ными, описанный выше.

В случае, если во время выборки ребования на обслуживание, выборка по какойлибо причине не,произойдет, сигнал выборки с второго выхода блока 2 связи с каналами поступает на вход центрального блока

1 управления, устанавливая последний в. исходное состояние.

Формула изобретения

Устройство для сопряжения процессора

Обмена с каналами связи, содержашее центральный блок управления, выходы которого подключены соответственно к унравлис шим Входам блока связи с каналами, коммутатора, регистра служебных признаков, а

Входы - к первому и второму выходам блока связи с каналами, первому выходу регистра служебных признаков и выходу дешифратора, вход которого соединен с первым вь?хо?1ом сче? чи1.а дь.;-1ь х 1 ffe;, 11ь.;-. ьх1ии?л" фо змирова Геля ад11ес& опер;- -.-:. Нвной памяти, выход к то12ОГс .1ОЙ??л& )5ен к первому BbfxA-— ду устройств:-.. Итс рой Bxoff — к третьему

B? fXOny бaoKB СВЯЗИ С КаНалаМИ, СОЕДИНЕН

НОГО инфОрма - хко11??ыми Входами и Вь1ходами и управляюшим входом с каналами связи, вход и BTDpoA вь?ход устройства подключены 1-„оответственио к входу и вь ходу коммутатора, соедин.нного двусторонн. ..:Ми связями с регистром дан;ных, регистром служебныхпризнаков и счетчиком данных, о т л и ч а ю ш е е с я тем, что, с целью увеличения производительности и повышения коэффициента использования оборудовния устройства, в него введены шифратор адреса абоне-rra, блоки управления поразрядным обменом, управления счетным входом, обмена байтами и обмена служебными сигналами,. управляюшие входы которых соединены с соответствующими выходами центрального блока управления, вход которого подключен к выходу блока обмена служебными сигналами, вход шифратора адреса подключен к третьему выходу блока связи с каналами, выход - к входу процессора обмена, блок управления поразрядным обменом соединен двусторонними связями с регистром данных и блоком связи с каналами и подключен входом к второму выходу счетчика данных, два входа которого подключены к соответствующим выходам блока управленич счетным входом, второй выход регистра слу. жебных признаков соединен с входом блока управления счетным входом, блоки обмена байтами и обмена служебными сигналами соединены с каналами связи, блок обмена байтами соединен двусторонними связями с регистром данных.

Источники информации, принять.е во внимание при экспертизе:

1. Патент СИА N 3720920, класс

340-172.5 (506 f, 3/OG) 13.03.1973 r.

2 Техническое описание ТЮ1,700.009

Т03, редакция 2-74. Блок сопряжения с каналами связи, стр. 9-96.

Составитель А. Жеренов

Редактор Е. Гончар Техред Г. Родак Корректор Л. Борш:.ская

Заказ 5225/486 Тираж 864 Подписное

111IHHIiH Государственного комитета Совета Минист о.: (. ССI по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Фипиап ППП "Патент", г. Ужгород, ул. Проектная,