Арифметическое устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ЫЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву(22) Заявлено10.08.73 (21) 1952952/24 с присоединением заявки №вЂ” (23) Приоритет(43) Опубликовано25.08.76,Бюллетень № 31 (45) Дата опубликования описания23.12.76

Союз Советских

Социалистических

Республик (») 52595G (51) М. Кл, С 06 У 7/38

Государственный комитет

Соаата Министров СССР по делам изобретений и открытий (53) УДК 681.325. .66 (088.8) (72) Автор изобретения

Ф. Ф. Мингалеев (71) Заявитель (54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах.

Известно устройство, содержащее суммирующий блок и группы элементов И, используемое для сравнения двух двоичных чисел(11, Однако известное устройство не позволяет выполнять арифметические и логические операции.

Известно также арифметическое устройство, содержащее регистры, суммирующий блок, группы элементов И, группу элементов НЕ, элементы И, ИЛИ, группу элементов ИЛИ, выходы которых соединены с входами перво- 15 го регистра, выходы которого соединены с входами второго регистра, прямые выходы которого соединены с первыми входами суммирующего блока, а инверсные выходы соединены с первыми входами первой группы 20 элементов И, вторые входы которой соединены с инверсным выходом знакового разряда второго регистра, а третьи входы соединены с первой тактовой шиной и с входами группы элементов НЕ,выходы которых соединены 25 с первыми входами второй группы элементов И, вторые входы которых соединены с выходами суммирующего блока, выходы элементов первой и второй групп элементов И соединены соответственно с первыми и вторыми входами группы элементов ИЛИ, вторые входы суммирующего блока подключены к выходам третьей группы элементов И первые входы которых соединены с инверсными выходами третьего регистра, а вторые входы соединены с второй тактовой шиной и первым входом элемента ИЛИ (2!.

Однако это известное устройство сложное.

Целью изобретения является упрощение устройства.

Для этого в устройство введен триггер, при этом инверсный выход знакового разряда второго регистра соединен с первым входом элемента И, второй вход которого соединен с первой тактовой шиной, а выход— с входом триггера, прямой выход которого соединен с вторым входом элемента ИЛИ, выход которого соединен со входом переноса в младший разряд суммирующего блока.

525950

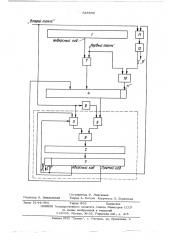

На чертеже приведена структурная электрическая схема устройства.

Арифметическое устройство содержит регистры 1,2 и З,суммирующий блок 4., первую группу элементов И 5, вторую группу элементов И 6, третью группу элементов И7, группу элементов HE 8, группу элементов ИЛИ 9, выходы которых соединены с входами регистра 2, выходы которого соединены с входами регистра 3, прямые выходы 10 которого соединены с первыми входами блока 4, а инверсные выходы соединены с первыми входами группы элементов 5, вторые входы которой соединены с инверсным выхо-дом знакового разряда регистра 3, а третьи 15 входы соединены с тактовой шиной "Второй такт" и с входами группы элементов HE 8, выходы которых соединены с первыми входами группы элементов И 6, вторые входы которых соединены с выходами блока 4, выхо- З ды элементов групп элементов И 5 и И 6 соединены с первыми и вторыми входами группы элементов ИЛИ 9 соответственно вторые входы блока 4 подключены к выходам группы элементов И 7, первые входы которых соединены с инверсными выходами регистра 1, а.вторые входы соединены с тактовой шиной "Первый такт" и первым входом элемента ИЛИ 1 О„

Инверсный выход знакового разряда регистра 3 соединен с первым входом элемента И 1», второй вход которого соединен с тактовой шиной Второй такт", а выход — с входом триггера 12, прямой выход которого соединен с вторым входом элемента ИЛИ 1 О. выход которого соединен с входом переноса в младший разряд блока 4.

Регистры 2 и 3 представляют собойфункционально полный регистр, запись кода на который производится двумя тактирующими импульсами внутри такта.

Группы элементов И 5 и 6, группа элементов ИЛИ 9 совмещаются с входными логиками триггеров регистра 2. 45

Перед сравнением числа, заданные в дополнительном коде, направляются на регистры 1 и 3. Сравнение производится путем вычитания чисел с последующим анализом результата. При выполнении операции может 5О быть два случая:

1. Результат вычитания отрицательный (т.е. знаковый разряд регистра 2 равен "1").

В этом случае результат вычитания сохраняется. 55

2. Результат вьгчитания положительныф (т.е. знаковый разряд регистра 2 равен "О").

Чтобы можно было судить о разности между сравниваемыми числами (разность равна "0" или разность неравна "0") произво- gp дится инвертирование результата с последующим переводом его в дополнительный код.

При этом, если числа равны, то знаковый разряд регистра 2 равен "О", если неравны, то знаковый разряд регистра 2 равен" 1"

По тактам операция "Сравнение" выполняется следующим образом: на первом такте операции — из регистра 1 на суммиоующий блок 4 посылается число в инверсной форме; — в суммирующем блоке 4 производитсясложение двух чисел и единицы дополнения "+1"; — результат сложения запоминается в регистре 3. на втором такте — производится анализ результата, полученного на первом такте; — если знаковый разряд регистра 3 равен "1", содержимое регистра 3 сохраняется; — если знаковый разряд регистра 3 равен "О", содержимое регистра 3 инвертируется. на третьем такте

-содержимое регистра 3 складывается с единицей дополнения "+1 ", если на предыдущем такте оно инвертировалось, либо сохраняется путем сложения с нулем на входе суммирующего блока.

Использование предложенного устройства обеспечивает по сравнению с известнымиследующие преимущества: а) выполнение точного поразрядного сравнения (логического сравнения) двух чисел, используя суммирующий блок арифметического устройства, т.е. без введения элемента сравнения; б) не требуется составления специальной подпрограммы выполнения операции сравнения чисел, т.е. без дополнительных затрат ячеек памяти; в) выполнение арифметических и логических операций.

Формула изобретения

Арифметическое устройство, содержащее регистры, суммирующий блок, группы элементов И, группу элементов НЕ, элементы И, ИЛИ, группу элементов ИЛИ, выходы которых соединены с входами первого регистра,,выходы которого соединены с входами второго регистра, прямые выходы которого соединены с первыми входами суммирующего блока, а инверсные выходы соединены с первыми входами первой группы элементов И, вторые входы которой соединены с инверсным выходом знакового разряда вчю525950 рого регистра, а третьи входы соединены с первой тактовой шиной и с входами группы элементов НЕ, выходы которых соединены с первыми входами второй группы элементов И, вторые входы которих соединены с 5 выходами сумьшрующего блока. выходы элементов первой и второй групп элементов И соединены соответственно с первыми и втооыми входами группы элементов ИЛИ, вторые входы суммирующего блока подключены 10 к выходам третьей группы элементов И, первые входы которых соединены с инверсными выходами третьего регистра, а вторые входы соединечы с второй тактовой шиной и первым входом элемента ИЛИ, о т л и ° ю ш е-е с я тем, что, с целью упрог устройства, в него инверсный выход регистра соеди та И, второй вой тактово триггера, с вторь торог ший нгердинен

ыход коса в млад.нятые во вниельство СССР

i6 F 7/02 1973. ,. и др. "Арифметичес,одействуюших ЭВАМ", М

), с. 249, (прототип). 525950

„дторай такпг"

Составитель Ф. Мингалеев

Техред А. Богдан Корректор Л. Боринская

Редактор А. Зиньковский

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 5 1 44/48 5 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5