Устройство для контроля передачи информации

Иллюстрации

Показать всеРеферат

ОП ИСАЙ ИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (») 525952 (61) Дополнительное к авт свид-ву (22) Заявлено13.03.75.(21)2112694/24 (51) ц. (л о

G 06 F 13/06

G 06 Р;11/00 с присоединением заявки №

Государствеииый комитет

Совета Министров СССР по делов изооретений и открытий (23) Приоритет (43) Опубликовано25.08.76 Бюллетень №31 (53) УДК 681.14 (088,8) °

Особое конструкторское бюро вычислительной техники Рязанского радиотехнического института (71) Заявитель

l (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПЕРЕДАЧИ

ИНФОРМАЦИИ

1

Изобретение относится к области вычислительной техники и может быть использовано для контролями передачик информации, в частности, из внешней памяти накопителя на магнитной ленте (НМЛ) в основную память UBN, Известно устройство, содержашее блат управления, узел анализа кодов и блоки памяти fl).

Наиболее близким техническим решением к предложенному является устройство для контроля передачи информации содержашее блок внешней памяти, блок основной памяти блок управления, триггер сбоя, узел анализа 1 кодов, счетчик прогонов, соединенный двусторонней связью с блоком управления, пеп I вый, второй и третий выходы которого соединены соответственно с первыми входами блока основной памяти, блока внешней памя- 2о ти и нулевым входом триггера сбоя, единичный вход которого соединен с выходом узла анализа кодов, первый и второй входы которого соединены соответственно с четвертым выходом блока управления и первым выходом 5

2 блока основной памяти, второй выход котороrî соединен с выходом устройства 2), Основныл и недостатками этого устройства являются большое количество каналов и weментов, а также необходимость резервирова ния самих источников информации. Помимо этого задача резервирования каждого канала при передаче сообшений от устройства внешней памяти на НМЛ сводится к синхронному и синфазному воспроизведению информации нескольких НМЛ, что в наотояшее врел1я технически не реализуемо, Цель изобретения - повышение надежности устройства для контроля передачи информации.

Для этого в предложенное устройство вве дены узел выдачи прямого и обратного кодов, регистр маски блока основной памяти, узел буферной памяти и узел поразрядного опроса, вход которого соединен с пятым выходом блока управления, а выход - с первым входом узла буферной памяти, второй вход тлторого соединен с шестым выходом блока управления, а выход — с третьим входом узла анализа кодов, выход которого соединен с третьим входом узла буферной памяти и

525952 входом регистра маски блока основной па- формация также поступает в обратном коде, м яти, выход которого соединен со вторым но в узле 6 осушествляется анализ только входом блока основной,па:, яти, третий вход тех разрядов, где произршло совпадение прякоторого соединен с четвертым) входом уз- мых и обратных кодов. Если сумма по модула анализа кодов и выходом узла выдачй лю два цифр прямого кода,храняшвгося в ячейпрямого и обратного кодов, первый и второй ке блока 2 основной памяти, и обратного ко-, входы которого соединены с седьмым выхо да, поступившего в устройство в третьем про. дом блока управления и выходом блока внеш» „o„o равна единице, значение цифры данного

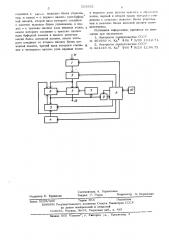

1 ней памяти соответственно. разряда остается без изменения, а в соотНа чертеже представлена структурная р ветствуюших разрядах ячейки узла 3 буферЮ схема устройства для контроля передачи ной памяти эапдсывается1нуль. Если же имеимформац (. ются разряды, в которых сумма по модулю . Устройство содержит,блок 1 внешней два кодов равна нулю, в счетчик 10 прогопамяти, блок 2 основной палы. и, узел 3 нов добавляется единица и осушествляется ! буферной памяти, узел 4 поразрядного оп- )g четвертый прогон носителя блока 1 внешней роса, узел 5 выдачи прямого и обратного памяти. Узел 5 выдачи прямого и обратного кодов, узел 6 анализа кодов, регистр 7 кодов выдает примой код, который в узле 6 маски блока 2 основной памяти, блок 8 уп- анализа кодов суммируется по модулю два равления, триггер 9 сбоя, счетчик 10 про- с кодом, храняшимся в ячейке блока 2 осгонов. Блок 1 внешней памяти имеет вход 20 новной памяти, в тех разрядах, значения ко11 для записи данных. Блок 2 основной Topblx в соответствуюшей ячейке узла 3 бупамяти имеет по выходу 12 связь с число- ферной памяти равны 1. Йля этого из ячейвой магистралью. ки узла 3 буферной памяти в. регистр 7мас-.

На вход 11 блока 1 внешней памяти по- ки блока. основной памяти переписывается

1 ступает информация, регистрируемая на но- 26 код, который <маскирует те разряды, в ко,сителе. Пля передачи информации из блока 1 TopbIx значение кода маски равно нулю. Если внешней памяти в UBM блок 8 управления эта сумма равна нулю, в данный разряд за- выдает в блок 1 внешней памяти команду писывается значение кода, поступившего в чтения, устанавливая!одновременно в нуль четвертом прогоне. В противном случае этот триггер 9,сбоя .и счетчик 10 прогонов, а 30 канал считается неисправным, в узел 5 выдается сигнал разрешения вы- Такое устройство позволяет исправлять дачи прямого кода. случайные ошибки, возникаюшие при передаЛанные с выходов узла 5 записываются чи в каналах, и обнаруживать неисправные в блок 2 основной памяти по адресу, сфор- каналы без резервирования каналов и источмированному блоком 8. После записи всего Зб ников информации, что значительно снижает массива в блок 2 основной памяти снимает- расходы на аппаратурные затраты.ся сигнал разрешения выдачи прямого кода с входа узла 5 в счетчик 10 прогонов добавляется единица, а носитель блока. 1 Формула изобретения внешней памяти переводится к началу мас« сива. При повторном прогоне блок 8 выда- Устройство для контроля передачи инфорет на вход узла 5 сигнал разрешения выдачи, мации, содержашее блок внешней памяти, обратного кода. Обратный код с выходов уз- блокосновнойпамяти,блокуправления,триггер ла 5 поступает в узел 6 анализа кодов. Од сбоя, узел анализакодов,счетчикпрогонов,соеI новременно из ячейки блока 2 основной па- © диненныйдвустороннейсвяэьюсблокомуправмяти, адрес которой соответствует прямому ления, первый, второй и третий выходы которопо коду анализируемого числа, на вход узла 6 соединены, соответственно с первыми входами подается прямой код и производится сумми- блока основной памяти, блока внешней памярование по модулю два. Если во всем мас- ти и нулевым входом триггера сбоя, единичсиве нет ни одного разряда, где совпали бы ный вход которого соединен с выходом узла прямые и обратные коды, информация в бло- анализа кодов, первый и второй входы которс ке 2 основной памяти считается достоверной рого соединены соответственно с четвертым и устройство переходит к передаче следу .выходомблокауправлеиияипервымвыходом шего массива. В противном случае в ячейку блока основнойпамяти, второй выход которого узла 3 буферной памяти, соответствуюшей

55 соединенсвыходомустройства, о т л и.ч аданной ячейке блока 2 основной памяти, за- ю ш е е с я тем, что, с целью повышения писывается код с выходов узла 6, а триг- надежности, в него введены узел выдачи гер 9 сбоя устанавливается в единицу. Одно- прямого и обратного кодов, регистр маски временно в счетчик 10 прогонов добавляемся . блока основной памяти, узел буферной памяединипа и осушествляется третий прогон, Нн- ти, узел поразрядного опроса, вход которого

525952

Составитель А. Горностаев

Техред; Г. Родак Корректор П. Боринская

Редактор Е. Кравцова

Заказ 5225/486 Тираж 864 Подписное .

11НИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4 соединен с пятым выходом блока управления, а выход - с первым входом узла буферной памяти, второй вход которого соедййен с шестым выходом блока управления, а выход — с третьим входом узла анализа кодов, выход которого соединен с третьим входом узла буферной памяти и входом регистра маски блока основной памяти, выход которого соединен со вторым входом блока основной памяти, третий вход которого соеди- 1р нен с четвертым входом узла анализа кодов и выходом узла выдачи пря.. 0I о и обратного кодов, первый и второй входы которого сое:динены с седьмым выходом блока управления и выходом блока внешней памяти соответственно.

Источники информадии, принятые во внимание при экспертизе:

1, Авторское свидетельство СССР

¹ 401989 M. Кл. 606 F 3/00 10.12,71, 2. Авторское свидетельство СССР

Ио 424149 М. Кл, 306 Р 9/20 12.06.72