Счетный триггер

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистимеских

Республик и (11) 52607 8

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 31.05.74(21) 2032724!21 с присоединением заявки № (23) Приоритет (43) Опубликовано25.08.76. Бюллетень ¹ 31 (45) Дата опубликования описания 03.11.76

2 (5Ц М. Кл.

Н 03 E(21/00

Государственный комитет

Совета Министров СССР па делам изобретений и открытий (53) УДК 621.374 (088.8) (72) Авторы изобретения

Б. М. Мансуров и В. И. Горячев (71) Заявитель (54) СЧЕТНЫЙ ТРИГГЕР

Изобретение относится к вычислительной технике и может применяться при разработке интегральных схем для пересчетных и распределительных устройств.

Известные счетные триггеры на МДП— транзисторах, содержащие два симметричных плеча и управление к ним, потребляют большую мощность (1).

Известен также счетный триггер на дополняющих МДП вЂ” транзисторах, содержа- EEE ший два симметричных плеча, выход каждого из которых соединен со входом другого плеча, и четыре управляющих транзистора в каждом плече f2). Такой триггер имеет сложную конструкцию. 15

Uemь изобретения - упростить триггер.

Это достигается тем, что выход каждого плеча соединен с истоком своего первого управляющего тт -транзистора, сток которого подключен к истоку второго управляющего 20 р -транзистора, третий управляющий ть -транзистор и четвертый управляющий р-транзистор включены последовательно, причем затвор третьего управляющего и -транзистора соединен со стоком первого управляющего п — 25 транзистора, исток четвертого управляющего р-транзистора соединен с выходом этого плеча, затворы первого, второго и четвертого управляющих транзисторов обоих плеч объединены и подключены к счетному входу триггера, а исток третьего и сток второго управляющих транзисторов подключены к общей шине.

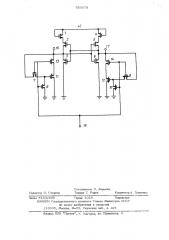

На чертеже приведена схема предлагаемого счетного триггера.

Триггер содержит два симметричных плеча, выполненных на транзисторах 1, 2, 3 и

4, 5, 6, первые управляющие тт -транзисторы 7 и 8, вторые управляющие р-транзисторы 9 и 10, третьи управляющие т -транзисторы 11 и 12 и четвертые управляющие р-транзисторы 13 и 14.

Транзисторы 1-6 соединень по схеме триггера на дополняющих МПП-транзисторах, выход одного плеча триггера соединен с истоком транзистора 7 и истоком транзистора

13, выход другого плеча триггера соединен с истоком транзистора 8 и истоком транзистора 14, транзистор 13 соединен последовательно с транзистором 11, а транзистор 14526078 логическая единица. При поступлении второго счетного импульса триггер переключается в противоположное устойчивое состояние, причем последовательность срабатывания транзисторов правого плеча триггера полностью соответствует рассмотренной последовательности срабатывания транзисторов левого плеча. щ Формула изобретения

Триггер оаботает следуюшим образом.

Допустим, что в исходном состоянии на выходе 16 триггера высокий уровень (логическая единица), на выходе 17 — низкий (логический нуль). При поступлении положи15 тельного импульса на счетный вход 15 триггера транзистор 7 открывается и передает уровень логической единицы на затвор транзистора 11 и заряжает емкость затвора последнего, а транзистор 9 и транзистор 13

20 закрыты уровнем логической единицы на затворе. На другом плече триггера, несмотря на открывание транзистора 8, транзистор 12 не открывается, так как с выхода 17 на загвор гранзисгора 12 поступаег нулевои уровень.

Во время действия счетного импульса это состояние схемы сохраняется без изменения.

После окончания действия счетного импульса закрывается транзистор 7 и открываются транзисторы 9 и 13. Во время разряда емкости затвора транзистора 11 через транзистор 9 создается такое положение, когда одновременно открыты транзистор 1 3 и транзистор 11. При этом на выходе 16 формируется нулевой уровень, который через обратную связь формирует на выходе 1 7 высокий уровень, который через обратную связь обеспечивает $opvирование нулевого уровня .на выходе 16, т. с. триггер переключается в устойчивое состояние, при котором на выходе 16 — логический нуль, а на выходе 1 7— лине, Источники информации, принятые во внимание при экспертизе:

1. Патент Англии % 1 341 156, НЗТ, 19.12,73.

2. Валиев К. А. и др. цифровые интегральнь е схемы на МДП-транзисторах, 1 97 1, с, 275, рис. 7.19 (прототип). последовательно с транзистором 12, сток транзистора 7 соединен с затвором транзистора 11 и истоком транзистора 9, сток транзистора Р— с затвором транзистора 1 2

HcToEoivl транзисто L 0> oToic!i транзис i opoB

9, 10 и истоки транзисторов 11, 12 подключень: к обшей шине, а затворы транзисторов 7-10, 13 и 14 объединены и подключены к счетному входу 1 5 триггера, Счетный триггер на дополняюших МДПтранзисторах, содержащий два симметричных плеча, выход каждого из которых соединен со входом другого плеча, и четыре управляющих транзистора в каждом плече, о т л ич а ю ш и и с я тем, что, с целью упрошения устройства, выход каждого плеча соединен с истоком своего первого управляющего г -транзистора, сток которого подключен к истоку второго управляюшего -транзистора, третий управляюший -транзистор и четвертый управляюший р-транзистор включены. последовательно, причем затвор третьего управляющего т -транзистора соединен со стоком первого управляюшего г -транзистора, исток четвертого управляюшего р-транзистора соединен с выходом этого же плеча, затворы первого, второго и четвертого управляющих транзисторов обоих плеч объединены и подключены к счетному входу триггера, а исток третьего и сток второго управ ляюших транзисторов подключены к общей

526078

Составитель Л. Дарьина

Техред Г, Родак Корректор А. Гриценко

Редактор О. Стенина

Филиал ППП "Патент, г. ужу ород, ул. Проектная, 4

Заказ 5143/490 Тираж 1 02 9 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5