Пороговое устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН И Я

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (i I1 526855

Союз Советских

Социалистических

Республик (61) Дополнительно к гi3т, свкд-I3) (22) Заявлено 29.03.74 (21) 2009693 21 с присоединением заявки М (23) Приоритет

Опубликовано 30.08.76. Бюллетень X- 32

Дата опубликования описания 08.09.76 (5)) Ч, Кл,- зG 05В 1/01

Н ОЗК 5/20

Государственнык комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.374 33 (088.8) (72) Лвтор изобретения

А. И. Епифанов!

Специализированное конструкторско-техкологичесйре .форо строительной техники связи J l (71) Заявитель (54) ПОРОГОВОЕ УСТРОЙСТВО

Изобретение относится к области импульсной техники и может быть использовано, в частности, для контроля сопротивления изоляции проводов, номинального значения высокоомных резисторов и сопротивления изоляции конденсаторов.

Известно пороговое устройство с запоминанием достигнутого порогового уровня, однако око не обладает высоким входным сопротивлением и повышенной перегрузочной способностью (1).

Известно также пороговое устройство, собранное на основе транзисторного эквивалента двухбазового диода с резистивным делителем напряжения в цепи базы его входного транзистора (2).

Однако в этом пороговом у.стройстве его входное сопротивление резко уменьшается, когда значение входного напряжения приближается к напряжению срабатывания порогового устройства.

Кроме того, известное пороговое устройство после срабатывания потребляет значительный ток от источника входного напряжения и возвращается в исходное состояние при отключении входного напряжения, а для запоминания достигнутого состояния требует дополнительных запоминающих схем.

Цель изобретения — расширение диапазона контролируемых напряжений от источников любой мощности с фиксацией достигнутого уровня.

Для достижения цели в пороговое устройство, содержащее транзисторный эквивалент

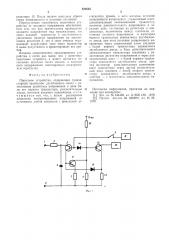

5 двухбазового диода с резисторкым делителем напряжения в цепи базы его первого тракз»сторг, разделительные диоды, источник входного напряжения, введены источкик запирающего напряжения, управляемый ключ, допол10 нительный запоминающий транзистор, источник дополнительного напряжения и зарядная цепь, состоящая из резистора и конденсатора, включенная между клеммами источника входного напряжения и эмиттером первого тран15 зистора эквпвалентг двухбазового диода, при этом источник запирающего напряжения через управляемый ключ соединен с ба-,îé первого транзистора эквивалента двухоазового диода, а база дополнительного запоминаю20 щего транзистора соединена с резистивным делителем напряжения и через разделительныйый диод с базой первого транзистора эквивалента двухбазового диода, причем ко I. лектор дополнительного запоминающего тран25 зистора через другой разделительный диод соединен с базой второго транзистора эквивалента двухбазового диода, а эмиттер — с источником дополнительного напряжения, На фиг. 1 представлена принциппа,-ькая

30 схема порогового устройства; на фиг, 2 при526855 ведена вольтамперная характеристика перехода эмиттер — база входного транзистора эквивалента двухб".зового диода.

Входной сигнал (см. фиг. 1) подается на клеммы 1, 2, к которым подсоединена зарядIIBH цепь, состоящая из Высокоомного резистора 3 и конденсатора 4. К точке соединения резистора 3 и кондеиcaTopa подключается эмиттер входного транзистора 5 эквивалента двухбазового диода, с коллектором которого соединена база другого транзистора 6 эквивалента двухбазового диода с эмиттерным резистором 7.

На базу транзистора 5 от источника 8 запиршощего напряжения через управляющий ключ 9 подается напряжение, превышающее пороговое напряжение. определяемое резистивным делителем 10, 11 напряжения. К точке соединения резисторов 10, 11 подключена база запоминающего транзистора 12 с

«оллекторной нагрузкой 13.

База запоминающего транзистора 12 через разделительный диод 14 соединена с базой входного транзистора 5, а коллектор запоминающего транзистора 12 через разделительный диод 15 соединен с базой транзистора 6.

На эмиттер запоминающего транзистора 12 от источника 16 дополнительного напряжения подано запирающее напряжение.

Для пояснения работы схемы рассмотрим вольтамперную характеристику перехода эмиттер — база входного транзистора 5 и зависимость сопротивления перехода от приложенного к нему напряжения, приведенного на фиг. 2, где U — напряжение, определяемое резистивным делителем 10,11;

I,ð — ток через входной транзистор, при котором сработает пороговое устройство;

U,ð — входное напряжение, при котором сработает пороговое устройство;

R-„; — сопротивление перехода эмиттер— база в момент срабатывания порогового устройства;

U „— запирающее напряжение, приложенное к базе входного транзи "тора от источника 8.

Из графика видно, что при напряжении сраоатывания сопротивление R,I; невелико.

Для увеличения входного сопротивления порогового устройства последовательно с сопротивлением перехода эмиттер — база транзистора 5 включен высокоомный резистор 3, в результате чего ток от источника входного напряжения не может достигнуть значения тока срабатывания 1,р порогового устройства.

С целью накопления энергии включен конденсатор 4, разрядный ток которого через входной транзистор 5 достигает значения тока срабатывания I,ð, когда напряжение на нем достигнет напряжения срабатывания U„„.

Сопротивление перехода эмиттер — база транзистора 5 нелинейно и резко уменьшается по мере заряда конденсатора 4, тем самым шунтируя его. В результате этого напряжение

Зб

65 на конденсаторе 4 ие может достигнуть напряжения сраоатывания порогового устройства, Для обеспечения заряда конденсатора 4 до напряжения срабатывания порогового устройства к базе транзистора 5 подводится запирающее напряжение от источника 8 запира ощего напряжения, чтооы предотвратить приоткрывание транзистора 5 по мере заряда конденсатора 4.

Таким образом, подключение запирающего напряжения к базе входного транзистора смещает вольта мперную характеристику перехода эмиттер — база на величину разности запирающего напряжения и напряжения делителя U,„„— Г,, что обеспечивает увеличение сопротивления перехода эмиттер — база при входном напряжении, равном U,ð (см. график пунктиром) . При достижении напряжения срабатывания порогового устройства на конденсаторе 4 и при отключении запирающего напряжения транзистор 5 открывается, сопротивление его перехода эмиттер — база уменьшается, за счет чего обеспечивается ток разряда конденсатора 4, достаточный для срабатывания порогового устройства.

Пороговое устройство работает следующим образом.

При отсутствии входного сигнала транзисторы 5 и 6 закрыты, закрыт также и запоминающий транзистор 12 за счет подачи запирающего напряжения от источника 16 дополнительного напряжения. Управляемый ключ 9 замкнут, в результате чего на базу входного транзистора 5 прикладывается запирающее напряжение, равное напряжению срабатывания порогового устройства. Для того, чтобы запирающее напряжение от источника 8 не влияло на напряжение на резисторе 11, включен раздел ит ел ь н ы и диод 14.

При появлении входного сигнала конденсатор 4 заряжается через высокоомный резистор 3.

Для контроля величины напряжения на конденсаторе 4 ключ 9 периодически размыкается с определенной частотой. Если в момент размыкания управляемого ключа 9 напряжение на конденсаторе 4 достигнет напряжения срабатывания порогового устройства, транзисторы 5 и 6 открываются за счет разрядного тока конденсатора 4. Напряжение на коллекторе транзистора 6 и базе транзистора

12 уменьшается, в результате чего потенциал на базе транзистора 12 становится положительным по отношению к потенциалу его эмиттера и транзистор 12 открывается. Напряжение на коллекторной нагрузке 13 увеличивается и через разделительный диод 15 поддерживает в открытом состоянии транзистор 6.

Таким образом, транзисторы 6 и 12 остаются в открытом состоянии до момента подачи импульса сброса на базу любого транзистора.

Сигнал информации о срабатывании порогового устройства снимается с резистора 7 или

526855 резистора 13. После подачи импульса сброса схема возвращается в исходное состояние.

Перегрузочная способность порогового устройства от входного напряжения обеспечивается тем, что при значительном превышении входного напря>кения над номинальным, ток через входной транзистор 5 увеличивается, увеличивая падение напряжения на высокоомном резисторе 3, что в свою очередь ограничивает возрастание тока через транзистор

5 выше допустимого и предотвращает его пробой.

Входное сопротивление предложенного устройства в сотни раз выше, чем у известных пороговых устройств, и может достигать нескольких десятков тысяч мегаом, а входные цепи выдерживают многократную электрическую перегрузку.

Формула изобретения

Пороговое устройство, содержащее транзисторный эквивалент двухбазового диода с резистивным делителем напряжения в цепи базы его первого транзистора, разделительные диоды, источник входного напряжения, отл ич а ю щ е е с я тем, что, с целью расширения диапазона контролируемых напряжений от источников любой мощности с фиксацией достигнутого уровня, в него введены источник запирающего напря>кения, управляемый ключ, дополнительный запоминающий транзистор, источник дополнительного за5 рядная цепь, состоящая из резистора и конденсатора, включенная между клеммами источника входного напряжения и эмиттером первого транзистора эквивалента двухбазового диода, при этом источник запирающего на1О пряжения через управляемый ключ соединен с базой первого транзистора эквивалента двухбазового диода, а база дополнительного запоминающего транзистора соединена с резистивным делителем напряжения и через раз15 делительный диод — с базой первого транзистора эквивалента двухбазового диода, причем коллектор дополнительного запоминающего транзистора через другой разделительный диод соединен с базой второго транзи20 стора эквивалента двухбазового диода, а эмиттер — с источником дополнительного напряжения.

25 Источники информации, принятые во внимание при экспертизе: (1). Лвт. св. № 344405, кл. G 05В 1/01, 1970. (2). Патент Англии № 1202091, кл. Н ЗТ, 1970.

526855

Составитель Лякишев

Редактор А. Купрякова Техред В. Рыбакова Корректор И. Позняковская

Заказ 1954/1 Изд, Кв 1576 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2