Процессор

Иллюстрации

Показать всеРеферат

и 526902

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 28.10.74 (21) 2071459/24 с присоединением заявки № (23) Приоритет

Опубликовано 30.08.76. Бюллетень ¹ 32

Дата опубликования описания 04.11.76 (51) М. Кл."- G 06F 15/06

Государственны и комитет

Совета Министров СССР ао делам изобретений и открытий (53) УДК 681.3(088.8) (72) Авторы изобретения

Ю. Е. Чичерин, В. С. Кокорин, В. В. Смирнов, Б. В. Шевкопляс, Э. П. Овсянникова-Панченко, Л. М. Петрова и Э. И. Плетнер (71) Заявитель (54) ПРОЦЕССОР

Изобретение относится к цифровой вычислительной технике, в частности к процессорам с микропрограммным управлением.

Известен процессор, содержащий блок микропрограммного управления и блок отработки команд, образующие замкнутую систему, в которой блок микропрограммного управления выполняет, в частности, функции изменения направления внутри микропрограммы и перехода к двум микропрограммам. Однако возможности ветвления от одной микрокоманды в таком процессоре ограничены, что приводит к снижению быстродействия и усложнению оборудования.

Известен также процессор, содержащий последовательно соединенные память микрокоманд, регистр микрокоманд и блок формирования микроопераций, арифметико-логическое устройство, соединенное с входами триггера переполнения, триггера расширения и условия, два регистра операндов, соединенные с арифметико-логическим устройством, регистр адреса памяти микрокоманд, блок регистров общего назначения, выходной регистр оперативной памяти и межрегистровую магистраль, соединенную с арифметико-логическим устройством, регистрации операндов, регистром адреса памяти микрокоманд, блоком регистров общего назначения и выходным регистром оперативной памяти.

Недостатком известного процессора является снижение быстродействия при работе с переменной системой команд и при эмуляции.

Цель изобретения — повышение быстродей5 ствия при работе с переменной системой команд и при эмуляции.

Это достигается тем, что в предлагаемый процессор введены два триггера эмуляции, два триггера ветвления и триггерная магист10 раль, причем триггерная магистраль соединена с триггерами эмуляции, ветвления, переполнения, расширения и условия, выходы двух соседних разрядов выходного регистра оперативной памяти подключены к входам соответствующих триггеров эмуляции. Входы первого и второго триггеров эмуляции соединены соответственно с шинами старших и младших разрядов межрегистровой магистрали.

Выходы триггера условия и одного из триг2о геров ветвления подключены к входам арифметико-логического устройства.

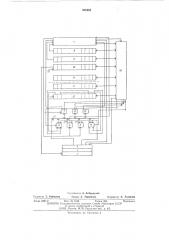

На чертеже представлена блок-схема процессора.

Процессор содержит память 1 микрокоманд

25 с регистром 2 микрокоманды, подключенным к входу блока 3 формирования микроопераций, арифметико-логическое устройство 4, соединенное с триггером 5 переполнения, триггером 6 расширения и триггером 7 услозо вия, регистр 8 первого операнда, регистр 9

526902

3 второго операнда, регистр 10 адреса памяти 1 микрокоманд, регистры 11 общего и специального назначений, выходной регистр 12 оперативной памяти, первый триггер 13 эмуляции, второй триггер 14 эмуляции, первый триггер 15 ветвления, второй триггер 16 ветвления, одноразрядную магистраль 17 обмена информацией между триггерами 5 — 7, 13 — 16 и поразрядные магистрали 18 обмена информацией между регистрами 8 — 12 и арифметикологическим устройством 4.

Выходы регистров 8 и 9 соединены с входами арифметико-логического устройства 4.

Выходы арифметико-логического устройства подключены к поразрядным магистралям 18 и к входам триггеров 5, 6 и 7. Выходы регистра

10 подключены к адресным входам памяти 1 микрокоманд. Выходы блока 3 формирования микроопераций подключены к магистралям 17, 18, к триггерам 5, 6, 13, 14 и к арифметикологическому устройству 4. Выходы любых двух соседних разрядов регистра 12 подключены к входам триггеров 13 и 14, выходы триггеров 13 и 14 — к магистрали 17. Триггеры 5 и 6 соединены двунаправленными линиями связи 19 с магистралью 17. Выход триггера 6 соединен с входом арифметико-логического устройства 4.

Вход триггера 13 подключен к магистрали

18 старших разрядов, .вход триггера 14 — к магистрали 18 младших разрядов, входы триггеров 7, 15 и 16 — к магистрали 17. Выходы триггеров 7, 15 и 16 подключены к трем различным магистралям 18 младших разрядов; кроме того, выходы триггеров 7 и 15 соединены с входами арифметико-логического устройства 4. Регистр 10 имеет внешние информационные входы 20, регистр 12 — входы 21.

Процессор работает следующим образом.

Каждой команде программы соответствует фиксированный начальный адрес микропрограммы, реализующей данную команду.

Команда, выбираемая из оперативной памяти, поступает на входы 21 регистра 12 и заносится в этот регистр. Выборка, так же как и исполнение команды, осуществляется под микропрограммным управлением. Сформированный начальный адрес микропрограммы (блок формирования начального адреса на чертеже не показан) поступает, как обычно, на вход 20 регистра 10 адреса памяти 1 микрокоманд, а выбранная микрокоманда — в регистр 2 микрокоманды. Дальнейшая работа процессора определяется содержимым регистра микрокоманды и кодом выполняемой команды. Блок

3 формирования микроопераций вырабатывает управляющие сигналы, определяющие все пересылки и операции в процессоре.

Микрокоманда имеет фиксированный формат и разбита на ряд полей: поле константы, поле микроопераций ветвления, поле микроопераций регистровых пересылок, после микроопераций арифметико-логического устройства, поле микроопераций триггерных пересылок, поле адреса следующей микрокоманды. Разде5

ЗО

4 ление полей обеспечивает параллелизм в работе процессора.

Эффективность использования предлагаемого процессора показана на приведенных ниже примерах выполнения наиболее часто встречающихся процедур: ветвления при формировании адреса операнда, ветвления при расширении системы команд, арифметических сдвигов, анализа групп разрядов и деления.

Рассмотрим процедуру ветвления при формировании адреса операнда. Признаки для формирования адреса операнда задаются двумя разрядами команды: признаком косвенной адресации и признаком модификации. После выборки команды на выходной регистр 12 оперативной памяти эти разряды с помощью микроопераций триггерных пересылок переписываются в триггеры 13 и 14 эмуляции и далее через магистраль 17 — в триггеры 15 и 16, Триггер 7 в это время устанавливается в нуль, Следующей микрокомандой выполняется ветвление посредством выдачи константы с нулевыми значениями двух младших разрядов в магистрали 18 процессора из поля константы микрокоманды и выдачи содержимого триггеров 7,15 и 16 в три магистрали 18 младших разрядов. После приема дизъюнктивной информации с магистралей 18 в регистр 10 адреса памяти микрокоманд в этой же микрокоманде выполняется микрооперация перехода. Следующая микрокоманда, выбираемая из памяти 1 микрокоманд, по сформированному в регистре 10 адресу определяет всю последовательность действий по формированию адреса операнда.

Расширение системы команд обычно осуществляется за счет использования определенных разрядов команды в качестве дополнения к основному коду операции. Предлагаемый процессор обеспечивает эффективное выполнение таких команд. Действительно, дополнительные разряды команды с регистра 12 переписываются в триггеры 13 и 14 с помощью микроопераций триггерных пересылок и далее через магистраль 17 — в триггеры 7, 15 и 16. Если число дополнительных разрядов кода операции превышает три, то оставшиеся разряды могут быть аналогично использованы на следующих этапах ветвления (подобно многоступенчатой дешифрации). Процедура ветвления осуществляется способом, аналогичным описанному в предыдущем примере. В зависимости от информации в триггерах 7, 15 и 16 на каждом этапе ветвления может быть выбрана одна из двух, четырех или восьми возможных ячеек памяти 1 микрокоманд.

Рассмотрим операцию арифметического сдвига, которая заключается в сдвиге влево или вправо всех разрядов числа, кроме знакового. Обычно для этой цели используется специальная микрооперация и дополнительные вентили в схеме сдвига. В рассматриваемом процессоре арифметический сдвиг осуществляется следующим образом.

526902

Сдвигаемое число из одного из регистров

9 — 12 переписывается в регистр 8. Одновременно с этим знаковый разряд числа принимается с магистрали 18, соответствующей зна. ковому разряду, в триггер 13 эмуляции и переписывается в триггер 7 условия.

Число из регистра 8 сдвигается вместе со знаковым разрядом с помощью комбинационной схемы арифметико-логического устройстава 4. Содержимое триггера 7 условия передается в арифметико-логическое устройство и через него — в .магистраль 18 знаковых разрядов. Разряды сдвинутого числа, кроме знакового, также выдаются в соответствующие магистрали 18. После приема в требуемый регистр процессора получается арифметически сдвинутое число.

В предлагаемом процессоре можно выполнять операции цилиндрических сдвигов без использования дополнительных вентилей в арифметико-логическом устройстве. Действительно, знаковый и младший разряды через магистрали 18 передаются в триггеры 13 и 14, затем переписываются соответственно в триггеры 15 и 7 и один из них .в зависимости от направления сдвига выдается в арифметикологическое устройство для последующей передачи в соответствующую магистраль. В это время число, принятое в регистр 8, логически сдвигается арифметико-логическим устройством в требуемую сторону и затем также выдается в магистрали 18. Циклически сдвинутый код, выдаваемый в магистрали 18, принимается в один из регистров процессора.

Важное значение при обработке сообщений, например, в случае использования процессора в центрах коммутации сообщений, имеет возможность анализа групп разрядов слова.

Обычно применяемый последовательный способ выделения и проверки разрядов занимает много времени, поскольку требует нескольких последовательных шагов работы процессора.

В предлагаемом процессоре выделение групп разрядов выполняется с помощью микроопераций занесения в триггеры эмуляции 13 и 14 произвольных пар разрядов выходного регистра 12 оперативной памяти и переписи их через магистраль 17 в необходимом сочетании в триггеры 7, 15 и 1б с последующей выдачей в магистрали 18, а проверка — с помощью ветвления посредством занесения значений триггеров 7, 15 и 1б и константы в регистр 10 адреса памяти микрокоманд и выполнения перехода.

Рассмотрим выполнение операции деления.

Поскольку в микропрограммном процессоре наиболее приемлемым способом ее реализации является микропрограмма, то время ее выполнения существенно зависит от эффективности огранизацпп ветвления. Типовой ча. I ÷o алгорп ем а делен;<я является проверка знаков значения делимого и делителя и последующее выполнение прибавления прямого или инверсного кода делителя к текущему значению делимого. В данном процессоре этот алгоритм реализуется следующим образом.

Перед началом деления знак делителя заносится в один пз триггерог ветвления, например в триггер 15, а знак текущсго значения делимого — по уже рассмотренной цепи: чрпем в триггер 13 эмуляции из знаковой магистрали 18 процессора, перепись из триггера

13 эмуляции через магистраль 17 в триггер 7 условия. Последующее ветвление по значению двух младших разрядов адреса микропрограммы, соответствующих знаком делителя и текущего значения делимого, позволяет сразу выйти на требуемый участок микропрограммы.

Использование предлагаемого процессора при работе с переменной системой команд и при эмуляции позволяет повысить быстродействие вычислительных систем на 20 — 30 /О.

Формула изобретения

Процессор, содержащий последовательно соединенные память мпкрокоманд, регистр микрокоманд и блок формирования мпкроопераций, арифметпко-логическое устройство, соединенное с входами триггера переполнения, триггера расширения и условия, два регистра операндов, соединенные с арифметпко-логическим устройством, регистр адреса памяти микрокоманд, блок регистров общего назначения, выходной регистр оперативной памяти и межрегистровую магистраль, соединенную с арифметико-логическим устройством, регистрами операндов, регистром адреса памяти микрокоманд, блоком регистров общего назначения и выходным регистром оперативной памяти, отличающийся тем, что, с целью повышения быстродействия при работе с переменной системой команд и прп эмуляции, в него введены два триггера эмуляции, два триггера ветвления и триггерная магистраль, причем триггерная магистраль соединена с триггерами эмуляции, вствленпя, переполнения, расширения и условия, выходы двух соседних разрядов выходного регистра оперативной памяти подключены к входам соответствующих триггеров эмуляции, входы первого и второго триггеров эмуляции соединены соответственно с шинами старших и младших разрядов межрегистровой магистрали, выходы триггера условия и одного из триггеров ветвления подключены к входам арифметико-логического устройства.

526902

Составитель А. Амбрацумян

Техред 3. Тараненко Корректор А. Галахова

Редактор T. Рыбалова

Типография, пр. Сапунова, 2

Заказ 226!/2 Изд. М 1646 Тираж 864 Подписное

Ц1-1ИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, К-35, Раушская наб., д. 4/5