Ассоциативный запоминающий элемент на моп транзисторах

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ 527т40

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДПВЛЬСТВУ (61) Дополнительное к авт, свид-ву (22) Заявлено 23.10.74 (21) 2070463/24 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано 05.09.76 Бюллетень № ЗЗ (4б) Дата опубликования описания 08.07.77 (51) М. Кл о G 11 С 11/40

G 11 С 15/04

Государственный комитет

Совета Министров СССР по делам ивооретений и открытий (53) УДК 681.327.66 (088.8) (72) Авторы изобретения

Н. А. Зосимова и P. В. Чабуркина (71) Заявитель

АС СОЦИАТИВНЫЙ ЗАПОМИНАИИцИЙ ЭЛЕМЕНТ НА

МОП вЂ” ТРАНЗИСТОРАХ

Изобретение относится к области вычислительной техники и может быть использовано при построении ассоциативных запоминающих устройств.

Известен ассоциативный запоминающий элемент на МОП вЂ” транзисторах, содержащий

МОП вЂ” транзисторы, соединенные с разрядными, словарными и индикационными шинами (1) .

Элемент довольно сложный по конструкции.

Наиболее близким к изобретению является ассоциативный запоминающий элемент, содержащий транзисторы записи, затворы которых подключены к адресной шине, истоки — к затворам транзисторов сравнения, истоки которых подключены к разрядным шинам (2).

Недэстаток этого ассоциативного запоминающего элемента заключается в том, что для индикации признака и выбора элемента используются две шины, и кроме того, возможно разрушение информации при считывании.

Цель изобретения состоит в упрощении ассоциативного запоминающего элемента и повышении надежности его в работе.

Это достигается тем, по в элемент введены дополнительные транзисторы, затворы которых подключены к шине питания, стоки — к разрядным шинам, истоки — к стокам транзисторов записи, истоки транзисторов сравнения подключены к разрядным шинам, стоки — к адресной шине.

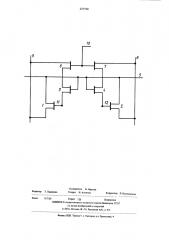

5 На чертеже изображена принципиальная схема предлагаемого ассоциативного запоминающего элемента, где:

1,2 — транзисторы сравнения;

3,4 — транзисторы записи, 10 5 — адре сная шина;

6,7 — дополнительные транзисторы режима;

8,9 — разрядные шины;

10 — шины питания;

11, 12 — узловые емкости.

15 Запоминающий элемент работает в режима: хранения, записи, считывания и сравнения.

Информация хранится в форме зарядов на узловых емкостях 11 и 12. В режиме хранения разрядные 8, 9 и адресные 5 шины находятся на

20 уровне логического "0", обеспечивая закрьпое состояние транзисторов 1, 2, 3, 4. В результате цепи перезаряда емкостей 11 и 12 находятся в разомкнутом состоянии.

Выборка элемента осуществляется подачей ло26 гического уровня "1" на адресную шину 5, что

527740

l0 приводит к отпиранию транзисторов 3 и 4, позволяющих осуществить запись информации.

Заряды емкостей изменяются при записи, если хранящаяся в них информация противоположна записываемой, что достигается путем подключения затворов транзисторов 3, 4 к выбранной адресной шине 5, а затворов транзисторов 6, 7 — к шине питания 10, находящейся при записи на уровне логической "l", по приводит к отпиранию этих транзисторов. При этом записываемая информация в парафазной форме подается на разрядные шины 8, 9 и через открытые транзисторы 3, 4, 6, 7 поступает на узловые емкости 11 и 12 запоминающего элемента.

При считывании ток течет из выбранной адрес ной шины 5 через открытый транзистор 1 или 2, в зависимости от заряда емкостей 11 и 12, в одну из разрядных шин 8, 9, находящихся на уровне логического "0, фиксируя на выходе состояние элемента.

Дополнительные транзисторы 6, 7 при считывании и сравнении заперты путем подачи уровня логического "0" на шину питания 10, что исключает возможность разрушения информации в этих режимах.

В режимах сравнения внешняя информация подается парафазно обратным кодом на разрядные шины 8, 9 так, что в случае несовпадения хранящейся на емкости и прямого кода внешней информации из соответствующей р;зрядной шины 8 или 9 через один из транзисторов 1 или 2 потечет ток в адресную шину 5, находящуюся при сравнении на уровне логического "0 ;.

Состояние маскирования при сравненИи получается, когда на обе разрядные шины 8 и 9 подается уровень логического "0",. В результате транзисторы 1, 2 будут отключены и независимо от состояния емкостей 11 и 12 ток в адресной шине не появится, что указывает на совпадение прямого кода внешней и хранящейся в данном элементе информации.

Применение предложенного элемента в ассоциативных запоминающих устройствах позволяет повысить надежность их в работе.

Формула изобретения

Ассоциативный запоминающий элемент на

МОП вЂ” транзисторах, содержащий транзисторы записи, затворы которых подключены к адресной шине, истоки — к затворам транзисторов сравнения, истоки которых подключены к разрядным шинам, отлича ющий ся тем, что, с целью упрощения конструкции и повышения надежности в работе, в него введены дополнительные транзисторы, затворы которых подключены к шине питания, стоки— к разрядным шинам, истоки — к стокам транзисторов записи, истоки транзисторов сравнения подключены к разрядным шинам, стоки — к адресной шине.

Источники информации, принятые во внимание при экспертизе:

1. Патент США Р 3609710 кл. 340 — 173, 1971 r, 2. Авторское свидетельство Р 408374, кл G 11

С 15/00, 1971 г.

527740

917/36 Тираж 720 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Составитель В. Фролов

Редактор Т. Каранова Техред И. Асталош Корректор Л. Веселовская