Формирователь импульсов малой длительности по переднему и заднему фронту входного импульса

Иллюстрации

Показать всеРеферат

с ° лю-, 1; .а|оН с Но библ и о;".;;, с, ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСИОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11) 5 7817 (о1) Дополнительное к авт. свид-ву 373864 (22) Заявлено 21.03.75 (21) 2115344/21 с присоединением заявки № (23) Приоритет (43) Опубликовано05.09.76,Бюллетень № 33 (45) Дата опубликования описания 19.05.77 (51) М. Кл.

Н 03 К 5/01

Гасударственный комитет

Совета Министров СС".р по делам иэаоретений и открытий (53) УДК 621.374. .387 (088,8) (72) Авторы изобретения

А. Л. Гуртовцев и А. Ф, Петренко

Институт электроники и вычислительной техники

АН Латвийской ССР (71) Заявитель (54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ МАЛОЙ

ДЛИТЕЛЬНОСТИ ПО ПЕРЕДНЕМ У И ЗАДНЕМ У

ФРОНТАМ ВХОДНОГО ИМПУЛЬСА

Изобретение относится к радиотехнике, может быть использовано в устройствах автоматики и вычислительной техники.

Известен формирователь импульсов малой длительности по переднему и заднему фронтам входного имп,льса по авт.св. ¹ 373864.

Е(ель изобретения — регулирование длительности выходного импульса формирователя.

В предлагаемый формирователь введены щ источник синхронизируюших импульсов и дополнительный логический элемент, один из входов которого соединен с выходом источника синхронизируюших импульсов и с устаHoBo÷íûì входом RS — триггера, второй и 1н третий входы дополнительного логического элемента подключены к выходам основных логических элементов, третьи входы которых соединены с выходом дополнительного логического элемента. 20

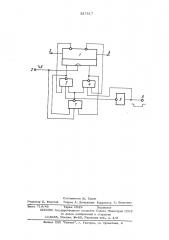

На чертеже приведена схема формирователя, Динамический синхронизируюший вход

RB триггера 1 подключен ко входу синхронизации 2. Инверсные выходы триггера 25 через логические элементы 3 и 4 соедине ны соответственно с его R и Я входами.

Выходы триггера подключены к выходам 5 и 6 формирователя, Один из входов логического элемента 7 соединен сс входом синхронизации 2 и с установочным входом триггера 1. Второй и третий входы элемента 7 поключены к выходам логических элементов 3 и 4, третьи зходы которых соединены с выходом логического элемента 7.

Управляющий вход 8 соединен с одним из входов логического элемента 4. непосредственно, а через инвертор 9-с одним из входов логического элемента 3.

Формиватель импульсов малой длительности по переднему и заднему фронтам входного импульса работает следующим образом.

Пусть в исходном состоянии триггер 1 находится в нуле, т.е. на его прямом выходе присутствует низкий уровень, а на инверсном — высокий. Пусть на входе синхрс низации 2 присутствует высокий уровень паузы, а на управляющем входе 8 — высокий уровень управляющего сигнала. Тогда выход

527817 элемента 7 удерживается на низ .ом уровне.

Высокий уровень инверсного выхода триггера 1 удерживает на низком уровне выход логического элемента 3, а высокий уровень управляющего сигнала - на низком уровне выход элемента 4. С появлением на входе

2 импульса синхронизации низкого уровня состояние триггера 1 не изменяется, так как на его входах присутствуют низкие уровни. Низкий уровень на выходе элемента 7 сменяется высоким, но это не приводит к изменению состояния элементов 3 и 4.

Пусть в момент присутствия на входе 2 импульса синхронизации низкого уровня высокий уровень управляющего сигнала на входе 8 сменяется низким, т.е. формируется передний фронт. При этом на вход элемента 4 поступает разрешающий низкий уровень со входа 8, а на вход элемента 3 с выхода инвертора 9 — запрещающий высокий уровень.

Однако эти переходы не изменяют состояния элементов 3 и 4 так как на их входы пс дается высокий уровень с элемента 7, И только по окончании входного импульса на входе 2 выход элемента 7 устанавливается на низкий уровень. Вследствие этого появляется высокий уровень на входе элемента 4, Этот высокий уровень с приходом очередного импульса на вход синхронизации

2 разрешает установку в единицу триггера

1, блокирует срабатывание элемента 7.

При этом на выходе триггера 1 формируется импульс, совпадающий по фазе и длительности с импульсом синхронизации на входе

2. Появление высокого уровня на прямом выходе триггера 1 переводит выход элемента

4. на низкий уровень, что вызывает срабатывание логического элемента 7 и установление на его выходе высокого уровня.

С появлением на входе 2 высокого уровня паузы выход элемента 7 устанавливается на низкий уровень. Состояние других элементов не меняется.

В таком состоянии формирователь находится до очередного изменения урбвня управ45 ляющего сигнала на входе 8.

Пусть смена низкого уровня высоким, т.е„ формирование спада управляющего сигнала, происходит в момент присутствия на входе

2 высокого уровня паузы. Тогда появление низкого уровня на выходе инвертора 9 вызовет появление высокого уровня на выходе элемента 3. В таком состоянии формирователь остается до прихода очередного импульса на вход 2. По фронту входного импульса триггер 1 возвращается в исходное нулевое состояние. При этом высокий уровень инверсного выхода триггера устанавливает на низкий уровень выход элемента 3, что разрешает срабатывание элемента 7. На выходе триггера формируется импульс, совпадающий по фазе и длительности с импульсом на входе 2. С появлением на входе 2 высокого уровня паузы формирователь оказывается в исходном состоянии.

Таким образом, предлагаемый формирователь формирует импульсы стабильной длительности, определямой длительностью синхроимпульса, Точность привязки импульса к фронту и спаду потенциала определяется величиной периода импульсной последователь ности синхроимпульсов, Формула изобретения

Формирователь импульсов малой длительности по переднему и заднему фронтам входного импульса по авт.св. М 373864, о т— личающийся тем, что, с цельюре гулирования длительности выходного импульса, в него введены источник синхронизирующих импульсов и дополнительный логический элемент, один из входов которого соединен с выходом источника синхронизирующих импульсов и с установочным входом КВ

-триггера, второй и третий входы дополнительного логического элемента подключены к выходам основных логических элементов, третьи входы которых соединены с выхо» дом дополнительного логического элемента.

Источники информации, принятые во внимание при экспертизе:

1. Авт.св. М 373864, Я.Кл. Н 03 К 5/01, 1971.

527817

Составитель Ю. Еркин

Редактор Б. Федотов Техред А. Демьянова Корректор А. Власенко

Заказ 716/48 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4