Счетчик импульсов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ЙЯ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву(22) Заявлено 05.06.75 (21) 2140410/21 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано 05,09,,76,Бюллетень ¹33 (45) Дата опубликования описания 19.05.77 (51) М. Кл.еН 03 K 28, 0:? .

Государственный комитет

Совета Министров СССР по делам изобретений и открытий

РЗ) ЬДК621Д-,.;,.-. (088„8) (72) Авторы изобретения

Ю. B. Рябов, И. И, Володарский и С. С. Политковский (71) Заявитель (54) СЧЕТЧИК ИМПУЛЬСОВ

Изобретение относится к вычислительной технике.

Известен счетчик импульсов на логичес ких потенциальных элементах, содержащий в каждом разряде две последовательно включенные ячейки памяти, соединенные между собой элементами "И-НЕ", и шины четных и нечетных сигналов (1). Эти счетчики малонадежны, Известен счетчик импульсов, содержащий щ д ячеек памяти, каждая из которых состоит из двух элементов "ИЛИ-НЕ", соединенных между собой элементами "И", шины четных и нечетных сигналов (2).Однако вьптолнение счетчика по предложенной схеме из- 1б за разброса характеристик транзисторов не исключает "состязания" при переключении ячеек памяти„ что приводит к сбою счетчика (2) .

Бель изобретения — упрощение и повыше- gp ние надежности схемы-достигается путем введения в счетчик элементов "ИЛИ-НЕ" и шины сброса четных и нечетных ячеек памяти, причем входы первого элемента "ИЛИНЕ соединены с выходами четных ячеек 25 памяти, а выход подключен к перво ду второго элемента "ИЛИ-HE", в-=о=, которого соединен с шиной:етных с.;..гн;.:.-г а выход подключен к шине сбооса .,c-.- .;с. ячеек памяти, входы третьего элеме:.:.,:

"ИЛИ-НЕ" соединены с выходами не-:.ст, ячеек памяти, выход подключен к первому входу четвертого элемента ИЛИ»НЕ", второй вход которого соединен с шиной нечетных сигналов, а выход подключен к шине сброса четных ячеек памяти.

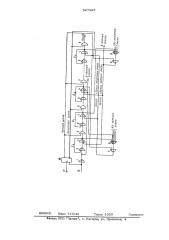

На чертеже представлена схема устройства.

Счетчик импульсов состоит из логическо-го элемента "ИЛИ-НЕ" 1, и транзисторных ячеек памяти 2, — 2, содержащих два лс гических элемента "ИЛИ-HE 3, 4 (и-:побое нечетное число), соединенных между собой элементом "И" 5; дополнительно введенных логических элементов ИЛИ-HE 6-9 и триггера 10 подачи импульсов на четную и нечетную шины, счетный вход которого подключен ко входной шине 11, а вход сброса подключен ко входу элемента ИЛИ-HE

1 и к шине сброса 12, 527825

Счетчик работает следующим образом.

Перед началом работы на шину 12 подается импульс "сброс", в результате кот рого на нечетной шине триггера 10 появляется единичный сигнал, а на четной - нулевой. Импульс "сброс" подается также на элемент "ИЛИ-НЕ 1, на выходе которого появляется единичный сигнал, приводящий ячейку памяти 2О в единичное состояние, а все остальные четные ячейки памяти - в io нулевое. Единичный сигнал ячейки памяти

2о подается на элемент "ИЛИ-НЕ" 6, а нулевой сигнал с элемента 6 - на элемент

"ИЛИ-НЕ" 7. Единичный сигнал с элемента

7 поступает в шину сброса нечетных ячеек, 15 приводя все нечетные ячейки в нулевое состояние. Единичный сигнал ячейки памяти

2 одновременно поступает на ее элемент

"Й" 5, подготавливая тем самым ячейку памяти 2 к срабатыванию. 20

При появлении первого счетного импульса на входной шине 11 на четной шине триггера 10 появляется единичный сигнал, на нечетной — нулевой, Единичный сигнал с чу ной шины попадает на элементы "И" 5 всех 25 четных ячеек памяти, но, так как к срабатыванию подготовлен только один элемент И"

5 ячейки памяти 2, только на ней появляо ется единичный сигнал, приводя эту ячейку памяти в единичное состояние и оставляя остальные ячейки в исходном положении. Единичный сигнал ячейки 2 подготавливает к срабатыванию элемент "И" 5 ячейки памяти 2 и подается на элемент "ИЛИ-HE" 8, При этом на выходе элемента ИЛИ-НЕ" 8 появляется нулевой сигнал, а так как на нечетной шине в данный момент нулевого сигнала нет, то на выходе элемента "ИЛИ-НЕ" 9 появляется задержанный единичный сигнал, который поступает на шину сброса 40 четных ячеек памяти. Ячейка 2о возвращается в нулевое состояние, При подаче второго счетного импульса на триггер 10 на четной шине появляется нулевой сигнал, а на нечетной - единичный. 4

Единичный сигнал нечетной шины приводит к срабатыванию элемента "И" 5 ячейки памяти 2 (на выходе ее появляется единичный сигнал), переводя ячейку 2 в единичо ное состояние, подготавливая к срабатыванию свой элемент "И" 5. Единичный сигнал ячейки 2 подается на элемент "ИЛИ-НЕ"

6. На его выходе появляется нулевой сигнал, который подается на элемент "ИЛИ-НЕ" 7, а так как в данный момент на четной шине тоже нулевой сигнал, то на выходе элемента ИЛИ-НЕ" 7 появляется единичный сигнал. Данный единичный сигнал подается на шину сброса в исходное состояние ячеек памяти и приводит ячейку памяти 2 в нулеМ вое состояние.

При подаче следующего счетного импульпульса на триггер 10 на четной шине появляется единичный сигнал, а на нечетной— нулевой и т.д.

В предложенной схеме счетчика импул сов дополнительные элементы "ИЛИ-НЕ» объединены в две пары, которые включены в шины сброса четных и нечетных ячеек памяти. Это позволяет для и — ячеечного счет чика импульсов уменьшить количество пар элементов "ИЛИ-НЕ в и-1/2 раз. Кроме того, повышается надежность бесперебойной работы счетчика.

Формула изобретения

Счетчик импульсов, содержащий ячеек памяти, каждая из которых состоит из двух элементов "ИЛИ-НЕ", соединенных между собой элементами "И", шины четных и нечетных сигналов, о т л и ч а .ю шийся тем, что, с целью упрощения и повышения надежности, в него введены дополнительные элементы "ИЛИ-HE" и шины сброса четных и нечетных ячеек памяти, причем входы первого элемента "ИЛИ-НЕ" соединены с выхо дами четных ячеек памяти, а выход подключен к первому входу второго элемента

"ИЛИ-НЕ", второй вход которого соединен с шиной четных сигналов, а выход подключен к шине сброса нечетных ячеек памяти, входы третьего элемента "ИЛИ-НЕ соединены с выходами нечетных ячеек памяти, выход подключен к первому входу четвертого эле» мента "ИЛИ-НЕ", второй вход которого соединен с шиной нечетных сигналов, а выход подключен к шине сброса четных ячеек памяти.

Источники информации, принятые во внимание при экспертизе изобретения:

1. Авт. св, СССР М 291331, М. Кл. Н 03 К 5/159, 14.10.68.

2. Выложенная заявка ФРГ % 2345670, Кл, 21 а 1 36/22, Н 03 К 23/02, опубликованная 04.07.74 (прототип).