Накапливающий сумматор

Иллюстрации

Показать всеРеферат

528566

65 ки памяти, элемента «ИЛИ» и элемента

«НЕ», причем первые входы элементов «И» подключены к .первому входу управляемого узла задержки, второй вход которого подключен ко второму входу первого элем нта «И», первому входу ячейки памяти и входу элемента «НЕ», (выход которого подключен ко второму входу второго э. мента «И», выход которого связан с первым входом элемента

«ИЛИ», выход которого подключен к выходу управляемого узла задержки, а второй вход — к выходу ячейки памяти, второй вход которoé связа.t с выходом первого эллента «И».

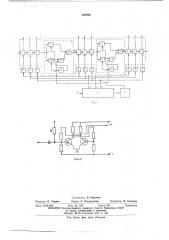

При этом управляегмый узел задержки выполнен в виде симметрично; о трн,.": ера с одним импульсным входом, связанным с первым .входом управляемого узла задержки, и одним потенциальным входол, связапным со вторым входом управляемого узла задержки.

Все это позволяет уменьшить общее число ячеек путем уменьшения ячеек в распределителе, а также повысить быстродействие в результате одновременной записи информации во всех группах счетчика.

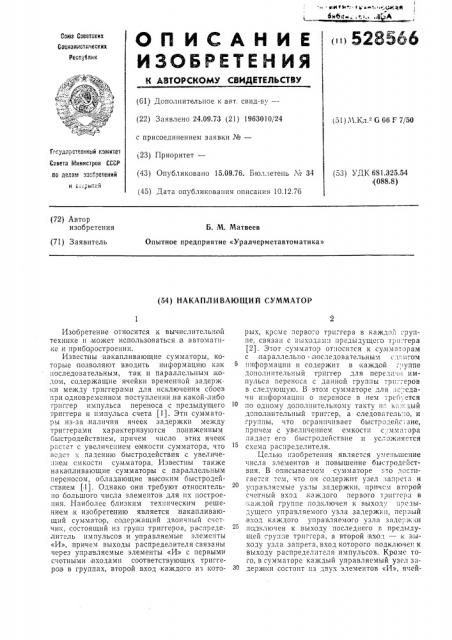

На фиг. 1 представлена блок-схема описываемого сумматора; на фнг. 2 — управляемый узел задержки B одном нз вариантов в ы п о ляе.н и я.

В блок-схеме для удобства рассмотрения счетчик разбит на три группы по три триггера в каждой. Однако в принципе число групп триг-.еров не ссраничивается. В оощсм жс случае накапливающий сумматор содержит

Л триггероз, разбитых tta пг групп, содержащих каждая не более и триггеров. В состав счетчика сумматора входят управляемые узлы задержки " колнчестзс, равном (m — 1).

Описываемый сумматор "о;1ержит двои tный с ет-шк 1, включеиощнй в сеоя группы триггеров 2 и управляемые узлы задержки

8; распределитель 4, запускаемый импульсами, посту. ающими tta вход 5, н вырабатывающий на своих выходах б, 7, 8 сдвинутые во времени импульсы; управляемые элементы

«И» 9, которые включаются в соответствии с кодом числа, которое необходимо записать в счетчик; узел запрета 10,,вырабатывающий сигнал на время работы распределителя 4.

Управляемые узлы задержки содержат каждый по два элемента «И» 11, 12, ячейку памяти 18, элемент «НЕ» 14 и элемент «ИЛИ»

15; lб, 17 — входы управляемого узла задерюа, 18 — его выход.

Первые счетные входы триггеров 2 через элементы «И» подключепы,к выходам б, 7, 8 распределителя импульсов 4; вторые счетные входы первых триггеров 2 всех групп, кроме первой, подключены,к,выходам 18 соответствующих управляемых узлов задержки 8: вто,рые счетные входы последующих триггеров 2 в гру:гпах подключены к выходам предыдущих триггеров 2. Первые входы lá управляемых узлов задержки 8 под ключены к выхо5

40 дам последних в группах триггеров, а вторые входы 17 — к выходу узла запрета 10.

В состоянии покоя элементы «И» 11 открыты, элементы «И» 12 — закрыты. Во время работы распределителя 4 элементы «И»

11 закрыты, элементы «И» 12 — открыты, ячейка памяти 18 устанавливается в исход ное состояние и выдает рабочий импуль" прп переходе B исходное состояние з момент снятия -.изгнала с узла запрета 10.

Управляемый узел задержки (см. фиг. 2), выполнен на симметричном триггере (или одновибраторе) с одним импульсным н вторым потенциальным, входом. При соответствующем значении резистора 19 наличие отрицательного сигнала на выходе 18 переводит триггер в режим работы с одним устойчивым состоянием, и GII пропускает без задержки сигналы, поступающие на его импульсный вход.

При поступлении на вход 5 запускающего импульса срабатывает распределитель им пульсов 4. При этом на выходах б, 7, 8 вырабатываются сдвинутые во времени импульсы, которые через QTtKpbIYble элементы «И» 9 поступают на nepat te счетные входы соответствующих триггеров 2. При этом в каждую группу записывается требуемое число. При переполнении .какой-либо, группы на выходе послед него триггера 2 этой группы появляе;— ся си гнал, который подается на вход lб следующего управляемого узла задержки 8. При этом, если распределитель 4 работает, TO импульс переноса через элемент «И» 12 поступит з ячейку памяти, которая сбрасывается в исходное состояние в момент окончания работы распределителя 4 и передает этот импульс переноса в следующую группу тзиггсзов 2. Если же распределитель 4 не раоотает в ilсмент переполнения кахой-либо группы, то импульс через элемент «И» 11 н элемент «ИЛИ» 15 проходит без задержки в сле 1ующую группу.

Лналогично работает управляемый узел задержки 8, выполненный i виде снмметрнчH0I".о триггера. Когда распределитель нмпульсоз работает, импульс переполнения с прелыдущего триггера 2 устанавливает триггер в состояние «1». В,момент окончания раооты распределителя импульсов 4 триггер переводится в состояние «0» и передает единицу в первый триггер 2 следующей группы. При неработающем распределителе 4 триггер работает в режиме с одним устойчивым состоя,нием и про пуокает без задержки импульсы, поступающие на вход lб.

Таким образом, исключается накладка импульсов при одновременной за.шси чисел в разные группы, а перенос единицы осуществляется, когда распределитель не работает.

Общее чи";10 К ячеек задержки и управляемых узлов задержки равно

528566 т. е. экономия з ячейках будет равна

Х вЂ” 1 — К=У вЂ” и — — — 1. и

Выведем соотношение между A и и, обеспечивающее минимальное число ячеек задержки. Для этого определим экстремум для К сИ N — = 1 — —., dи и -

Приравняв полученное выражение нулю, получим и:), N

При этом обеспечивается минимальное ",èñëî ячеек задержки в счетчике и в распределителе.

Общее число ячеек в этом случае равно

К==2)г Л что дает экономию в

Ь = N — 1 — 2 )/ i\Г + 1 = N — 2 )/N ячеек задержки.

Принцип, заложенный в описываемый сумматор, может быть использован и для тех случаев, когда коэффициент пересчета cóìматора в целом или его групп отличается от двоичного, т. е. когда,в счетчик вводятся дополнительные связи, а также когда запись чисел ведется .в коде, отличном от двоичного.

Формула изобретения

1. Накапливающий сумматор, содержащий двоичный счетчик, состоящий из групп триггеров, распределитель импульсов и управляе= мые элементы «11», причем выходы распределителя связаны через управляемые элеме11ты

«И» с первыми счетными входамп соответствующих три1хгеров в группах, второй вход каждого из .которых, кроме первого триггера в каждой группе, связан с выходом предыдущего триггера, отличающийся тем, что, с целью уменьше1шя числа элементов и:1овышения быстродействия, сумматор содержит узел запрета и управляемые узлы задержки, причем второй счетный вход каждого первого триггера в каждой группе подключен к выходу .предыдущс-.о управляемого узла задерж ки, первый вход каждого управляемого узла задержки подключен,к выходу последнего в предыдущей группе триггера, а второй вход — к выходу узла запрета, вход которого подключен к выходу распределителя импульсов, 2. Сумматор по и. 1, отличающийся тем, что каждый управляемый узел задержки состоит нз двух элементов «И», ячейки памяти, элемента «ИЛИ» и элемента «НЕ»,,причем первые входы элементов «И» подключены к,первому входу управляемого узла задержки, второй вход которого подключен .ко второму входу первого элемента «11», первому входу ячейки памяти и входу элемента

«НЕ», выход которого подключен ко второму входу второго элемента «11», выход которого связан с первым входом элемента «ИЛИ», выход которого,подключен к выходу управляемого узла задержки, и второй зход— к выходу ячейки .1амяти, второй вход которой связан с выходом первого элемcíта «И».

3. Сумматор по п. 1, отличающийся

4О тем, что управляемый узел задержки выполнен в виде симметричного триггера с одним импульсным входом, связанным с первым входом управляемого узла задержки, 11 одним .потенциальным входом, связанным со

45 вторым входом управляемого узла задержки.

528566 врун 2

Составитель В. Березкин

Техред Е. Подурушина

Корректор И. Симкииа

Редактор Л. Тюрина

Заказ 1648/1085 Изд. Ма 1785 Тираж 864 Подписное

ЦНИИПИ Государственного коиитета Совета Министров СССР по делам изобретений и открытий

Москва, )К-35, Раушская наб., д. 4/5

Тип. Харьк. фил. пред. «Патент»