Асинхронный регистр сдвига

Иллюстрации

Показать всеРеферат

(t t) 5286I2

ОП ИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 26.03.73 (21) 1897837/24 с присоединением заявки № (23) Приоритет

Опубликовано 15.09.76. Бюллетень ¹ 34

Дата опубликования описания 12.10.76 (51) М. Кл.2 G 11С 19 00

Государственный комитет

Совета Министров СССР, по делам изобретений и открытий (53) УДК 681.327,66 (088.8) (72) Авторы изобретения

А. Г, Астановский, В. И. Варшавский, В. Б. Мараховский, И. А. Насибуллин, В. A. Песчанский, Л. Я. Розенблюм, Н. А. Стародубцев и P. Л. Финкельштейн (71) Заявитель М щи (54) АСИНХРОННЫЙ РЕГИСТР СДВИГА

Изобретение относится к области цифровой вычислительной техники.

Известны различные модификации схем синхронных сдвиговых регистров (1, 2). Эти устройства, несмотря на различия принципиальных схем разрядов регистров (в первом использованы вентили ввода, во втором — дополнительный элемент И вЂ” НЕ), обладают общим недостатком. Наличие внешних тактовых сигналов не позволяет увеличить быстродействие регистров по сравнению с тем быстродействием, которое рассчитано с учетом максимальных задержек, вносимых логическими элементами схемы.

В упомянутых выше регистрах сдвига используются по два триггера на разряд и дополнительные элементы. Такое построение предусматривает, в основном, двухтактную работу (например, во втором применено предварительное обнуление), что приводит к снижению быстродействия регистра.

Наиболее близким по технической сущности к данному изобретению является регистр сдвига, содержащий в каждом разряде по три триггера, соединенных последовательно и выполненных на потенциальных элементах, три элемента И вЂ” НЕ, шины управления (3).

Однако, такому регистру присущ тот же недостаток — расчет его быстродействия должен производиться, исходя из максимально возможных задержек логических элементов. В применяемых в настоящее время в промышленности потенциальных элементах отношение максимальной задержки к минимальной нахо5 дится в пределах 10 — 20. Очевидно, что если регистр будет работать по реальным задержкам элементов, его эффективное быстродействие должно быть существенно выше. Кроме того, если уход величины задержки логическоt() го элемента за верхний предел, гарантируемый техническими условиями, является в синхронных регистрах причиной отказов, то в регистрах, работающих по реальным задержкам элементов, он приведет лишь к некоторому за15 медлению работы.

Целью изобретения является повышение надежности и быстродействия регистра.

Для этого в регистр сдвига введены трп дополнительных триггера, причем прямой и пн20 версный выходы каждого триггера в разрядах соединены со входами соответствующего элемента И вЂ” НЕ и с первыми входами соответствующих дополнительных триггеров, выходы элементов И вЂ” НЕ соединены со вторыми вхо25 дами соответствующих дополнительных триггеров, счетные входы первого, второго и третьего триггера каждого разряда соединены соответственно с прямыми выходами второго и третьего дополнитель ых триггеров и с шиной

3() сдвига, прямой выход первого дополнительного

65 триггера соединен с первой шиной управления, а вторая шина управления соединена со вторым входом третьего дополнительного триггера.

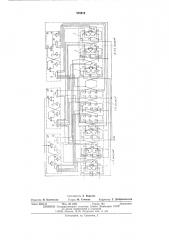

На чертеже изображена функциональная схема предлагаемого синхронного регистра сдвига.

Регистр содержит в каждом разряде три триггера 1, 2, 3 на потенциальных элементах

И вЂ” НЕ. Триггеры имеют счетный вход 4, входы установки 5, 6, инверсный и прямой выходы 7, 8, выход 9, входы установки «О» 10, 11.

Сигналы с выхода 9 указывают на моменты окончания переходных процессов в соответствующем триггере. Регистр содержит также три дополнительных триггера 12-14, выполненных на элементах ИЛИ вЂ” НЕ и элементах

И 15-19, шины 20 управления, выходы дополнитсльных триггеров 21-23, шину 24 сдвига, элементы И вЂ” НЕ 25-27.

На входы 5 и 6 триггера 1 «О»-го разряда постоянно подаются сигналы «О» и «1» соответственно. Выводы 10 и 11 используются в качестве установочных входов только в триггерах 2. Все триггеры в регистре соединены последовательно, а именно — выходы 7 и 8 предыдущего триггера соединены со входами

6 и 5 последующего триггера соответственно.

На шину 24 подается внешний управляющий сигнал сдвига, а на шину 20 — сигнал установки начальйой информации.

Будем называть триггер обнуленным, если на его общий вход 4 подан сигнал «О». В этом случае на его выходах 7 и 8 установлены сигналы «1», на выходе 9 — сигнал «О». Если же на вход 4 подан сигнал «1», то триггер хранит информацию (сигнал на одном из выходов равен «1», на другом — «О») и на выходе 9 сигнал равен «1» При обнулении и записи информации изменение значения сигнала на выходе 9 свидетельствует об окончании переходных процессоров в триггере.

Выходы 7 и 8 всех триггеров соединены со входами элементов 15 дополнительных триггеров, а выходы 9 — со входами элементов 18 дополнительных тритгеров следующим образом: триггеры 1, 2 и З,всех разрядо в — с дополнительными триггерами 12, 13 и 14 соответственно. Прямые выходы 22 и 23 дополнительных триггеров 13 и 14 соединены со входами 4 триггеров 1 и 2 соответственно.

Дополнительный триггер работает следующим образом. Если соединенные с его входами триггеры обнулены, то на всех входах элемента 15 сигналы равны «О», на инверсном выходе триггера устанавливается «О», а на прямом — «1», так как на всех входах элемента 18 сигналы равны «0», Это справедливо для дополнительного триггера 14 в том случае, когда на вход 20 элемента 19 подается сигнал «О», если же он равен «1», то на прямом выходе установится сигнал «О». Если все триггеры, подключенные к дополнительным триггерам, хранят информацию, то на всех входах элемента 18 сигнал равен «1». Поэтому

50 па прямом выходе дополнительного триггера в этом случае установится сигнал «О», а на инверсном — «1», госкольку на половине входов элемента 15 сигналы будут равны «О».

Значение сигнала на входе элемента 19 в данном случае безразлично. Элементы 16 и 17 служат для организации обратных связей. Таким образом, если соединенные с дополнительным триггером триггеры регистра обнулены, то на выходе дополнительного триггера сигнал равен «1», если же они хранят информацию или на вход элемента 19 подан сигнал «1», то на выходе дополнительного триггера — «О».

В начальном состоянии сигнал сдвига равен

«О», триггеры 1 и 3 каждого разряда обнулены, в триггерах 2 записана информация. Устойчивость начального состояния обеспечивается следующим образом; на выходе 23 дополнительного триггера 14 сигнал равен «1», на выходе 22 дополнительного триггера 13 сигнал равен «О», на выходе 21 дополнительного триггера 12 сигнал равен «0».

Цикл работы регистра (сдвиг на 1 разряд в сторону старших разрядов) состоит из трех фаз.

В первой фазе, если сдвиг разрешен, сигнал сдвига изменяется с «О» на «1», разрешая прием информации из триггеров 2 в триггеры

3. Ilo окончании записи сигнал на выходе 23 дополнительного триггера 14 станет равным

«О», что вызовет обнуление всех триггеров 2.

На выходе 22 дополнительного триггера 13 установится сигнал «1». Фаза закончена, триггеры 3 хранят информацию, триггеры 2 и 1 обнулены, Во второй фазе сигнал «1» с выхода 22 дополнительного триггера 13 разрешает перепись с триггеров 3 i-го разряда в триггеры 1 (i+1)-го разряда. По окончании процесса записи на выходе 21 дополнительного триггера

12 установится «О». По этому сигналу снимается разрешение сдвига, после чего сигнал сдвига изменяется с «1» на «О». Это вызывает обнуление всех триггеров 3. На выходе 23 дополнительного триггера 14 устанавливается сигнал «1». Фаза закончена. В триггерах 1 хранится сдвинутый на один разряд в сторону старших разрядов первоначально записанный в триггерах 2 код. Все триггеры 2 и 3 обнулены.

В третьей фазе сигнал «1» на выходе 23 дополнительного триггера 14 разрешает перепись информации из триггеров 1 в триггеры 2.

1lo окончании записи на выходе 22 дополнительного триггера 13 установится сигнал «О», который оонулит триггеры 1, в результате чего на выходе 21 дополнительного триггера 12 установится сигнал «1». Все триггеры l и 3 обнулены, триггеры 2 хранят код, сдвинутый на один разряд.

Цикл сдвига закончен. Момент окончания сдвига на 1 разряд индицируется изменением сигнала на выходе 21 с «О» на «1». Этот сигнал по первой шине управления направляется в устройство, управляющее бдвигом, после чего может быть начат следующий цикл сдвига.

Установка начальной информации производится в каждом разряде по входам 10 и 11 триггера 2 подачей взаимоинверсных значений сигналов, сигнал сдвига при этом должен быть равен «О». На вход 20 (по второй шине управления) подается сигнал «1», при этом обнуляются все триггеры 2. Момент окончания их обнуления индицируется на выходе 22 изменением сигнала с «О» до «1». После этого сигнал на входе 20 должен быть изменен с «1» на

«О». Окончание процесса установки совпадает с моментом изменения сигнала на выходе 22 с «1» на «О».

Предложенный регистр сдвига работает по реальным задержкам элементов благодаря индикации моментов окончания переходных процессов. Испытания показали, что это приводит к увеличению быстродействия регистра в 3—

4 раза по сравнению с аналогичными синхронными, повышает надежность по отношению к параметрическим отказам логических элементов, а элементы встроенной индикации диагностируют возможные отказы устройства, что существенно упрощает методику ремонта и отыскания неисправностей.

Кроме того, асинхронный регистр сдвига может быть рекомендован для использования в больших интегральных схемах, поскольку благодаря внутреннему тактированию отпадает необходимость в синхронизирующих тактах, что существенно уменьшает количество внешних выводов.

Формула изобретения

5 Асинхронный регистр сдвига, содержащий в каждом разряде по три триггера, соединенных последовательно и выполненных на потенциальных элементах, три элемента И вЂ” НЕ, шины управления, о тл ич а ю щи и ся тем, 1О что, с целью повышения надежности и быстродействия регистра, он содержит три дополнительных триггера, причем прямой и инверсный выходы каждого триггера в разрядах соединены со входами соответствующего элемента

15 И вЂ” HE» с первыми входами соответствующих дополнительных триггеров, выходы элементов

И вЂ” НЕ соединены со вторыми входами соответствующих дополнительных триггеров, счетные входы первого, второго и третьего тригге20 ра каждого разряда соединены соответственно с прямыми выходами второго и третьего дополнительных триггеров и с шиной сдвига, прямой выход первого дополнительного триггера соединен с первой шиной управления, а

25 вторая шина управления соединена со вторым входом третьего дополнительного триггера.

Источники информации, принятые во внимание при экспертизе изобретения:

1. Авт. св. ¹ 251617, кл. G 11С 19/00, 1969 г. зо 2. Авт св. ¹ 305589, кл. Н ОЗК 23/00, 1971 г.

3. Авт. св. ¹ 228855005544, кл. G 11С 19/00, 1970 г. (прототип).

528612

Составитель А. Воронин

Техред М. Семенов Корректор T. Добровольская

Редактор Н. Каменская

Типография, пр. Сапунова, 2

Заказ 2063715 Изд. Хе 1609 Тираж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 7К-35, Раушская аб., д. 4, 5