Адаптивное вычислительное устройство

Иллюстрации

Показать всеРеферат

О П И С А Н К Е 11,5gg45g

Союз Советских

Социалистических

Республик (® (61) Дополнительное к авт. свид-ву (22) Заявлено30. 10.74 (21) 2071514/24 с присоединением заявки № (51) v(. Кл. G 06 f 7/38

Государственный комитет

Совета Миннстрав СССР

flD делам изабретеннй и открытий (23) Приоритет (43) Опубликовано25.09.76. Бюллетень N- 35 (53) УДК 681 327

{088,8) (45) Дата опубликования описания 01.1 2. 76 (72) Авторы изобретения

Г.С. Пирамуа и В.A. Богатырев

Грузинский ордена Ленина и ордена Трудового Красного Знамени политехнический институт им. В. И. Ленина (71) Заявитель (54) АДАПТИВНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к устройствам для обработки цифровых данных и может использоваться в адаптивных цифровых вычислительных машинах.

Известно адаптивное вычислительное уст- 5 ройство, содержащее два многофункционных логических блока, блоки сравнения и блок настройки fl).

Однако это устройство требует значительного обьема оборудования на два парал- 10 лельно работающих многофункциональных блока.

Известно также устройство, содержащее идентичные многофункциональные блоки, контрольный орган, распределитель функций и !5 выходной блок 1 2). Однако это устройство имеет сложный контрольный орган.

Наиболее близким техническим решением к предлагаемому устройству является адаптивное вычислительное устройство, содержа- 20 щее регистр, многофункциочальные блоки, подключенные через соответствующие элементы И ко входам выходного блока и блока сравнения„ одни входы которого соединены с выходами регистра сдвига, а выход — 25 со входом распределителч функций, выходы которого подключены Ко входам многофункциональных блоков и управляющим входам элементов И f3).

Недостатками этого устройства являют» ся большие аппаратурные затраты оборудования.

Цель изобретения — упростить устройство и повысить его надежность.

Это достигается тем, что выходы регист— ра сдвига через соответствующие элементы

И подключены ко входам многофункциональж х блоков и непосредственно — ко входам регистра, выходы которого соединены с другими входами блока сравнения.

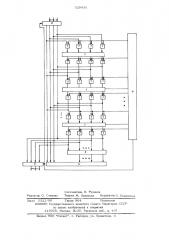

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство содержит пт и -разрядных многофужциональных блоков 1, выходной блок 2, блок сравнения 3, распределитель функций 4 {r> — L ) — разрядный регистр 5, — разрядный регистр сдвига 6, 28 rn эле« ментов И 7 соединяющих многофункциональные блоки 1 с выходным блоком 2 и - бло529456 ком сравнения 3. Выходы регистра сдвига

6 через соответствующие элементы И 7 подключены ко входам многофункциональных блоков 1 и непосредственно — ко входам регистра 5, выходы которого соединены с одними входами блока сравнения 3, другие входы которого соединены со входами регистра сдвига 6.

Устройство работает следующим образом, Операнд записывается в регистр сдвига

6, с которого оы полается через соответствующие элементы И1 на (0 — f ) младших разрядов первого многофункционального блока 1 (на чертеже — верхний). После выдачи результата вычислений с первого мно- 1 гофункционального блока 1 во второй врегистре сдвига 6 осуществляется сдвиг операнда на 8 разрядов и подаче его íà (r)— ь ) старших разрядов первого многофункционального блока 1. Таким образом про— исходит вычисление суммарной функции F в различных разрядах многофункциональных блоков 1 со сдвигом по времени, равным времени вычисления функции т в одном блоке 1. Результат вычисления суммарной 25 функции F на (A — 6 ) младших разрядах хранится в регистре 5 в течение промежутка времени вычисления элементарной функции 1- в одном блоке, чем достигается одновременный приход на блок сравнения 3 30 результатов вычисления на (il — f ) младших и (n — 3) старших разрядах мно. Рункциональных Л -разрядных блоков 1. чае совпадения результатов происходит дача с выходного блока 2 результатов 35 числения суммарной функции F на (П— старших разрядах многофункциональных бл . ков 1 (а,, а ... а ), в противном случае включается распределитель функций

4, производящий перераспределение элемен- 40 тарных функций (,, ... ), возложенных на многофункциональные блоки 1.

Одновременно происходит блокировка выдачи результата вычислений с выходного блока 2 и возвращение операнда в регистре сдвига 6 в исходное состояние. Процесс повторяется сначала до тех пор, пока результаты вычисления суммарной функции F на различных разрядах блоков не совпадут т.е. не возобновится правильное функционирование (можно считать, что на различных разрядах блоков 1 одновременно не может возникнуть неисправность, приводящая к одинаковому искажению результатов).

Осуществление простого перебора настроек, используемого в данном изобретении, позволяет получить выигрыш B оборудовании., т.е. приводит к значительному упрощению устройства.

Формула изобретения

Адаптивное вычислительное устройство, содержащее регистр, многофункциональные блоки, подключенные через соответствую— щие элементы И ко входам выходного блока и блока сравнения, одни входы которого соединены с выходами регистра сдвига, а выход — со входом распределителя функций, выходы которого подключены ко входам многофункциональных блоков и управляющим входам элементов И, о т л и ч а ю m e— е с я тем, что, с целью повышения надежности и упрощения устройства, выходы регистра сдвига через соответствующие элементы И подключены ко входам многофункциональных блоков и непосредственно ко входам регистра, выходы которого соединены с другими входами блока сравнения.

Источники информации>принятые во внимание при экспертизе:

l. Авторское свидетельство СССР № 260968, М.Кл. 5 06 F 7/00, 1968.

2. Авторское свидетельство СССР № 363091, М.Кл. G 06 F 11/00, 1971.

3. Заявка № 2067347, М. Кл.

С 06 Р 7/00, 1974.

529456

Составитель В. Рудаков

Редактор О. Стенина Техред М. Левицкая корректор Л. Боринская

Заказ 5321/90 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

1 1 3035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4