Запоминающее устройство

Иллюстрации

Показать всеРеферат

6N6AooToHR й!Я

Союз Советских

Социалистимеских

Республик (11) Q29481

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено10.04.75 (21) 2123826/24 с присоединением заявки ¹ (23) Приоритет (43) Опубликовано25.09,76,Бюллетень № 35 (45) Дата опубликования описания 07.12.76 (51) Ч. Кл,-

С 11 С 11 00

G 11 С 29/0С

Государственный комитет

Совета Министров СССР оо делам изооретений и открытий (53) У ДК 68 1. 32 7,6

{088,8) А, В. Городний, В. И, Корнейчук, В, П, Тарасенко и Я, И. Торошанко (72) Авторы изобретения (71) 3

Заявитель

Киевский ордена Ленина политехническпй институт им 50-летия о

Великой Октябрьской социалистической революц!и (54) ЗАПО!ЧИНАЮШЕЕ УСТРОЙСТВО ванпя и одного из триггеров.

Изобретение относится к запоминающим устройствам.

Известно запоминаюцсее устройство, содержащее регистр адреса, накопитель, блс ки кодирования и декодирования, регистр мощности корректирук:щего кода (11. Недостатком этого устройства являются большие аппаратурные затраты, Известно также запоминаю..цее устройство, содержащее накопитель, подключенный через !О блоки кодирования и декодирования к регистру числа, дешифратор, вход которого подключен к регистру адреса, а выход через одни элементы И ко входам регистров мощности корректирующего кода, выходы котс» 15 рых че ре з другие зле ме нты И с седине ны со входами блоков кодирования и декодирования, и блок управления L2 1.

В таком запоминающем устройстве при отказе одного или нескольких элементов 20 памяти, а также при случайных сбоях ошно ки корректируются блоками кодирования и декодирования, которые управляются регистрами мощности корректирующего кода.

Информация каждой страницы накопителя 25 кодируется в зависимости от максимальнсI 0 KQJIII IBOTBB 0TKBBDB !! cJIW IÉI!b!x сбоеь в одной ячейке данной сòðàíèöû накопителя.

Однако В тако-"! запОми11аюц1ем у строй стае на величину мощности корректиру юще—

1 о кода значительно ьлняот случайныс- сбои, что ведет к нерационал ному использование технического ресурса оборудования и cIIIIжает эффект вную емкость устройсTBB.

tJ.0JII» изобретен!!я — I:рост!1Tb у стр 01!СТЬ О И П ОВЫСIIТЬ ЕГО ЭффЕ 1 .Т! I ь НУЮ Е МК Oi ТЬ, Это достигается те»м, что задо. .шнающее устройство содержит счетч!!к, ьходь: и выход которого подключены к выходам и входу блока управления, дополнительны11 элемент И и два триггера, одни входы KDторых подключены соответственно I выходам блока декодирования и дополнптельпогс зле еt!та И выходы и двугпе ьходы — ко

1 входам и выходам блока у!1!уаьления, входы дополнительного элемента И саед!!ноны соответственно с выходами блока декодиро529481

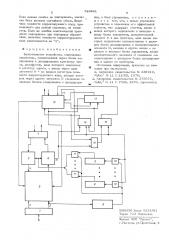

На чертеже изображена структурная электрическая схсма предлагаемого запоминающего устройства.

Устройство содержит регистр адреса 1 выходы 2 которого соединены с накопителем, 3, вход 4 которого соединен с выходом блока кодирования 5, блок декодирования 6, регистр числа 7, Выход старших разрядов регистра адреса 1 соединен со входом дешифратора 8, выход которого соединен с регистрами мощности корректирующего кода 9 через элементы И 10.

Выходы регистров мощности корректирующего кода 9 соединены с одними входами элементов И 11, выходы которых подключены к управляющим входам блоков кодирования 5 и декодирования 6. Другие входы элементов И 11 соединены с выходом дешифратора -8. Кроме того, устройство содержит блок управления 12, счетчик 13, два триггера 14 и 15 и дополнительнь1й элемент И 16, Выход 17 б.пока управления 12 соединен со входами элементов И 10 и со входами установки в "0" счетчика 13 и триггеров 14 и 15.

Вход установки в "1" триггера 14 соединен со входом дополнительного элемента И 16 с выходом 18 блока декод11рс-вания 6. Выход триггера 14 соединен со входами блока управления 12 и p,oïo1àнительного элемента И 16, выход которс го подключен ко входу установки в "1" триггера 15, Вь xoq последнего связан с блоком управления 12, соединенным с выходом счетчика 13, с накопителем 3, со счетным входом счетчика 13, со входами установки в "0" счетчика 13 и триггера 14.

Запоминающее устройство работает следующим образом.

Код адреса я1ейки, к которой производится обращеш1е, поступает на регистр адреса 1. Код старших разрядов регистра адреса 1 1.оступает на дешифратор 8, который открывает один из элементов И 11, Блоки кодирования 5 и декодирования 6 настраиваются IIB обработку корректирую..цего кода, мощность которого равна числу, записанному в выбранном регистре мощности корректирующего кода. Запись числа в выбранную ячейку происходит обычным образом. Число из регистра числа 7 псступает на блок кодирования 5 и записывается в выбранную ячейку накопителя 3.

В режиме чтения число из выбранной я:ейки накопителя 3 поступаст ца блок декодирования 6 и записывается íà регистр чис,.а 7.

При работе блока декодирования 6 в режиме чтения возможны два случая.

В первом случае блок декодирования 6 при обращении к t -ой ячейке исправил (rn » 1 ) ог1ибку, где (o- + 1) — число, записанное в соответствующем регистре мощб ности корректирующего кода 9, à rn — максимальное число отказов в одной из ячеек данной страницы, Информация при этом не теряется. Выбранное слово из регистра числа 7 выдается в вычислительную машину, На выходе 18 блока декодирования

6 вырабатывается сигнал о максимальном использовании мощности корректирующего кода, По этому сигналу триггер 14 устанавливается в единичное состояние, по которому блок управгения 12 выдает сигна(б лы на повторное ооращение к 1 -ой ячейке ".акопителя. Одновременчо = каждым обращением к накопителю подается сигнал

"+3. B с .ет llll< 13, EcJ1II Ilptl iN повторных обращениях к t -ой ячейке сигнал о максимальнolvi использовании мощности кор

peIntipy!omeI-o ко B не повтори-.. я, т.е. при первом обращении к !- ой ячейке I ;,icë мес l о случайный сбой, к содерж11;1ому рсгисстра мощности корректирующего кода "1"

2б не прибавляется. По сигна:1у ill счетчика 13 блок управления 12 уста1-:авлttt ает в v счетчик 3 11 I pl ÃI cp 3.4 и выдав устройство управлепп1я ычислительн и

:1ашины сигнал, разрешающий обра1.це -Ivie к

Ю зало .111нающел у устройству, l:c;Iit Itpll oG, Ioi,i из iioI3Toptlcix обращений к t. - ои ячейке ctll" на. о - 1акси. 1&ль ном использовании мощности корректирую35 щегo кода повторяется1 значит, данный о1 каз вызван увеличением числа "-iêàçàâших элементов памяти„Соответствующий с1-:ãttà.tl t-.oñòóïàcò через донc.1нt:òåëüíûé элемент li 16 на вход установки в "1" триг43 гера 15. По едини1ному состоянию триггера 5 блок управления 12 вь:дает сигнал ус -ановк:l в "G" счетчика 13, триггеров 14 и 15, а также сигнал "1" на один из рс гистров ioitittocnt корректирующего кода 9.

4б Инфор бац.1я данной страницы перекодируется оолее мощным корректирую..цим кодом„

Во втором случае блок декодирования 6 при обрац ен .1и к l — ой ячейке исправил число ошибок меньше (tn +1). При этом

56 повторное обращенпс к t -ой ячейке не про:1зводится. Обращение к запоминаюц1ему устр ойству иде: обы чнь;:.1 с и ос об ом.

Таким образом, в г1редлагаемом запоминающем устройстве устраняется влияние слуМ чайных сбоев на величину мощности корректирую цего кода. Это достигается путем анализа причин, вызвавших максимальную кратность ошибки. При появлении ошибки максимальной кратности производи -ся нескольQQ ко повторных обращений к выбранной ячейке„

529481

ИПИ Заказ 5324/81 ж 723 Подписное

Если данная ошибка не повторилась, значит она была вызвана случайным сбоем. Величина мощности корректирующего кода, примененного для данной страницы, не меняется. Если же ошибка максимальной кратности повторилась при повторных обращениях, величина мощности корректирую цего кода увеличивается на "1", Формула изобретения

Запоминающее устройство, содержащее накопитель, подключенный через блоки кодирования и декодирования крегистру числа, дешифратор, вход которого подключен к регистру- адреса, а выход через одни элементы И вЂ” ко входам регистров мощности корректирующего кода, выходы которых через другие элементы И соединены со входами блоков кодирования и декодироваI ния, и блок управления, о т л и ч а ю— щ е е с я тем, что, с целью упрощения устройства и повышения его эффективной емкости, оно содержит счетчик, входы и выход которого подключены к выходам и входу блока управления, дополнительный элемент И и два триггера, одни входы которых подключены соответственно к выходам блока декодирования и дополнительного

10 элемента И, выходы и другие входы — ко входам и выходам блока управления, входы дополнительного элемента И соединены соответст ве н но с выходами бл ока де кодир ования и одного из триггеров.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство М 338919

М.Кл. G 11 С ll/02, 1970.

2. Авторское свидетельство М 375675, М,Кл. G 11 С 7/00, 1970. (прототип), Ы

<ал ППП Патент", г. Ужг ор од, ул. Пр оек тна я, 4