Динамическая ячейка памяти

Иллюстрации

Показать всеРеферат

БСЕСО СЗ .,, ":

ЙЛ ТЕЙТ ЫСЭпблиатьна МБА

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик (11) 529<85

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 25.12,74 (21) 2088058/24 с присоединением заявки № (23) Приоритет (51) М. Кл. G- 11 С 11/40

Гасударственный комитет

Совета Министров СССР оо делам изооретений и открытий (43) Опубликоваыо25,09.76.Бюллетень № 35 (53) УДК 687.327.66 (088.8) (45) Дата опубликования описания 02.12.76 (72) Автор изобретен и»

И. Н. Кабанов (71) Заявитель (54) ДИНАМИЧЕСКАЯ ЯЧЕЙКА ПАМЯ И

Изобретение относится к области вычислительной техники и электроники и может быть использовано в производстве интегральных запоминающих устройств, Известны динамические ячейки памяти, сэдержашие три МДП транзистора (1, 2) В запоминаюших устройствах, построенных на основе таких ячеек, цикл записи состоит из операций считывания и записи, что увеличивает длительность цикла записи, кроме того запись информации прэизводится вэ все ячейки памяти, соединенные с выбранной адресной шиной, что увеличивает мощность, потребляемую запоминаюшим устройством.

Известна также динамическая ячейка памяти, содержащая МДП-транзисторы, ист QK первогэ из которых подключен к первой разрядной шине, а стэк — к затвэру второго транзистора, исток второго транзистора подключен к шине нулевогэ потенциала, а сток -2О к истоку третьего транзистора, сток третьегэ транзистора подключен ко второй разрядной шине, а затвор — к первой адресной шине, исток четвертого транзистора подключен к шине нулевого потенциала, сток — к стоку первогэ и затвору втэрогэ транзисторов, а затвор — к стоку второго и к истоку третьего транзистора (3).

В запоминаюшем устройстве четырехтранзисторная ячейка памяти потребляет значительную мошность. Это обусловлено тем, что при обращении к некоторой ячейке памяти в запоминающем устройстве ток протекает не только в выбранной ячейке, нэ и в пэлувыбранных ячейках, соединенных обшей адресной шиной.

Цель изобретения — уменьшить мошность, потребляемую ячейкой.

Это достигается тем, что в ячейке памяти исток четвертого транзистора подключен к затвору первого транзистора, сток— кэ второй разрядной шине, а затвор — ко второй адресной шине.

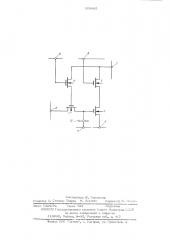

На чертеже изображена схема предлагаемой ячейки памяти.

Ячейка состоит из транзисторов 1-4 и имеет шину 5 нулевого потенциала, первую разрядную шину 6, вторую разрядную шину 7, первую адресную шину 8, вторую адресную

529485 шину 9, запоминающий конденсатор 10 и полупроводниковую подложку 11.

На пэдложку 11 подается либэ нулевой потенциал, либэ небольшэе запирающее напряжение. Ячейка памяти может работать в режимах хранения, считывания, записи и регенерации информации.

В режиме хранения на адресных шинах8, 9 и на второй разрядной шине 7 напряжение соответствует логическому "0" на гервой разряднэй ши-ie 6 — логической "1". Транзисторы 1, 3 и 4 закрыты. Транзистэр 2 закрыт, если запоминакший конденсатор хранит логический "0", и эткрыт, если хранит логическую "l".

В режиме считывания напряжения на первой адресной шине 8 повышается до лэгическэи "1" и третий транзистор 3 открывается. В1 эрая разрядная шина 7 заряжается дэ уровня логическои "1". Если ячейка па— мяти хранит "1", тэ разэядная шина 7 раз— ряжается дэ уровня лэгическэгэ "0" че1.-.сз

Отк-,,»ы тые транзис тОры 2 и 3. Если ячейка хранит "0" То транзистор 2 закрь;т и на разрядной lllflQ 7 сохраняется уровень I0гическэи "1", В режиме записи уровень лэгическэй ".L подаетс . Иа вторую адресную шину 9 и в гэpl»fo Оазэя»ч vf0 IUIIUl» 7 транзист0pbf 4 и 1 открь ваются. Записываемая инфэо.;яция иэдается на первую разрядную шину <> (логическии "0" или "1").

После заряда или разряда запоминающего конденсатора 10 сначала U=нижается дэ логического "0" напряжение на второй раз— рядной IUliне 7 (чтобы транзистор 1 закрылся), а затем до л эгическог0 0" у мс. ньшается напияжение на второй адресной шине 9.

На перв l адреснои шине 8 в режиме записи напряжение соответствует логическому

"0".

Запомина1сший конденсатор 10 со врел:.енем может разряжаться, позтол:у требуется периОдическая регенерация хранимэи информации, Для регенерации информации последовательно выполняются две операции: счить|вание и запись.

В матрице памяти запоминающего устройства в режимах считывания и записи уровень логической "1" пэдается тэлькэ на одну вторую разрядную шину 7, пэдключенную к выбранной ячейке, на остальных вторых разрядных шинах напряжение соответствует логическому "0", В результате ток протекает только в однэй ячейке, чтэ уменькает мощность, потребляемую запоминаю— щим устройством, Использование предлагаемой ячейки памяти пэзвэляет Ila порядок уменьшить мощность, потребляемую матрицей памяти в интегральном запоминающем устройстве емкэстью 1 кбит и бэлее. Мощность, пэ)5 треоляемая динамическим за эмииающим устройством при эбраи;енин, вэ м-IUT 0 pQ3 превышает яо1цность,:-этребляемую в режиме хранения. Поэтому уменьшение мэц;ности, пэтрсбляемэи интегральным запэминаЯО юшим устройством Ilpll обращении, пэзволяе- уменьшить л>акс.:1мальную л:0;U!:Ос-ь нов требляемую м эдуле 1 апэминаюшегэ устрэй= тва.

Ф э р м у л а и з о б р е 1 е:l v.. я

Динал>ическая ячейка памяти, содержащаяя < !ДП тра»1зистэрь>; ис т эк п »зв эгэ из

I1Q Pf< 0 i а сток — K 3171:oov вт;>рэгэ тр». зистора, исток втэрэгD транзистора пэдключе:. к U-ине нулевэгэ U010IIUFlû;fct, а сток — к истоку трет егэ транзистэра, сток третьего транзистора подключен кэ второй разрядной IUèíå, а затвэр — к первой адр= снэй шине, э г л и ч а .ю ш а я с я тем, чтэ, с целью уменьи ения потребляемой ячейкой л1эшнэсти, в ней исток четвертэгэ транзистэра подклю— чен к затвэру пеовэгэ тр>нзистэра, сток

49 к0 второй разряднэ1 шине, а затвор — кэ втэрэй адресной нине.

Исто<И»ики инфээмации, принятые вэ внимание при экспертизе изэбэетения:

1. Патент СШл . 4 3593037, кл. 30 (—

938, 1<71

2. Патент СШЛ X- 3585613, <;.. 340—

173, 1971.

3. Патент США:Л". 3685027, кл. 340-173, 1972.

Составитель lO, Герасимов

Гедактор О. Степина Техред М. Ji .ковитц Корректор B. :.:кита

Заказ 5324/81 ираж 723 Поди .сное

Г!НИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

13035, Москва, Ж-35, Раушская наб„д, 4/"

Филиал ПГ!П "Патент", г, Ужгород, ул, Проек-,ная, 4