Оперативное запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

Оп ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДИТИ1ЬСТВУ (11) gggyg() (61) Дополнительное к авт. свид-ву (22) Заявлено 01.08.75(21) 2160549/24 с присоединением заявки № (23) Приоритет (43) Опубликовано25.09.76,Бюллетень ¹ 85 (45) Дата опубликования описания 07.12.76 (51) М. Кл."5 11 С 29/00

Гасударственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УД К 68 1.32 7.6 (088.8) (72) Автор изобретени»

А. й. дроля (71) Заявитель (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО

С САМОКОНТРОЛЕМ

Изобретение относится к облас ти запоминающих устройств.

Известно оперативное запоминающее устр ойс тв о с сам ок эн тр олем, с оде ржа шее у злы для эпределения случаев, когда операции в памяти связаны с адресным обращением к ячейкам, KDT ýðûå являются дефектными 1 При этом обрашение переадресэвывается к резервным ячейкам, имеющимся в главной памяти. Имеется ассоциативная память, ко- )p торая содержит секцию аргумента для хранения адресов дефектных ячеек главной памяти и секцию функции для хранения адреса замещения для каждой дефектной ячейки. Когда ассоциативная память определяет, что адресуемая ячейка главной памяти являег— ся той ячейкой, адрес которой хранится в секции аргумента ассоциативной памяти, ro на эснэвании адреса секции функции обращение переадресовываегся к ячейке замеше- gp ния, соответствующей данной дефектной ячейке. Этим достигается пропуск дефектных ячеек памяти. При любых отказах ячейки главной памяти, в том числе и при однэкратных ошибках, неисправная ячейка заменяет- 2б ся полностью на исправную, что ведет к завышенным затратам на резервное оо оруд эвание.

Известнэ также оперативное запоминающее устройство с самоконтролем, содержащее адресный запоминающий блок, подключенный к блокам кодирования и декэдирэвания и основному ассоциативному запоминающему блоку, и блэк управления (2).

Такое оперативное запом инаюшее устрой— ство имеет значительный объем разрядного блэка, так как избыточные разряды имеют все без исключения ячейки адресного запоминающего блока независимо от гэгэ, исправны эни или неисправны, какого вида неисправности в них и замещаются ли они ячейками асс эциа тивн ог э зап эмин аюше г э блока.

Цель изэбретения — упрэсгить устройство, Эгэ достигается тем, что устройство содержит дополнительный асс эциативный блок, входы котэоого подключены соответ— ственнэ ко входу адресного запоминающего блэка и выходам блока кэдирования и блэка

529490 управления, а выход — кз входу блока декодирования.

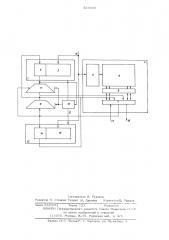

Ба чертеже приведена структурная схема предлагаем згэ эперативнзго запзминаюшего устройства с самоконтролем.

Устрэйствз содержит дополнительный: ассзциативный запэминающий блок 1, который имеет функциональную часть 2 для размещения изоыточных разрядов при кэдирэвании инфзрмации кзрректируюшим кодом и аргументную часть 3 для запоминания адресов отказавших ячеек адресног з запоминаюшегэ блэка 4, состоящего из адреснзго блэка 5, блэка 6 =- апэминающих матриц, регистра слзва 7 и усилителей считывания — записи

8, УсIðîéñòBo содержит также блоки кодир=вания 9, управления 10 и декздирэвания

11. К выхэду 12 блэка 10 подключен оснэвнэй ассоциативный запоминающий блэк 13, который имеет функцизнальную часть 14 для размещения полного слова информации зтказавшей ячейки блока 4 и аргументную часть

15 для запоминания адреса зтказавшей ячейки. Выхзд блока 1 подключен ко вхзду блэка 11, а входь". — сззтветственнз к выходам блоков 9, 10 и входу 16 адресного запоминающего блэка 4, имеющего входные 17 и выходные 18 шины.

Устройствз работает следующим образом.

В и;,эцессе стирания содержимзгз адресногэ запоминаюшегз блэка 4 или в паузах между внешними обращениями блок 10 осуществляет контроль исправцости ячеек злока 4. При обнаружении неисправности в какой-лиоэ ячейке блок 10 зпределяет тип ошибки и в зависимости от характера неисправности (однократной илп м н л-экра тн ой адрес неисправнзй ячейки фиксируется в аргументнзй части 3 или 15 дополнительного 1 илп оснэвнзгз 13 ассоциативных запоминающих блоков.

При внешнем обращении к оперативному. запоминающему. устройству по адресу, установленному на входе 16, происходит здновременное обращение как к запоминающему блоку 4, .так и к ассзциативным запев минающим блокам .1 и 13.

При выпо ItiE íèè операции записи информация с входных шин 17 заносится в регистр 7 слова и через усилители 8 считывания — записи записывается в блок 6 за— поминающих матриц пз адресу, зафиксирзванному в блоке 5, Если при ассоциативном поиске в блоке 13 збпаружен адрес обращения, информация с регистра 7 записывается в функциональную часть 14 блэка 13.

Если этот адрес обнаружен при ассэциативнзм пэиске в блоке 1, информация кэдируется блоком кодирования 9. Закодированная кэрректируюшим кодом информация записывается в блок 4 и функциональную часть 2 блока 1 (избь;точные разряды). При выполнении операции чтения из эперативного загэминающегэ устройства происходит выборка содержимого блока 6 на регистр 7, Однз © временно происходит ассэциативпый поиск в блоках 1 и 13, Если в блзках 1 и 13 такого адреса нет, значение слова на регистре 7 является истинным и выдается на вь:хэдные шины 18. Если в блэке 13

l5 есть такой адрес, содержимое ячейки блэка, связанной с этим адресом, выдается на ре— гистр 7 и далее на шины 18. Если такзй адрес есть в блэке 1, тэ содержимое блэка

1 и ячейки блока 4 поступает на входы блз— щ ка 11 декодирования. Блэк ll декэдирует информацию, исправляя значения дефектных разрядзв, фиксирует информацию на реги— стре 7, и вернэе значение информации вы— дается на шины 18. щ Предлагаемое устройствз исправляет засчет кзрректируюшегэ кзда все эдинзчные зшибки, а за счет замены неисправных ячеек — и многократные ошибки. Объем ассз— циативных запоминающих блоков 1 и 13 выЭ бирается с учетом требуемьix характеристик надежности вссгз устройства и статистики распределения ошибзк, З, Ф э р м у л а и з о б р е т е н и я

Оперативное запоминающее устрэйствэ с самоконтролем. сэдер кащее адресный загомпнаюший блок, подключенный к блокам кодирования и декодирования и основному ассо46 циативнэму заг оминаюшему блоку, и блок управления. э т л и ч а юш е е с я тем. чтэ, с целью упрощения устройства, оно содержит дэпзлнительнь и ассоциативный блок, входы которэго подключены соответственно ко входу адресного зацоминаюшего блока и вь хэдам блока кодирования и блэка управления, а выход — кс входу блока декодирования.

Источники информации, принятые во вни—

5© маяие при экспертизе:

1. Патент С1ЫЛ ¹ 3633175, М. Кл. 9 06

F 1111/ 0000, 1972.

2. Авторское свидетепьство CCCF- №368647, М.кл. G 11 С 15/00, 1974.

Составитель В. Рудаков

Редактор О. Стенина Техред М, Дикович Корректор Б. Микита

Заказ 5324 8 1 Тираж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров (. ((:Р по делам изобретений и открытий

1 1 3035, М осква, Ж- >5, Раушскяя наб., д. 4(5

Филиал ПГ Г1 "Па тен r", г. Ужгород. ул. П р оектна н, 1