Цифровой многоустойчивый элемент

Иллюстрации

Показать всеРеферат

I л

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социапистических

Респубпик (») 52956 3

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 23 05 75 (21) 2136598/2! с присоединением заявки № (51) M. Кл.е

Н 03 К 29/00//

//H 03 К 5/20

Государственный комитет

Совета Министров СССР

ns делам изобретений и открытий (23) Приоритет (43) Опубликовано 25.09. 76. Бюллетень № 35 (53) УДК 681.325.3. (088.8) (45} Дата опубликования описания10.03.77.

Ю, И. Кузьмин (72) Автор изобретения

Львовский филиал Всесоюзного научно- исследовательского института физико-технических и радиотехнических измерений (71) Заявитель (54) ЦИФРОВОЙ МНОГОУСТОЙЧИВЫЙ ЭЛЕМЕНТ

Изобретение относится к радиотехнике и может быть использовано в устройствах вычислительной техники.

Известен цифровой многоустойчивый элемент, содержащий последовательно соединенные дели- 5 тель — ограничитель, накопитель, зарядный вход которого соединен с выходом усилителя — ограничителя, транзисторный компаратор, соединенный базой с выходом накопителя, а коллектором — с входом элемента задержки, разрядное устройство, !О выход которого соединен с разрядным входом накопителя, источник напряжения компарации (1).

Однако этот элемент имеет сравнительно невысокую надежность и узкие фукцнональные возможности. 15

Цель изобретения — повышение надежности и расширение функциональных возможностей элемента.

Для этого в цифровом многоустойчивом элементе между эммитером транзисторного компара- 20 тора и источником напряжения компарации дополнительно введены последовательно соединенные и-транзисторных компараторов, n — элементов задержки и и — разрядных устройств.

Эмиттер каждого прсдыдугцсго транзисторного 25 компаратора соединен с базой каждого последующего,к базе каждого транзисторного компаратора подсоединен дополнительный конденсатор.

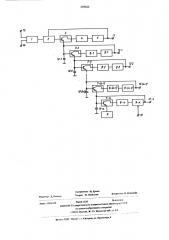

На чертеже изображена структурная электрическая схема цифрового многоустойчивого элемента

Он содержит последовательно соединенные усилитель †ограничите 1, накопитель 2, зарядный вход которого соединен с выходом усилителя — ограничителя 1, транзисторный компаратор 3, соединенный базой с выходом накопителя 2, а коллектором — с входом элемента задержки 4, разрядное устройство 5, выход которого соединен с разрядным входом накопителя 2, источник напряжения компа рации 6.

Между эмиттером компаратора 3 и источником напряжения компарацни 6 включены и последовательных цепей, состоящих иэ последовательно соединенных компараторов 7=-1 — 7 — п,элементов задержки 8=1 — 8=п и разрядных устройств 9=-1—

9=п соответственно.

Входы разрядных устройств 9=1 — 9 и соеди иены с входами компараторов 7=-1 — 7=-n,ê базам которых подключены конденсаторы 10 1 — 10=n, соответственно. Выходы разрядных устройств 5, 529563

9=1 — 9=n подключепы к выходам 11 и 12=1—

I 2=n соответственно.

11ифровой многоустойчивый элемент раоотает следующим образом.

Пусть в исходном состоянии все конденсаторы

10=1 — I0=-п разряжены до нуля. Напряжение на выходе источника напряжения компарации 6 установлено на уровне, расположенном между значениями соответствующих заданных уровней.

В момент поступления первого счетного импульса на вход 13 или 14 напряжение на выходе накопителя 2 дискретно увеличивается до некото рой величины ь U. При этом в схеме протекают слелующие процессы. Открывается компаратор 3 и запускает элемент задержки 4. Одновременно начи нается заряд конденсатора 10=1 через компаратор

3. В результате заряда конденсатора 10=1 открывается компаратор 7=1 и запускает элемент задержки 8=-1. Начинается заряд конденсатора 10=2 через компаратор 7-"-1. И так далее.

Компаратор 7=n останется закрытым, так как по принятым начальным условиям к его эмиттеру приложен з;; .;Раюший потенциал источника напряжения компарации 6.

Так как коэффициент передачи транзисторных компараторов от базы к эмиттеру близок к единице, заряд конденсаторов 10=-1 — 10=-и происходит до напряжения, приблизительно равного л0. Задним фронтом импульсов элементов задержки 4, 81 — 8= (и — 1) запускаются соответственно разрядные устройства 5, 9=1 — 9=(n — 1) и разряжают конденсаторы 10=1 — 10=-(и — 1) приблизительно до нуля, а напряжение на конденсаторе 10=n равно в О.

В момент поступления второго счетного импульса все описанные процессы повторяются, за исключением того, что компаратор 7=(n — 1), как и компаратор 7=n остается закрытым. Таким образом, к моменту поступления третьего счетного импульса до напряжения., равного U оказываются заряженными конденсаторы 10=(n — 1) и 10=n. Остальные конденсаторы разряжены до нуля. Последовательным отключением компараторов 7=-1

7=n конденсаторы 10=1 — 10=п оказываются заряженными до напряжения ь U. 3a время следующего цикла конденсаторы 10=1 — 10=n заряжаются до напряжения, равного 2 е, U . И так далее, пока они не зарядятся до требуемого напряжения,, заданного источником напряжения компарации 6.

Для установки схемы в исходное состояние необходимо подать короткий импульс на вход 15 разрядного устройства 9=n.

Перевод многоустойчивого элемента в исходное состояние можно осуществить импульсом, подаваемым на один из входов усилителя — ограничителя 1 после того, как все конденсаторы 10-1 — 10*=п будут заряжены до требуемого напряжения.

Формула изобретения

Цифровой многоустойчивый элемент содер20 жащий последовательно соединенные усилитель — ограничитель, накопитель, зарядный вход которого соединен с выходом усилителя — ограничителя, тран;зисторный компаратор, соединенный базой с выхо. дом накопителя, а коллектором — с входом элеЛ мента задержки, разрядное устройство выход которого соединен с разрядным входом накопителя, источник напряжения компарации о тл и ча ющи и си тем, что, с целью повышейия надежностИ и расширения функциональных возможностей, в

30 нем между эмиттером транзисторного комларатора и источником напряжения компарации дополни тельно введены последовательно соединенные и транзисторных компараторов п элементов задержки и и разрядных устройств, причем эмиттер каждого предыдущего транзисторного компаратора соединен с базой каждого последующего, к базе каждого транзисторного компаратора подсоединен дополнительный конденсатор.

Источники информации, принятые во внимание при экспертизе;

1, Авт. св. СССР У 330556, М. Кл. И 03 К 29/00, 24.11.72 (прототип) .

529563

Составитель Ю. Еркин

Техред М Левицкая

Корректор Н. Ковалева

Редактор Д. Пинчук

Заказ 5334/109

Филиал ППП "Патент", г, Ужгород, ул. Проектная, 4

Тираж 1029 Подписное

011ИИПИ Государственного комитета Совета Министров СССР но делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5