Устройство для синхронизации по циклам

Иллюстрации

Показать всеРеферат

O ll И С А Н И Е <и> б вббб

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЙТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 09.06.75 (21) 2143969/09 с приСоединением заявки №вЂ” (23) Приоритет (43) Опублнковано25.09.76.Бюллетень №35 (45) Дата опубликования описания 27.12.76 (51) М. Кл.з

Н 04 3 3/06

Н 04 L 7/08

Государственный комитет

Совета Министров СССР пп делам изобретений и открытий (53) УДК 621.394. . 662. 2 (088. 8) (72) Авторы изобретения

Г.В. Коновалов, 3.И. Лангуров и Г.С, Рудская (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО LIHKJIAM

Изобретение относится к технике обработки информации в дискретных системах, а именно к технике осуществления синхронизма по циклам в системах с цифровыми методами модуляции аналоговых сигналов, а так- g же в системах передачи дискретных сообщений.

Известными устройствами являются устройства цикловой синхронизации,. с помощью которых синхронизм по циклам в дискретных щ многоканальных системах достигается обычно путем фазирования приемных распределителей каналов на оконечных и помежуточных станциях(1j . Для обеспечения возмож ности такого фазирования в состав переда- 15 ваемого группового сигнала системы вводят синхросигнал какого-либо вида, представляющий собой периодическую последовательность синхрогрупп, передаваемых на одних и тех же импульсных позициях (синхрони- оО зациях) в каждом цикле.

Наиболее совершенным является устройство синхронизации по циклам, содержащее дешифратор синхрогруппы, выходы которого подключены через анализирующий узел синк- 25 рогруцпы первого вида к входу первого элемента ИЛИ, к входу анализирующего уз» ла синхрогруппы второго вида, а через вто рой элемент ИЛИ, узел управления — к вхо» ду делителя тактовой частоты, а также последовательно соединенные решающий узел и узел фазирования приемного распределителя (2), Однако при передаче синхросигнала из синхрогрупп одного вида, периодически повторяющихся в каждом цикле, из символов

«молчащих» каналов возможно образование псевдосинхрогруппы, периодически повторяющейся в каждом цикле подобно синхрогруппв синхросигнала. Обнаружение устройством цикловой синхронизации в процессе поиска состояния синхронизма такой псевдосинхрогруппы может привести к длительной потере циклового синхронизма, что приводит к увеличению времени вхождения в синхронизм по циклам.

11елью изобретения является уменьшение времени обнаружения синхрогруппы.

Для этого введены третий элемент ИЛИ, узел коммутации, узел формирования сигна529565 лов управления, при этом выход делителя тактовой частоты подключен к входам узла коммутации, а через узел формирования сиг налов управления, узел коммутации, анализирующий узел синхрогруппы первого вида, третий элемент ИЛИ вЂ” к соответствующим входам узла формирования сигналов управления, решающего узла и узла фазирования приемного распределителя, причем второй выход узла коммутации подключен через анализирующий узел синхрогруппы второго

Р6 вида, соединенный с узлом формирования сигналов управления, и первый элемент

ИЛИ к вторым входам узла управления и решающего узла.

Таким образом, время обнаружения синхросигнала, передаваемого в вице последовательности чередующихся синхрогрупп gBvx видов, уменьшается, так как осуществляетимо ависимый поиск этих синхрогрупп.

26

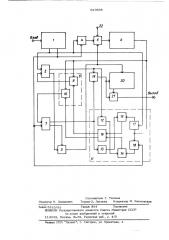

На чертеже дана структурная электрическая схема устройства.

Устройство синхронизации по циклам со— держит дешифратор 1 синхрогруппы, один выход которого подключен через анализирующий узел 2 синхрогруппы первого вида к входу первого элемента ИЛИ 3, а через второй элемент ИЛИ 4, узел управления 5 - к ьходу делите.ля 6 тактовой частоты, второй выход дешифратора 1 подключен к второму входу второго элемента ИЛИ

4 и к входу анализирующего узла 7 синхрогруппы второго вида, выход делителя

6 подключен к входам узла коммутации 8, состоящего из элементов И 9 и 10, а через узел формирования 11 сигналов управления, состоящий из элементов задержки

12, 13, элементов ИЛИ 14 и 15, триггера

16 и элементов И 17 и 18, узел коммутации 8. анализирующий узел 2-к соответствующему входу узла формирования 11 и дополнительно через третий элемент ИЛИ

1 9 — к соответствующим входам последовательно соединенных решающего узла 20 и узла фазирования 21 приемного распределителя,. причем второй выход узла формиро вания 11 подключен через узел коммутации

8, анализируюгций узел 7, соединенный с узлом формарованич 11, и первый элемент

ИЛИ 3 к вторым входам узла управления

5 и решающего узла 20. Узел формирования 11 соединен также непосредственно с дешифратором 1, анализирующим узлом 7 и вторым входом третьего элемента ИЛИ 19

Вход дешифратора 1 и выход узла фазироввния 21 являются соответственио входом и выходом устройства, вход 22 узла управления

5 является входом импульсов тактовой часготы.

Устройство работает следующим образом, 69

Импульсно-кодовый сигнал с входа устройства поступает на дешифратор 1, на вы ходе которого образуются сигналы откликов как на синхрогруппы, так и на кодовые группы информационного сигнала, сходные с сиихрог руппами.

Выпеленные дешифратором 1 сигналы поступают через второй элемент ИЛИ 4 на вход узла управления 5, соответствующий запуску делителя 6. Г1ри регулярном поступлении импульсов тактовой частоты с входа

22 через узел управления 5 на вход делителя 6 на его выходе формируется последовательность импульсов опробования, длительностью в период тактовой частоты и следующих с частотой циклов.

В установившемся режиме отклик на синхрогруппу первого видa с выхода дешифратора 1 поступает на вход анализирующего узла 2 в тот момент, когда на другой его вход через открытый элемент И 9 узла коммутации 8 с делителя 6 приходит импульс опробования. В этом случае сигнал повторения с выхода анализирующего узла

2 через третий элемент ИЛИ 1 9 проходит на вход, записи фиксации состояния синхронизма в решающем узле 20 и на вход узла фазирования 21. Кроме того, сигнал повторения с выхода анализирующего узла 2, задержанный на элементе задержки 12 узла формирования ll, проходит элемент ИЛИ

l4 и переключает триггер 16 в положение, разрешающее в следующем цикле прохождение ймпульса опробования с делителя

6 через элемент И 10 узла коммутации 8 на вход. анализирующего узла 7 и запрещающее через элемент И 9 ча вход анализирующего узла 2, В следующем цикле в результате появ— ления на выходе дешифратора 1 отклика на синхрогруппу- второго вида аналогично происходит переключение "ðèããåðà 16 в исходное положение сигналом повторения с выхода анализирующего узла 7 через элемент задержки 13 и элемент ИЛИ 15, т.е. происходит подготовка устройства к приему в следуюшем цикле синхрогруппы первого вида.

В случае потери синхронизма устройством (отсутствие ча выходе дешифратора 1 ожидаемого отклика) на выходе подготовленного -. опробованию анализирующего узла

2 или 7 формируется сигнал ошибки, который через первый элемент ИЛИ 3 поступает на вход сброса решающего узла 20 и на вход узла управления 5, запрещающий поступление импульсов тактовой частоты на вход делителя 6, т.е. делитель останавливается в положении, соответствующем моменту опробования, а элементы И 17 и 18 остаются открытыми.

529565

5 Я

В Сежн.". -.= поиска,1еавый ке ч 3 QTKRI1 ков на любушка: синхрогруппу н н ее имитацию импульсами инфармационно1 о сигна;::а,. появившийся на выходе дешифратср» 1, пас туп ает на с О ответствующий анализн аующий узел 2 или 7 и на запуск дегите;..я 6.

3тот отклик ппаходцт соатв етс Г31 юшче элементы И 17 либс 18 и элемент.- . ИЛИ

14, либо 15 узла формирования 11 II про= изводит установку триггера 1 6 в ;толожение, Открыва ашее зле; ент И 9 либо 1С узла коммутации В, пропускающий сигнал с делителя 6 на тат анализируюшии узел

2 и 7, на вход которого пришел Отклик с дешифратора 1.

Образующийся сигнал повторения, состветствуюши! дешифоуемой синхрагр т1-;е, через третий элемент ИЛИ 1 9 поступает на вход записи решающего узла 20, КрОме Tot О.:Зпепжанчый сигнал J0BT .» рения чар . ; со. тве: с Г и," Ошии,„1ем;=нт И (И

14 либо 15 в узле формирования 1 осу-ществляет пере-.;.;.>-с--. тригге0а 16 в состоя-. ние, в котором устройство готово к t:риему в следуюп1е:„»!II. г -.i дру1-Ой синхга1- p, t пы, После,иксации ссстояния синхраннзма реша|а:инм ° -; —,.....; .;-.:- -О-.а

p0BQItIIB, l Ка i ..".!". ОткрЫТ . (-,Ка уст ci-. новившемся oc> ::.!;. IÐ,. Наст у1ает 1 м1 ульс для пОдсГрОЙки 0 пэ .мнс : ра .Нведе."Г" Геля сР О 0 v у . 1 8 и,з 0 б 0 е," H u содержащее 0 э. ;t,,р*, )0, ; t;; ; 00 "у!,, дь. которого подключеньг через анализирующий узел синхрогруппы первого вида к входу первого элемента ИЛИ, к входу анализи ру.ощего узла синхрогруппы второго вида, » через второй элемент ИЛИ, узел управления — к входу делителя тактовой частоты, а также последовательно соединенные решающий узел и узел фазирования приемного распределителя, о т л и ч а ю ш е ес я тем, что, с целью уменьшения времени обнаружения синхрогруппы, введены третий элемент ИЛИ, узел коммутации, узел формирования сигналов управления, при этом выход целителя тактовой частоты подключен к входам узла коммутации, а через узел формиразания сигналов управления, узел коммутации, анализирующий узел синхрогруппы первого вида, третий элемент ИЛИ вЂ” к соответствующим входам узла формирования сГГ-:алов управления, решающего узла и узла фазированияприемного распределителя, причем второи выход узла коммутации подключен через анализирующий узел синхрогрупГъ1 второго вида, соединенный с узлом формирования сигналов управления, и перHbtII элемент ИЛИ к вторым входам узла управления и решающего узла.

Источники информации, принятые во внимание при экспертизе:

Гуревич B. З. и др. Импульсно-кодовая модуляция в многоканальной телефонной связи. М., "Связь", 1973, с.240.

2. Патент ФРГ ¹ 1142921, класс 21а

49, 1 963 (прототип).

529565

Составитель Г. Теплова

Техред О. Луговая Корректор Н. Золотовская

Редактор Н. Данилович

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Заказ 5223/ &1. Тираж 864 Подписное

ЯНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5