Запоминающее устройство

Иллюстрации

Показать всеРеферат

союз советскня Q П И (Д Н И Я

Социалмстическ н

Республик

ИЗОБРЕТЕНИЯ (61) Дополнительное к ант. свид-ву(22) Заявлено 24.02,7о (21) 2107872/24 (51) М. Кл.

6 11 С 11/40 с присоединением ааянки №"

Гасударственный намнтет

Совета Мнннетрее СССР ее делам нзабретеннй к открытий (23) Приоритет „ (43) Опубликовано30,09.76.Бюллетень ¹ 86 (4Ь) Дата опубликования описания,07.11 76 (53) УДК 628, 3 2 7, 6 (О88,8 ) (72) Авторы изобретения

Г. Л. СоФийский и Р В.,Смирнов (71) Заявитель (54) ЗАПОМИНАЮШЕЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники.

Наиболее близким техническим решением ,является запоминающее устройство, содер,жащее элементы намести, подключенные через 5 дешифратор к соответствующим выходам пер,вого и второго регистров адреса, входы ко торых подключены к ходовым шинам, шину разрешения дешифрации и шину запуска.

Недостатком запоминающего устройства является невысокое быстродействие, что свя.

;:зано с задержкой Г между моментами пода.чи на первые w вторые адресные шины полупроводниковых элементов памяти соответственно старших разрядов кода адреса и т5 сигнала выборки. Задержка характерна для полупроводниковых элементов памяти и обусловлена большим временем расшифровки anреса внутри полупроводниковых элементов

; тта мяти. 20

Белью изобретения является повышение быстродействия устройства.

Поставленная пель достигается тем, что устройство содержит третий и четвертый ре1гистры адреса, схему сравнения, двухканаль25 ц ьгй переключатель, элемент задержки и гер, причем входы третьего и четвертогт регистров адреса соединены с одноименн ли входами первого регистра адреса, е выходы через схему сравнения подключены к управляющему входу двухканального переключателя, другие входь. которого один непосредственно, а другой — через элемент задержки, соединены с шиной разрешения дешифрации,, выход двухканального переключателя подсое;динен к управляющему входу дешифратора, ) управляющие входы третьего и четвертого регистров адреса через триггер подключены к шине записи.

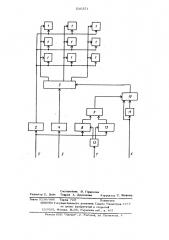

На чертеже приведена блок-схема устроФгтва, Устройство с одер>кит полулроводниковые элементы I памяти, первый регистр 2 ад;

jpeca, дешифратор 3, второй регистр 4 ад-!

jpeca, кодовые шины 5 адреса, штпту 6 раз решения дешифрации, шину 7 запуска, третий

1 регистр 8, схему 9 сравнения, двухканаль! ный:,переклточатель 10, элемент 11 задерж ки, триггер 12, четвертый регистр 13.

Э устро ра ойство ра ает сл работ ет следуюшим образом тов памяти 1 уже расшифрован в и е

По кодовым шинам 5 agpeea пос купает р об ащении), причем и первый рз Поскольку при оаботе в составе щц и полный код адреса, причем гисч з 2 адреса заносятся осятся старшие разряды в р«е других применений для запоминаюше., второй Ре"ис р адре 5 го устройства характерным является носл

«ода адреса, а во второ ре заносятся младшие ра ня ДОватЕЛЬная смена адресов, что соответс В зрядьт кода адреса ет изме ению старших разрядов кода адреса иовременно старшие разря тные в"о"ь ребров через 2 обрашений к звпомннаюшемуустрй пос гупают на одноименные ,9 и 13. мпу пу " " " стау (к-разрядность Второто регис,а а ресаК то В 2 обратцениях старшие разря ребрасывае у; е бра; его s логическое состояние, ды предьтдутцего и текушего кодов будут против ополо тр ер совпадать ив следовательно, сигнал Выборки буд т Goc ó ã на вторые адресные шины по.

8 заВФнрим

Лупроводниковьтх элементов памяти на Вре

35 . Выбирается один из я один из регистров 8 или 13, в 1мя 2 раньше, чем в известном устройстве.

2 +1 кот ый в данный момент Времени заносят Только В одном обрашенин () старся зтаршие разряды кода адреса, При этом шие разряды предыдушего и текушего кооцотояиие одного из регистров 8 или 13 не дов адреса будут различаться и, следоваИЗМЗ меняется и на нем сохраняются старшие тельно, сигнал выборки будет поступать на х едыдушего кода адреса. Состоя вторые адресные шины полупроводнико ущ регистров 8 и 13, г,е. старшие разря- элементов памяти незадержанным, т.е, такы е душего и текушего кодов адреса, же, как в известном устройстве.

b авнивается схемой сравнения 9, Резуль- Так как задержка, например, для

P и МОП-титат сра не. в сия поступает на управляюший

И лупровопниковых элементов памяти М в т 2ОО вход двухканального переключателя 10, на па может достигать величины, равных угие два входа которого по шине 6 раз- - 400 нсек, при времени цикла обрашения решения дешифрации пос.тупает сигнал раз«полупроводниковых элементов памяти 7 иф ции При этом на один из - 900 нсек, то изобретение позволяет совходов двухканального переключателя 10 кратить время цикла обрашения запоминаюоютнал разре азрешения поступает непосредствен- шего устройства„а также время выборки а 30-50 %. йо, а на другой < через элемент задержки 11, информации примерно на на кбтщюм м он задерживается на ВремЯ 7 ° Таким образом, изобретение позволяет

В ос ги от результата сравнения сос- сушественно повысить быстродействие заВ зависимос ги от рез тояния регистров 8 и 13, T.å, от несовпаде- ® поминаюшего устройствв. ния или совпадения старших разрядов кода а еса ч ез двухканальный переклточ аадреса, ер двухк

Запоминаюшее устройство, содержа нее тель 1О на управляюший вход дешифрато

% ржанный элементы памяти, подключенные чь,ез дера 3 поступает соотве гственно задержанны езадержаиный шифратор к соответствуюшим выходам перна элементе задержки 11 или незадержаины „

Со етствен- вого и второго регистров ащзесв, входы косигнал разрешения дешифрации. ответственторых подключены к кодовым шинам, шину но на элометтты памяти 1 с выходов дешиф3 будет поступать задержа1шы или туп за жанный и т разрешения дешифрации и шину запуска, о т ратора уд л и ч а и ш е е с я тем, что, с целью понезадержанный относительно момента поступления ста ших аз ядов кода адреса сигна а адреса сигнал Вышения быстродействии устройства, оно со ленни ст р р р держит третий и четвертый регистры адре-!

Выбо ки элементов памяти 1. .Выборк са, схему сравнении, двухканальный переПри несовпадении старших разрядов пре- ключатель, элемент задержки и триггер, прин тек шего кодов адреса на вто- чем входы третьего и четвертого регистров рые адресные шины элеь ины элементов памяти 1 по- адреса соединены с одноименными входами

ЬВ деется задер жанный сигнал выборки т.е, первого регистра адреса, а выходы через

° ъ также, как и в известном устройстве. При схему сравнения подключены к управляюшесовпадении же старших разрядов предыдуше- му входу двухканального переключателя, го и текущего кодов адреса на вторые аа- другие входы которого оспин непосредственресные входы элементов памяти подается но, а другой - через элемент задержки соесигнал вы орки на вреь ра б на время С раньше чем в динены с виной разрешении дешифрации, выизвестном устро стве, ойстве поскольку не ъебует ход двухканального переключателя подсоеся время на расшифровку адреса Внуч ж еле- динен к упрввлякшему входу дешифрвторв, а ментов памяти 1 (старшие разряды кода упрввлятошие входы третьего и четвертого адреса хранится на ттерзом регистре ащзе- ® регистров адреса черезтриттер подключены са, и, следоватслыто, адрес Внутри элемен- к шине записи.

Составитель В. Гардонова

Pen8KTop E. Дайч Текред А. Демьянова Корректор С. 13tWwap

Заказ 5235/6О6 Тираж 723 Подлисное

ИНИИПИ Государственного комитета Совета Министров С4,СР но делам изобретений и открытий

3.13035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППИ "Патент, г. Ужгород, ул. Проектная,