Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

Союз Советских

Се „иалистических

Республик

ОП ИКАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (и) 530425 (И) Дополнительное к авт. свид-ву— (22) Заявлено05.05.74 (21) 2022961/09 с присоединением заявки № (23) Приоритет (43) Опубликовано30.09.76.Бюллетень № 36 (45) Дата опубликования описания 09.11.76 (51) М. Кл,>

Я 03 7 3/45

Гасударственный нвннтет

Свввтв Мнннстрав СССР вв делан нэеврвтеннй н отнрытнй (72) Авторы изобретения

В. П. Гузий и B. Г, Шульга (71) Заявитель (54) ДИФФЕРЕНБИАЛЬНЫЙ УСИЛИТЕЛЬ

Однако известные дифференциальные усилители имеют значительный дрейф нуля.

Бель изобретения - уменьшение дрейфа нуля.

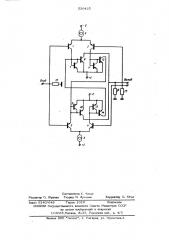

Для этого в дифференциальном усилителе, содержащем первый и второй дифференциальные каскады, выполненные на транзисторах разного типа проводимости, с генераторами тока в обшкх эмиттерных цепях,. соответствуюшие входы дифференциальных каскадов попарно объединены и подключены к входам усилители, коллектор каждого из транзисторов подключен к шине питания через соответствуюший управляемый генератор тока (УГТ), при этом вход УГТ первого плеча каждого дифференциального каскада соединен с выходом УГТ второго плеча другого дифференциального каскада, а выходы

УГТ первых плеч дифференциальных каскадов объединены и подключены к выходу усилиНв чертеже изображена принципиальная электрическая схема дифференциального усилителя.

Изобретение относится к усилителям электрических колебаний и может использоваться в измерительной и вычислительной технике.

Известны дифференциальные усилители.

Один из известных дифференциальных усилителей содержит первый и второй транзисторы диф ференциального каскаде, причем коллектор одI (,ного транзистора дифференциального каскада подключен к входу управляемого генерато- 10 ра тока, выход которого соединен с коллектором другого транзистора дифференциального каскада, и генератор тока в обшей эмиттерной цепи транзисторов дифференциального каскада (1), }5

Наиболее близким техническим решением является дифференциальный усилитель, содержащий первый и второй дифференциальные каскады, выполненные на транзисторах 20 разного типа проводимости, с генераторами тока в обших эмиттерных цепях, в котором соответствую,чие входы дифференциальных каскадов попарно объединены и подключены к входам усилителя f 2), 25 (53) УДК.621.375.024 (088.8) 530425

Дифференциальный усилитель содержит

;первый и второй дифференциальные каскады, выполненные соответственно на транзисто.рах 1, 2 и 3, 4 разного типа проводимос-,ти, с генераторами тока 5 и 6 в общих емиттерных цепях, управляемые генерато.ры. тока (УГТ) первых плеч каждого,дифференциального каскада, выполненные соответственно на транзисторах 7, 8 и 9 10, УГТ втррых плеч каждого дифференциального каскада, выполненные соответственно на тр нзисторах 1 1, 1 2 и 1 3, 1 4, резисторы

15, 16 и сопротивление. нагрузки 17. Входы дифференциальных каскадов попарно объединены и подключены к входам усилителя, а коллектор каждого из транзисторов 1, 2, 3, 4 подключен к шине питания через со-,. ответствующий управляемый генератор тока, При этом вход УГТ первых плеч каждого дифференциального каскада соединен с выходом УГТ вторых плеч другого дифференциального каскада, а выходы УГТ первых плеч дифференциальных каскадов объединены и подключены к выходу усилителя.

Дифференциальный усилитель работает следующим образом.

В исходном состоянии ток, задаваемый

1 от источника напряжения + ь и — E I, через генераторы тока 6 и 5 соответственно рас- .

1 пределяются равномерно в коллекторные нагрузки дифференциальных каскадов, выпол-( пенных на транзисторах 1, 2 и 3, 4. На» грузкой,дифференциальных каскадов служат

УГЧ,образованные транзисторами.7, 11, 9, 13 в диодном включении и соответственно транзисторами 8, 12, 10, 14. Эти УГТ имеют малое входное сопротивление (десятки ом) при высоком выходном (сотни кило- . ом), широкий частотный диапазон при коэф- фициенте усиления го току, близком к единице.

Входной ток усилителя для общих входов дифференциальных каскадов равен разности входных токов транзисторов 1; 3 и

2, 4 разного типа проводимости. Если токи, покоя Э дифференциальных каскадов равны (наиболее распространенный режим) и коэффициенты усиления транзисторов 1 и 3 также равны, то происходит полная компенсацияи отсутствует входнойтоксмещения, вы-. зывающий ошибку на выходе дифференциального усилителя, даже при неравенстве входных сопротивлений источников сигнала. В коллекторных нагрузках дифференциальных каскадов протекают токи 3 и 3, нагруз-кой же являются, как уже указывалось, малые входные сопротивления УГТ, коэффицлсHT передачи llo току которых равен единице. Следовательно, каждый из УГТ

{транзисторы 7, 8 и 9, 10) выдает на общий выход токи, равные сумме токов на их: входе и противоположно направленные. На вход УГТ первого плеча дифференциальных каскадов (транзисторы 7, S) поступают ток .) с выхода усилителя и ток с выхода

УГТ на транзисторах 13, 14, равный .Э и совпадающий по направлению с 3 Таким ,образом, на выходе УГТ первого плеча име+

jQ .ется суммарный ток (3 «. 3 ) . Аналогично в силу симметрии дифференциального усилителя, на выходе УГТ второго плеча имеется суммарный ток (3 + 3 ) противоположного направления. Нетрудно видеть, 3Ь что суммарный ток в сопротивлении нагрузки 17 всегда равен нулю, так как любое приращение тока на выходе УГТ одного плеча, вызванное температурными изменениями или флуктуациями питающего напряжении, компенсируется равным приращением тока противоположного направления другого плеча.

Дифференциальный усилитель может работать как в режиме усилителя, так и в режиме переключателя тока.

Предлагае мый дифференциальный усилитель имеет высокую стабильность выходного уровня тока покоя, в нем отсутствует разбаланс, вызванный входными токами смеЗО щения транзисторов.

Формула изобретения

Дифференциальный усилитель, содержащий первый и второй дифференциальные каскады, выполненные на транзисторах разного типа проводимости, с генераторами тока в общих эмиттерных цепях, соответствующие входы дифференциальных каскадов попарно объединены и подключены к входам усилите-. ля, отличающийся тем,что,с целью уменьшения дрейфа нуля, коллектор каждого из транзисторов подключен к шине питания через соответствующий управляемый генератор тока (УГТ), при этом вход

УГТ первого плеча каждого дифференциального каскада соединен с выходом УГТ второго плеча другого дифференциального каскада, а выходы УГТ первых плеч дифференциальных каскадов объединены и подключены к выходу усилителя.

Источники информации, принятые во внимание при экспертизе:

1, Проектирование и применение операционных усилителей. Под ред, Дж. Грэма.

М., 1974, с. 60 {аналог).

2. Патент СШЛ Мю3530391, кл. 33023, 1970 (прототип).

530425

Составитель Г, Челей

Редактор О. Юркова Техред О. Луговая

Корректор Б. Югас

Филиал ППП Патент", г. Ужгород, ул. Проектная,4

Заказ 5240/646 Тираж 1029 Подписное

UHHHHH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035,Москва, Ж-35, Раушская наб., д. 4/5