Умножитель частоты

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11) 530462 (61) Дополнительное к:"- =- свнд-ву (22) Заявлено18.12.74, 21) 2086464/21 с присоединением заявки № (23) Приоритет (43) Опублнковано30.09.76.Бюллетень № 36 (51) M. Кл."Н 03 К 23/00

Государственный комитет

Совета Министров СССР по делам нзооретений и открытий (53) УДК 621.374..4 (088.8) (45) Дата опубликования описания 25.11.76 (72) Автор изобретени я

Ю. К. Майоров (71) Заявитель (54) УМНОЖИТЕЛЬ ЧАСТОТЬ|

Изобретение отйосится к измерительной технике, автоматике, в частности к системе регулирования авиационных двигателей.

Известен умножитель частоты, содержа;щий генератор импульсов, соединенный с фор- 5 .мирователем элементами И" и "ИЛИ", диодными ключами и накопительным конденсато:ром, а выход формирователя связан с входом .,генератора дополнительной цепью обратной связи, содержащей устройство пересчета (1 . lO

Однако для такого умножителя характерны .частотные ошибки в переходном режиме и фа:зовые ошибки в установившемся режиме работы.

Наиболее близким по технической сушнос-15 ти к предлагаемому умножителю является умножитель, содержащий последовательно соединенные первый счетчик и делитель частоты, входы которых объединены и через линию задержки подключены к входной шине и 2О к входу запоминающего устройства, входы которого соединены с выходами ячеек первого счетчика, и опорный генератор, выходы которого подключены к входам второго счетчика и делителя частоты (21.

Такой умножитель частоты имеет невысокуиз точность из-за появления неравномерности временных интервалов между выходными импульсами.

Иель изобретения — повышение точности умножения.

С этой целью в предлагаемый умножитель частоты, содержащий два счетчика, делитель частоты, запоминающее устройство, делитель частоты и линию задержки, введены элемент совпадения и дополнительная линия задержки, подключенная к выходу элемента совпадения и к второму входу второго счетчика, выходы ячеек которого соединены с входами элемента совпадения, а входы яче ек- с выходами запоминающего устройства.

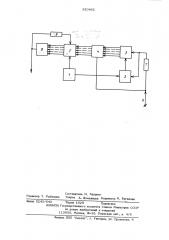

На чертеже представлена структурная электрическая схема умножителя частоты.

Умножитель частоты состоит из опорного генератора 1, соединенного с входом делителя частоты 2 с коэффициентом деления, р аным требуемому коэффициенту умножения, к выходу которого подключен вход первого ! счетчика 3. К выходам ячеек счетчика 3 подключено запоминающее устройство 4, к

530462 выходам ячеек которого подключен второй счетчик 5, выполненный вычитающим. Вход счетчика 5 соединен с опорным генератором 1. Входная шина 6 подключена к цепям считывания показаний счетчика 3 в запоминающее устройство 4 и к входу линии задержки 7, выход которой подключен к цепям сброса на нуль первого счетчика 3 и делителя частоты 2. Выход умножителяподключен к элементу совпадения 8, входы ко- ® торого подключены к выходам ячеек счетчика 5 и к входу дополнительной линии задержки 9, выход которой подключен к цепямсчитывания показаний устройства 4 во второй счетчик 5.

Умножитель работает следующим образом.

После прохождения через линию задержки 7 очередного импульса, поступившего на входную шину 5 умножителя частоты, происходит сброс на нуль счетчика 3 и делителя © частоты 2. Затем происходит накоплениесчетчиком 3 импульсов, поступающих с выхода делителя частоты 2. К моменту прихода на вход умножителя частоты следующего импульса в счетчик 3 записывается число 25 оп — Т

4 его в нулевое состояние. В момент попадания его в нулевое состояние с выхода элемента совпадения 8 поступает импульс на выход умножителя частоты. Этот же импульс поступает на вход дополнительной линии задержки 9, после прохождения импульса через которую происходит запись показания устройства 4 в счетчик 5. Следующий импульс на выходе умножителя частоты появляется через время

1= — -т т

К ъх 1„K

Таким образом, точность повышается за счет того, что второй счетчик не имеет связи с входом умножителя частоты.

Умножитель частоты, содержащий последовательно соединенные первый счетчик и делитель частоты, входы которых объединены и через линию задержки подключены к входной шине и к входу запоминаюшегоустройства, входы которого соединены с выходами ячеек первого счетчика, и опорный генератор, выходы которого подключены к входам второго счетчика и делителя частоты, о т л и ч а ю ш и и с я тем, что, с целью повышения точности умножения, в него введены элемент совпадения и дополнительная линия задержки, подключенная к выходуэлемента совпадения и к второму входу второго счетчика, выходы ячеек которого соединены с входами элемента совпадения, а входы ячеек — с выходами запоминающего устройства.

Источники информации, принятые во внимание при экспертизе изобретения:

1. A вт.св. СССР № 36 6 550, Н 03 К 1/16, 07.06.71.

2. Авт.св. СССР № 337947, Н 03 К 23/00, 28.12.70 (прототип). где т o — частота опорного генератора;

Т „, — период входной частоты; — коэффициент деления делителя частоты.

Входной импульс умножителя частоты поступает к цепям считывания показаний счетчика 3 в запоминающее устройство 4. Импульс с выхода линии задержки 7 сбрасыва- ет на нуль счетчик 3 и делитель частоты 2.

Таким образом, в устройстве 4 хранится все время число, соответствующее периоду входной частоты. Это число не стирается, атолько может изменяться в случае, если изменя-4g ется входная частота. Импульсы опорного генератора 1, поступая на вход вычитающего счетчика 5, в некоторый момент приводят

Формула изобретения

530462

Составитель М. Аудринг

Редактор Т. Рыбалова Техред д,. демьянова Корректор Н. Бугакова

Заказ 5243/643 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4