Фазовый различитель

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистимеских

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (11) 531096 (61) Дополнительное к авт. свид-ву— (22) Заявлено18.02,75 (21) 2106009/21 с присоединением заявки № (23) Приоритет (43) Опубликовано05.10,76.Бюллетень № 37 (45) Дата опубликования описания 15.02.77 (51) М. Кл."G 01 R 25/00

Государственный комитет

Совета Министров СССР оо делам изооретений и открытий (53) УДК 621.317,77 (088.8) (72) Авторы изобретения

В. В, Бессонов и А. Д. Ванейчик (71) Заявитель (54) ФАЗОВЫЙ РАЗЛИЧИТЕЛЬ

Изобретение относится к фазоизмерительной технике, может быть использовано при созданчи фазометров с расширенным угловым диапазоном.

Известны фазовые различители с расширенным диапазоном однозначности, например фазовый различитель по трехканальной схеме, содержащий общий для всех каналов генератор опорного напряжения, усилители, фазовращатели, фазовые детекторы в каждом из каналов, ограничители и сумматор

Этот фазовый различитель имеет недостаточно большой диапазон однозначного измерения разности фаз.

Наиболее близок к предлагаемому фазовый разпичитель, содержащий фазовый детектор и сумматор 121.

Однако диапазон однозначного измерения разности фаз у этого различителя не превышает +-" °

Бель изобретения — расширение диапазона однозначности амплитудно -фазовой характеристики устройства, 25

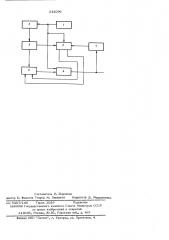

Поедлагаемь и фазовый различцтель отличается тем, что в него введе:-.ы и!оследовательно соединенные схема дифференцирования, логцческий элемент с ивBBpTDpoM и коммутатор, а также запоминающее устройство с умножителем на "два", первый вход которого одновременно подключен ко входам схем дифференцирования, сумматора и к выходу фазового детектора, второй вход подкл;очен к логическому элементу с пнвертором, а выход через второй вход коммутатора — ко входу сумматора, выход которого чсрез схему сравнения соединен с треть-. им входом запоминающего устройства с умножителем на "два", На чертеже представлена схема устройства, Фазовый различитель состоит из фазов<>го детектора l, схемы дифференцирования 2, запоминающего устройства с умножителем на "два" 3, сумматора 4, логического элемента с инвертором 5, ком татора 6 и схемы сравнения 7, Пусть при включении устройства раз531096 ность фаз положительна (О <9< T 7) и возрастает.

При положительном напряжении на выкать. де фазового детектора 1> когда разность фаз равна, например>, запоминающее

1Т устройство с умножителем на "два" 3 подключено непосредственно к выходу детектора. При 9 = 7 происходит скачок выходного сигнала фазового детектора в область отрицательных значений, на выходе схемы дифференцирования 2 появляется импульс отрицательной полярности. Этот импульс с помощью логического элемента с инвестором 5 подключает через коммутатор к сумматору 4 выход запоминающего устройства с умножителем на "два" 3 (удвоенное максимальное выходное напряжение фазового детектора 1); одновременно отключает запоминающее устройство 3 от фазового детектора и подключает к выходу схемы дифференцирования 2 инвертор, который находится в логическом элементе 5, подготавливая тем самым переключение полярности напряжения с выхода запоминающего устройства 3 на вход сумматора 4, Второй отрицательный импульс со схемы дифференцирования 2, который формируется при разности фаз 9 =3 У, переключает полярность напряжения с запоминающего устройства 3, которое подается на сумматор 4 через коммутатор. Третий отрицательный импульс со схемы дифференцирования 2 (при 9 =5 K ) с помощью логического элемента 5 отключает запоминающее устройство 3 от сумматора 4. Когда выходное напряжение сумматора будет равно заданному уровню вблизи нуля, схема сравнения 7 разряжает запоминающее устройство 3, Если напряжение на выходе сумматора4 превышает заданный уровень, схема сравнения 7 прекращает разряд запоминающего устройства 3 и подключает его к выходу фазового детектора 1, Если при включении устройства разность фаз отрицательна и возрастает по абсолютному значению, все процессы следуют в обратном порядке.

Использование схемы дифференцирования, логического элемента с инвертором, запс минающего устройства с удвоением напр жения и схемы сравнения позволяет расширить диапазон однозначного измерения разности фаз до + ЗТ, С помощью предложенного фазового различителя можно решить проблему регистрации медленно меняющихся разностей фаз в интервале, превышающем период. формулаизобретения

< азовый различитель, содержащий фазовый детектор и сумматор, о т л и ч а ю ш и и с я тем, что, с целью расширения диапазона однозначности его амплитуднофазовой характеристики при сохранении чувствительности, в него введены последовательно соединенные схема дифференцирования, логический элемент с инвертором и коммутатор, а также запоминаюшее устройство с умножителем на "два", первый вход которого одновременно подключен ко входам схемы дифференцирования, сумматора и к выходу фазового детектора, второй вход подключен к логическому элементу с инвертором, а выход через второй вход коммутатора подключен ко входу сумматора, выход которого через схему сравнения соединен с третьим входом запоминающего устройства с умножителем на "два".

Источники информации, принятые во внимание при экспертизе:

1, Авт,св. № 227407, кл. 2la, 42, 19,10.66.

2, Авт.св. № 391495, кл. G01 25/04, 27.09.7 1.

531096

Составитель И. Шаронова дектер Б. Федотов Техред M. Лееидкан Корректор ll. Меданичеико

<аз 5407/148 Тираж 1029 Подпионое

БНИИПИ Государственного комитета Совета Министров СССР ло делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 финиад ППП Патент", г. Ужгород, уа. Проектнаи, 4