Преобразователь сдвига фазы в код

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

Оп ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (11) 531181 (61) Дополнительное к авт. свид-ву— (22) Заявлено 26.12.74 (21) 2089467/24 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано 05.10.76. Бюллетень № 37 (45) Дата опубликования описаиия29.03.77 (51) M. Кл. G08C 9/00

G 01 R25/00

Государственный комитет

Совета Министров СССР па делам изобретений и открытий (53) УДК621.314.24(088.8) (72) Авторы изобретения

А. К. Смирнов, И. П. Глаголев и В. Д. Фатеев (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ СДВИГА ФАЗЫ В КОД

Изобретение относится к автоматическому управлению и вычислительной технике, в частности к преобразователям аналоговой величины в код.

Известны преобразователи сдвига фазы в код, в которых погрешность из — за нестабильности частоты входного сигнала компенсируется введением калибровочного отсчета. Код фазы в таких устройствах определяется в виде отношения точного и калибровочного отсчетов (1,2) .

Недостатком таких преобразователей является необходимость в вычислительном устройстве.

Наиболее близким техническим решением к предлагаемому преобразователю является преобразователь сдвига фазы в код, содержащий источник входных сигналов, соединенный с формирователями старт — и стоп — импульсов, генератор импульсов, выход которого через вентиль соединен с одним из входов делителя частоты, первую группу вентилей, подключенную через последовательно соединенные сумматор и преобразователь "код — напряжение" к входу генератора импульсов, триггер, элемент задержки и вторую группу вентилей (3). Для устранения погрешности из — за нестабильности частоты выходных сигналов в известный преобразователь введен генератор импульсов с регулируемой часто2 той. Известный преобразователь имеет сложную конструкцию и низкое быстродействие.

Цель изобретения — повышение быстродействия преобразователя и упрощение его конструкции.

Это достигается тем, что в предлагаемом преобразователе сдвига фазы в код формирователь старт-импульсов подключен к управляющим входам первой группы вентилей и через элемент задержки к нулевым входам делителя частоты и единичному входу

1р триггера, нулевой вход которого соединен с входной шиной, а нулевой выход подключен к нулевым входам делителя частоты и сумматора, единичные выходы разрядов делителя частоты через вторую группу вентилей подключены к выходным клем15 мам преобразователя сдвига фазы в код, а формирователь стоп-импульсов соединен с управляющими входами второй группы вентилей.

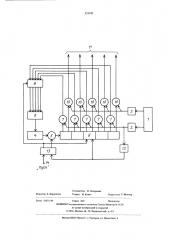

На чертеже представлена структурная схема предлагаемого преобразователя.

20 Преобразователь содержит источник входных сигналов 1, подключенный к формирователю 2 старт — импульсов и формирователю 3 стоп — импульсов, генератор импульсов 4, подключенный через вентиль 5 к делителю частоты 6. Нулевые выходы всех разрядов делителя частоты 6 через первую

531181 группу последовательно соединенных вентилей 7, сумматор 8, преобразователь " код-напряжение" 9 подключены к управляющему входу генератора 4.

Единичные выходы всех разрядов делителя частоты через вентили 10 подключены к выходу 11. преобразователя. Формирователь 2 подключен к управляющим входам первой группы вентилей 7 и через элемент задержки 12 к нулевым входам делителя частоты 6 и к единичному входу триггера 13, нулевои вход которого соединен с входной шиной 14 команды

"Пуск", единичный выход триггера 13 подключен к управляющему входу вентиля 5, а нулевой выход подключен к нулевым входам делителя частоты 6 и сумматора 8. Формирователь 3 подключен к входам второй группы вентилей 10.

Преобразователь работает следующим образом.

Импульсы генератора 4 с частотой где fax — частота сигналов источника 1, непрерывно поступают на вход и разрядного делителя 6. Сигналы источника 1, сдвинутые относительно друг друга по фазе, по25 ступают на вход формирователей 2 и 3, где формируются старт- и стоп-импульсы. По сигналу

"Пуск" происходит установка в начальное положение триггера 13, делителя 6 и сумматора 8.По первому старт-импульсу после сигнала "Пуск" изменяется состояние триггера 13, открывается вентиль S, и иьнульсы генератора 4 заполняют делитель

6. По каждому старт-импульсу обратный код делителя 6 складывается с содержимым сумматора 8 выходной код которого в преобразователе 9 преобразуется в напряжение и воздействует на генератор

4 регулируя частоту выходных импульсов генератора 4.

Кроме того, по ка кдому старт-импульсу производится установка в начальное положение делителя 6. По каждому стоп — импульсу прямой

40 код делителя 6 поступает на выходные клеммы 11 преобразователя.

Если частота импульсов генератора 4 и частота выходных сигналов источника 1 соответствунп

45 уравнению (1), то на вход сумматора 8 поступает нулевой код. При этом старт-иьшульс формируется в момент полного заполнения делителя 6 (все разряды находятся в состоянии "1"). При увеличении частоты выходных сигналов источника 1 на величину Д в,, входной код сумматора 8 увеличивается, что приводит к пропорциональному увеличению выходной частоты генератора 4 ь| =а дР (г) ги ах соотношение (1) снова выполняется, а старт — импульс формируется в момент полного за-полнения делителя 6. При уменьшении частоты выходных сигналов источника 1 обратный код делителя 6, поступающий на сумматор 8, скачком изменяется, переходя через максимальное значение.

Поскольку сложение обратного кода равносильно вычитанию прямого кода, то при уменьшении частоты выходных сигналов источника 1 содержимое сумматора 8 и частота выходных импульсов генератора 4 пропорционально уменьшается и соотношение (1) снова выполняется.

Формула изобретения

Преобразователь сдвига фазы в код, содержащий источник входных сигналов, соединенный с формирователями старт — и стоп — импульсов, генератор импульсов, выход которого через вентиль соединен с одним из входов делителя частоты, первую группу вентилей, подключенную через последовательно соединенные сумматор и преобразователь "код — напряжение" к входу генератора импульсов, триггер, элемент задержки и вторую группу вентилей, отличающий ся тем, что, с целью повышения быстродействия устройства и упрощения его конструкции, в нем формирователь старт-импульсов подключен к управляющим входам первой группы вентилей и через элемент задержки к нулевым входам делителя частоты и едц ичному входу триггера, нулевой вход которого соединен с входной шиной, а нулевой выход подключен к нулевым входам делителя частоты и сумматора, единичные выходы разрядов делителя частоты через вторую группу вентилей подключены к выходным клеммам преобразователя сдвига фазы в код, а формирователь стоп — импульсов соединен с управляющими входами второй группы вентилей.

Источники информации, принятые во внимание при экспертизе

1. Авт.св. СССР Р 283703, кл. G 08 С 9/00, 03.01.69.

2, Патент США N 3663956, кл. 324 — 83, 10.05.7 2.

3. Авт. св. СССР N 353207, кл. G 01R25/00, 02.04.71.

Составитель Н. Назаркина

Техред И. Ковач Корректор С Шекмар

Редактор Е. Караулова

Заказ 5367/140

Тираж 830 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4