Устройство для адресно-разрядной выборки системы 2,5 д

Иллюстрации

Показать всеРеферат

СОюз Сееетски) Социалистических

Республик

ОП ИКАНИЕ

ИЗОБРЕТЕН Ия

Х АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 16.10.73 (21) 1966460/21 с присоединением заявки №(23) Приоритет (»)531277 (51) М. Кл.

Н ОЗ К 17/00

G 11 С 11/02

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий (43) ОпублнкованоО5,10.76,Бюллетень № 37 (53) УДК 621.318 (088. 8 ) (45) Дата опубликования описания 23.12.76 (72) Авторы изобретения

Н. П. Епихин и H. Н. Сорокина (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АДРЕСНО-РАЗРЯДНОЙ ВЫБОРКИ

СИСТЕМЫ 2,5 Д

Изобретение относится к вычислительной технике и может быть использовано при разработке запоминающих устройств системы 2,5 Д.

Известно устройство для адресной выборки, содержащее формирователи (ключи) записывающих и считывающих токов, входы которых подключены к выходам управляющих ключей (каскадов возбуждения по эмитру) C1J. 1О

Однако известное устройство характеризуется нестабильностью временных параметров токов.

Известно также устройство для адресно-разрядной выборки системы 2,5 Д, со- 15 держащее в каждом разряде транзисторные ключи втекаюшего и вытекающего записывающего и считывающего токов, входы которых через согласующий блок подключены к дешифратору адреса, генераторы записывающего и считывающего токов, ключ, управляющий записывающим и считывающим токами, вход которого подключен к выходу регистра числа, диодный дешифратор адресных линий разряда и источник напряжения(2). 2>

Однако и это известное устройство также характеризуется нестабильностью временных параметров токов и имеет сложную констоукцию.

Целью изобретения является упрощение устройства и повышение стабильности временных параметров токов.

Для этого в каждый разряд дополнительно введены ключ, управляющий считывающим током и два последовательно согласно включенных диода, причем входы каждого транзисторного ключа втекаюшего и вытекающего записывающего и считывающего токов соединены через другой дополнительный диод и соответствующий ключ, управляющий записывающим током (считывающим) с шиной нулевого потенциала, которая через два дополнительных последовательно согласно включенных диода соединены с точкой соединения ключей втекаюшего считывающего тока; кроме того согласующий блок выполнен на транзисторах разного типа проводимости, .причем база каждого транзистора с проводимостью такой же, как и проводимость транзисторов ключей втекающих за3 531 писываюших токов (считывающих) подключе на к соответствуюшему выходу дешифратора адреса, эмиттер - к шине нулевого потенциала, коллектор — через резистор к базе транзистора обратной проводимости, которая через второй резистор соединена с положительным потенциалом источника напряжения, коллектор — через третий резистор подключен к шине нулевого потенциала, а также к входу транзисторного ключа втекаюшего (вытекающего ) записываюшег о тока (считываюшего) каждого разряда через резистор, эмиттеры транзисторов обратной проводимости вбьединены и через прямо включенный диод подключены к шине положительного потенциала источника напряжения.

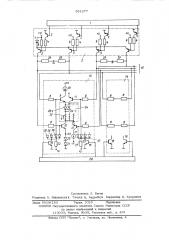

На чертеже приведена принципиальная электрическая схема устройства.

Устройство для адресно-разрядной выборки системы 2,5 Д содержит дешифратор адреса 1, выполненный, например, на логических интегральных узлах типа ТТЛ, выходы которого соединены с базами транзисторов 2 согласуюшего блока 3, коллектор каждого из которых через резистор 4 соединен с базой соответствующего транзистора 5 другого типа проводимости, база которого через резистор 6, а эмиттер— через диод 7 соединены с положительным потенциалом источника напряжения.

Эмиттеры транзисторов 5 обьединены, а коллекторы через резисторы 8 соединены с базами транзисторов ключей 9 — 12 вытекающего и втекаюшего считывающих токов и втекаюшего и вытекающего записываюших токов соответственно, которые образуют переключатель адресного тока одного разряда 13 и последующих подобных разрядов 14, 15 и т.д. запоминаюшего устройства структуры 2,5 Д.

Кроме того, переключатель адресного тока одного разряда содержит генераторы 16 и 17 считывающих и записывающих токов, ключи 18 и 19, управляюшие считывающими и записывающими токами соответственно, два последовательно соединенных диода 20 и 21, резисторы 22 и 23, диодный дешифратор 24 с выходом на нагруэку25 (адресные линии разряда).

Коллекторы ключей 18 и 19 через диоды 26 и 27 соединены с базами транзисторов ключей 9 и 10 и 11 и 12 соответственно, а базы - c выходами управляющего блока (регистра числа 28).

Коллектор каждого из транзисторов 5 через резистор 29 соединен с землей, а коллектор транзистора ключа 10 — с катодами диодов 24-1 дешифратора 24 адресных линий другого разряда, а эмиттер тран277 эисторов ключа 9 - с анодами других диодов 24-2 дешифратора 24.

В исходном состоянии транзисторы 2 за крыты сигналами с выхода дешифратора адреса 1 и закрыты транзисторы 5. Ключи 9 — 12 разомкнуты, а ключи 18 и 19замкнуты, при этом базы транзисторов ключей

9 — 12 через диоды 26 и 27 привязаны к потенциалу земли.

При обращении к запоминаюшему устрой ству, например по первому адресу с блока 28 запирается ключ 18, диоды 26 запираются положительным потенциалом череф резистор 22 и тем самым устраняется влИяние паразитных емкостей этих диодов на динамические процессы и базах транзисторов ключей 9 и 10. Последние удерживаются в закрытом состоянии нулевым потенциалом через резисторы 8 и 29.

26

При п оявлении с чит ываю ших импульс ов с выходов деыифратора адреса 1 соответствующие транзисторы 2 и 5 отпираются и на базы транзисторов ключей 9 и 10

М всех разрядов 13-15 подается отпирающий потенциал, Ключи 9 и 10 замыкаются, и через выбранную адресную линию протекаем считывающий ток генератора 16. Одновременно с окончанием считываюшего импульса кончается импульс с блока 28, ключ 18 замыкается ичереэ диоды 26 на базы транзисторов ключей 9 и 10 поступает нулевой потенциал.

Ключи 9 и 10 размыкаются и считываю35 ший ток в выбранной линии обрывается, не дождавшись запирания транзисторов 5.

При возбуждении записываюшего тока предварительно выключается ключ 19 данного разряда. С задержкой на время, не

49 меньшее времени выключения ключа 19, с выходов дешифратора адреса 1 появляются записывающие импульсы и соответствующие транзисторы 2 и 5 отпираются и ключи 11 и 12 данного разряда замыкаются, и через выбранную линию протекает записывающий ток генератора 17.

При записи 0", например, в разряде 14 ключ 19 этого разряда не размыкается и ключи 11 и 12 этого разряда остаются рад зомкнутыми, так как базы их транзисторов через диоды 27 и резистор 23 привязаны к нулевому потенциалу, а эмиттер транзистора ключа 11 смешен на два диодных перехода. у При записи 1" окончание записывающего тока происходит аналогично окончанию считывающего тока. Назначение ключей

9, 10, 18 может поменяться с назначением ключей 11,12,19 при изменении фазы то } ка.

531277

Формула изобретения

1. Устройство для адресно-разрядной выборки системы 2,5 3, содержащее в каждом разряде транзисторные ключи втекаюшего и вытекающего записывающего и считывающего токов, входы которых через согласующий блок подключены к дещифратору адреса, генераторы записывающего и считывающего токов, ключ, управляющий записывающим током, вход которого подключен к выходу регистра числа, диодный дешифратор адресных линий разряда и источник напряжения, о т л и ч а ю щ е е— с я тем, что, с целью упрощения устройства и повышения стабильности временных параметров токов, в каждый разряд дополнительно введены ключ, управляющий счи» тывающим током, и два последовательно согласно включенных диода, причем входы каждого транзисторного ключа втекающего и вытекающего записывающего и считывающего токов соединены через другой дополнительный диод и соответствующий ключ, управляющий записывающим током (считывающим) с шиной нулевого потенциала, которая через два дополнительных последоlO

Таким образом, в предложенном устройстве при относительной простоте его конструкции временные параметры записывающего и считывающего токов получаются

Ьысокостабильными.

d вательно согласно включенных диода соединены с точкой соединения ключей втекающего считывающего тока.

2. Устройство по и. 1, о т л и ч а ю— щ е е с я тем, что согласующий блок выполнен на транзисторах разного типа проводимости, причем база каждого транзистора с проводимостью такой же, как и проводимость транзисторов ключей втекающих записывающих токов (считывающих) подключена к соответствующему выходу дешифратора адреса, эмиттер — к шине нулевого потенциала, коллектоо — через резистор к базе транзистора обратной проводимости, которая через второй резистор соединена с положительным потенциалом источника напряжения, коллектор - через третий резистор подключен к шине нулевого потенциала. а также к входу транзисторного ключа втекающего (вытекающего) записывающего тока (считывающего) каждого разряда через резистор, эмиттеры транзисторов обратной проводимости обьединены и через прямо включенный диод подключены к шине положительного потенциала источника напряжения.

Источники информации, приняты во внимание при экспертизе.

1. Запоминающие устройства современных

ЭЦВМ, Сборник статей под ред. А, Крупского, М., 1968, с. 120.

2. JEEE Тга пьас1 o s om Ef ectvo c с,ornpu4er s,1966,чо1.EC-fs, М Ф, р 4.8

531277

Составитель Л. Багян

Редактор A. Зиньковский Техред Н. Андрейчук Корректор В. Куприянов

Заказ 5419/183 Тираж 1029 Подписное НИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4