Делитель частоты с целочисленным коэффициентом деления

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено03.02.75 (21) 210157O/21 с присоединением заявки №вЂ” (23) Приоритет (43) Опубликовано05.10.76.Бюллетень №37 (45) Дата опубликования описания 28.12.76

Союз Советских

Социалистических

Республик (11) 5З1285 (51) М. Кл.

Н 03 К 23/00

Государственный комитет

Соната Министров СССР по делам изобретений н открытий (53) УДК 681.374..44 (088.8) A.Н. Дебальчук, В.Н. Куликов, В.С. Семковский и Q.Н. Давиденко (72) Авторы изобретения (71) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ С ЦЕЛОЧИСЛЕННЫМ КОЭФФИЦИЕНТОМ

ДЕЛЕНИЯ

Изобретение относится к импульсной технике, может быть использовано в устройствах деления частоты на произвольное целое число.

Известны делители частоты с произволь ным целочисленным коэффициентом деления

f1, 2).

Первое из известных устройств содержит счетчик с дешифратором, выходной сигнал которого непосредственно или через допол- 0 нительный R5 -триггер устанавливает счетчик в исходное состояние.

Надежность этого устройства снижают сбои из-за одновременного воздействия сигналов запуска и установки счетчика в исход-15 ное состояние.

Второй делитель частоты, наиболее близкий к предлагаемому, содержит триггерный счетчик, выходы триггеров которого соединены со входами дешифратора, и два венти-. 20 ля, первые входы которых подключаются к клемме источника входного сигнала, выход первого вентиля соединен со входом счетчика, а выход второго — с шиной сброса счетчика. 25

Однако этот делитель частоты, кроме счетчика и дешифратора, содержит два вентиля, счетный триггер, инвертор и элемент

"ИЛИ". Это усложняет схему делителя и понижает его надежность, 11ель изобретения — повышение надежности схемы.

С этой целью в предлагаемый делитель частоты введены два дополнительных вентиля; выход первого вентиля подключен к первому управляющему входу второго и к первс му входу первого дополнительного вентиля, выход которого соединен с управляющим входом первого вентиля; выход второго дополнительного вентиля подключен ко второму входу первого дополнительного вентиля и ко второму управляющему входу второго вентиля, первый вход — к выходу второго вентиля, а второй вход — к выходу дешифратора

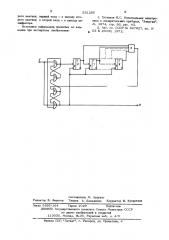

На чертеже представлена структурная схема делителя частоты с целочисленным коэффициентом деления.

Делитель частоты с любым целочисленным коэффициентом деления К (1 — К 6- 2") содержит четыре вентиля 1-4, попарно ох531285 ваченных обратными связями. Первые входы вентилей 1 и 2 соединены с клеммой исто*рника входного сигнала 5, выход вентиля 1 соединен с третьим входом вентиля 2 и со входом A -разрядного счетчика, состоящего из П последовательно соединенных триггеров 6-8, выходы которых через дешифратор

9 соединены со вторым входом вентиля 4 выход которого соединен со вторым входом вентиля 3. Выход вентиля 2 подключен к шине сброса триггеров и выходу (клемма

1 0) делителя.

Рассмотрим работу делителя для случая

К 15, П =4.

В исходном положении (момент Т ) триггеры n, — разрядного счетчика находятся в состоянии, соответствующем числу четырнадцать" (К-1). С дешифратора 9, настроенного на число К-1, на второй вход вентиля 4 поступает низкий потенциал, поэто му на его выходе оказывается потенциал.

Так как на первых входах вентилей 1 и 2, связанных с клеммой 5, действует низкий потенциал, на их выходах — высокие потенциалы, не влияющие на работу счетчика.

На обоих входах вентиля 3 действуют высокие потенциалы, поэтому с его выхода на управляющий вход вентиля 1 поступает низкий потенциал, запрещающий прохождение входных импульсов через этот вентиль.

На оба управляющих входа вентиля 2 с вентилей 1 и 4 поступают высокие потен— циалы, разрешающие прохождение входных импульсов через этот вентиль, Первый импульс, поступающий на клемму 5 (момент

), проходит на выход (клемма 10) и сбрасывает и -разрядный счетчик (обнуление) . При этом на выходе:дешифратора

9 (а следовательно и на входе вентиля 4) потенциал становится высоким, но потенциал на выходе вентиля 4 не изменяется и сохраняется высоким до окончания первого входного импульса (до момента 1 ), так как вентиль 4 блокирован по первому входу на время действия входного импульса потенциалом с вентиля 2. После окончания входного импульса (момент (- ) на вы5 ходе вентиля 2 устанавливается высокий потенциал, а на выходе вентиля 4 — низкий, так как на его обоих входах действуют высокие потенциалы. Этот низкий потенциал поступает на второй вход вентиля 3, на выхо де которого устанавливается высокий потенциал, поступающий на управляющий вход вентиля 1 и разрешающий прохождение входных импульсов через этот вентиль, На первый управляющий вход вентиля 2 с вентиля 4 поступает низкий потенциал, запрещающий прохождение входных импульсов через этот вентиль.

Следующие К-1 входных импульсов через вентиль 1 поступают на п -разрядный счетчик. С дешифратора 9 на второй вход вентиля 4 поступает все это время высокий потенциал.

После поступления К-го импульса (момент () все триггеры Г) -разрядного

l счетчика устанавливаются в состояние, при котором на выходе дешифратора 9 (а следовательно и на входе вентиля 4) снова появляется низкий потенциал.

На другом выходе вентиля 4 потенциал становится положительным. Этот потенциал поступает на первый управляющий вход вентиля 2, но прохождение К-го входного импульса через этот вентиль невозможно, так как он блокирован низким потенциалом по второму управляющему входу с вентиля 1 на время действия К-го входного импульса (до момента t ).

После окончания К-го входного импульса (момент t ) на выходах вентилей 1 и 2 устанавливаются высокие потенциалы.

HG обоих входах вентиля 3 снова действу— ют высокие потенциалы, поэтому с его выхода на управляющий вход вентиля 1 поступает низкий потенциал, запрещающий прохождение входных импульсов через этот вентиль. На обоих управляющих входах вентиля

2 действуют высокие потенциалы с вентилей 1 и 4, разрешающие прохождение входж х импульсов через этот вентиль.

К+1-вый входной импульс проходит (момент 1 ) через вентиль 2 на выход делителя и сбрасывает h - разрядный счетчик.

После окончания импульса (момент 1 ) разрешается прохождение входных импульсов через вентиль 1 и запрещается прохождение их через вентиль 2.

Далее цикл работы повторяется.

Фо,.мула изобретения

Делитель частоты с целочисленным коэффициентом деления, содержащий триггерный счетчик, выходы триггеров которого соединены со входами дешифратора, и два вентиля, первые входы которых подключаются к клемме источника входного сигнала, выход первого вентиля соединен со входом счетчика, а выход второго — с шиной сброса счетчика, отличающийся тем, что, с целью повышения его надежности, в него введены два дополнительных вентиля, при этом выход первого вентиля подключен к первому управляющему входу второго и к первому входу первого дополнительного вентиля, выход которого соединен с управляющим входом первого вентиля, выход вто рого дополнительного вентиля подключен ко второму входу первого дополнительного вентиля и ко второму управляющему входу вта531285

Составитель М. Аудринг

Редактор Б. Федотов Техред А. Демьянова Корректор В. Куприянов

Заказ 5395/164 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 рого вентиля, первый вход — к выходу второго вентиля, а второй вход — к выходу дешифратора.

Источники информации, принятые во внимание при экспертизе изобретения:

1. Гутников В.С. Интегральная электроника в измерительных приборах, Энергия;

Л., 1974, стр. 86, рис. 43.

2. Авт. св. СССР ¹ 347927, кл. Н

03 К 23/00, 1972.