Устройство контроля интегральных схем

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К атОРСКОМ СаИДИТИЛЬСТВ

Союз Советских

Социалистических

Республик (») 532830 (61) Дополнительное к авт. свид-ву (22) Заявлено 11,07.75 (21) 2155913/21 с присоединением заявки № (23) Приоритет (51) М. Кл е

601 R 31/28

Гасударственный комитет

Совета Министров СССР по делам ивооретений и открытий (43) Опубликовано 25.10.76.Бюллетень ¹ 3 ! (45) Дата опубликования описания 16.02.77 (53) VQK 621.317.799 (088. 8) Д.И. Ажоткин и С.А, Гаврилов (7 2) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО КОНТРОЛЯ ИНТЕГРАЛЬНЫХ

СХЕМ

Изобретение относится к области вычислительной техники и может быть использовано в автоматизированных системах контроля интегральных схем (ИС) с динамической логикой.

Известны устройства контроля логических ИС, содержащие генератор импульсов, счетчик дишифратор, блок элементов совпадения fl). Однако такие устройства не обеспечивают контроля ИС с "совмещенными" 1О выводами в динамическом режиме, которые в один из тактов питания являются входами, а в другой такт - выходами.

Известна также система автоматического,5 контроля больших интегральных схем, которая содержит блок управления, блок памяти, амплитудный дискриминатор, ссединенный с элементом ИЛИ (21.

Однако известные устройства контроля 20 интегральных схем не обеспечивают быстрой перекоммутации "совмещенных" выводов

ИС с низкоомных выходов блока памяти на высокоомные входы амплитудных диск и4ми наторов и не позволяют производить конт- 25 роль таких ИС с частотой, превышающей частоту обращения к блоку памяти, 11ель изобретения - расширить функциональные возможности устройства.

Это достигается тем, что в устройство контроля интегральных схелл, содержащее блок управления, блок памяти и амплитудный дискриминатор, соединенный с элементом ИЛИ, введены две пары ключей входных цепей и ожидаемых выходных тестов, которые информационными входами подключены к выходам блока памяти, а управляющими входами - к выходам блока управления, причем выходы ключей входных цепей подключены к зажимам объекта контроля (ИС) и информационным входам амплитудного дискриминатора, вход сравнения которого подщпочен к выходам ключей ожидаемых выходных тестов, а разрешающий вход амплитудного дискриминатора соединен с входом блока управления.

Такое устройство обеспечивает возможность контроля интегральных схем с совмещенными" выходами с частотой, превышающей частоту обращения к блоку памяти

532830 в результате быстрой перекоммутации выводов объекта с низкоомных выходов блока памяти на высокоомные входы амплитудных дискриминаторов.

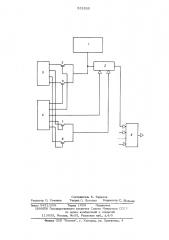

На чертеже представлена структурная 5 электрическая схема устройства контроля

ИС для одного вывода объекта контроля.

Зажимы объекта контроля 1 подключены к высокоомному входу амплитудного дискриминатора 2 и через транзисторные ключи 3 и 4 входных цепей - к выходам разных разрядов блока памяти 5 хранения тестовых комбинаций. Управляющие входы транзисторных ключей 3 и 4 подключены к соответствующим выходам блока управления 6, 15 соответствующие выходы которого подключены к управляющим входам транзисторных ключей 7 и 8 ожидаемых выходных тестов и к разрешающему входу амплитудного диск20 риминатора 2. Ключи 7 и 8 включены между соответствующими выходами блока памяти и входом сравнения амплитудного дискриминатора. Выход амплитудного дискриминатора 2 соединен с входом элемента ИЛИ. 9.

Входные воздействия, выделяемые блоком памяти 5, поступают на клеммы объекта контроля 1 только в моменты времени, определяемые импульсами, поступающими на управляющие входы транзисторных ключей 3 и 4 с выхода блока управления 6, вырабатывающего стробируюшиэ импульсы.

Причем частота смены входной информации, поступающей на соответствующую клемму объекта контроля, может превышать максимальную частоту выдачи информации блоком памяти 5.

За один цикл выдачи информации блоком памяти 5 на клемме объекта контроля происходит двойная смена входной информации.

Входная информация, поступающая на клемму объекта контроля 1, одновременно поступает и на вход амплитудного дискриминатора 2. Однако срабатывания амплитудного дискриминатора не происходит,так как 45 блок управления 6 при этом не выдает на амплитудный дискриминатор 2 разрешающего импульса (стробирование по выходу).

Стробируюший импульс на амплитудный дискриминатор 2 подается в такт, при кото- 5О ром на клемме объекта контроля 1 появляется выходной сигнал. Транзисторные ключи 3 и 4 при этом закрыты, и выходной сигнал не шунтируется низкоомными выходами блока памяти 5.

Выходной сигнал с клеммы объекта контроля 1 поступает на вход дискриминатора

2 одновременно с разрешающим импульсом блока управления 6, подающего импульс на амплитудный дискриминатор 2. В тот же момент времени блок управления 6 открывает один из транзисторных ключей

7, 8 ожидаемых выходных тестов, разрешающих прохождение информации с выхода блока памяти, которая должна соответствовать выходным сигналам объекта конт» роля в данный момент времени при правильно работающем объекте контроля 1 (ожидаемые тестовые комбинации). Амплитудный дискриминатор 2 фиксирует амплитуду выходного сигнала объекта контроля„ сравнивает ее с ожидаемой информацией, выдаваемой блоком памяти 5 через ключи

7, 8, и при несовпадении сигналов выдает сигнал ошибки на вход элемента ИЛИ, на выходе которого при этом появляется сигнал о наличии брака, Формула изобретения

Устройство контроля интегральных схем, содержащее блок управления, блок памяти и амплитудный дискриминатор, соединенный с элементом ИЛИ, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены две пары ключей входных цепей и ожидаемых выходных гестов. которые информационными входами подключены к выходам блока памяти, а управляющими входами — к выходам блока управления, причем выходы ключей входных цепей подключены к зажимам объекта контроля и информационным входам амплитудного дискриминатора, вход сравнения которого подключен к выходам ключей ожидаемых выходных тестов, а разрешающий вход амплитудного дискриминатора соединен с выходом блока управления, 532830

Составитель Е. Березов

Редактор О, Стенина Техред О. Луговая Корректор С. Щекмар

Заказ 545 1 I2 0 8 Тираж 1 02 9 Подписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Млиал ППП "Патент", г. Ужгород, ул. Проектная, 4