Устройство управления

Иллюстрации

Показать всеРеферат

(1!! 533927

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Х АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Со@о CG88TQKIIx

Социалистических

Респ}, блик (б1) Дополнительное к авт. свид-ву 213421 (22) Заявлено 03.01.74 (21) 1985408/24 с присоединением заявки № (23) Приоритет

Опубликовано 30.10.76. Бюллетень № 40

Дата опубликования описания 18.10.76 (51) М, Кл. G 06F 9/00 (осударстзеииьо! комитет

Совета Мииистрое СССР оо лелем изооретеиий и откре1тий (53) УДК 681.326(088,8) (72) Лвторы изобретения

A. И. Фельдман, С. Н. Фокин и В. С. Голоборщенко (71) Заявитель (54) УСТРОЙСТВ

Изобретение относится к области вычислительной техн.!ки и может быть использовано в устройствах управления специализированных цифровых вычислительных машин.

По основному авт. св. № 213421 известно устройство управления, содержащее коорди-! атные регистры, сьязанные с диодной матрицсй, выходнь!е шины которой прошивают сердечники долговременного запоминающего блока, дополнительные сердечники, число которых равно числу координатных шин диодной матрицы, а выходные шины этих сердечников соединены с координатными регистрами по

: райней мсрс цо одной из координат через

;.о D!) òàòîð со входом условного перехода. г1c. 10c Га Гном те1коГО у стройства явл5!ется отсутс Гвис контрог1я кода на выходных шинах долговрсмснпог0:запоминающего блока, что

", о!рсдсле;-1пых у.словиях приводит к несанкционированному выполнению программы вы !ислитсльной машины, а это, в свою очередь, влечет за собой резкое нарушение режима порсблсния электроэнергии, связанный с этим

«ыход из строя полупроводниковых приборов в блоках !III!ания и других узлах вычислительной машины. что существенно снижает на.!ст Ä;Iость работы устройства.

i1оис!: а! ого TIIII3 неисправности очень за трудпсц, за!! мает много времени и требует высокой квалификации обслуживающего персонала.

Целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что B устройство дополнительно введены сдвигающий регистр, два триггера, три элемента И и узел индикации, причем вход сдвигающего регистра соединен с первым входом устройства и с первыми входами первого и второго элементов И, первый и второй выходы сдвигающего регистра соединены соответственно с единичным входом первого триггера и с первым входом третьего элемента И, второй вход

15 и выход которого соединены соответственно с единичньгм .выходом второго триггера и с нулевым входом пер!вого триггера, нулевой выход которого соединен через первый элемент И с управляющими входами координат20 ных регистров и коммутатора, единичный выход первого триггера через второй элемент И соединен с нулевым входом второго триггера, нулевой выход и единичный вход которого соединены соответственно со входом узла инди25 кации и со вторым входом устройства.

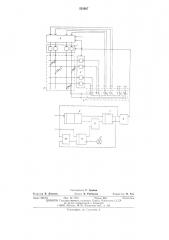

Блок-схема устройства приведена на чертеже.

Устройство содержит координатные регистры 1, 2, диодную матрицу 3, долговременный

З0 запоминающий блок 4, коммутатор 5, сдвига

533927

3 ющий регистр б, триггеры 7, 8, элементы И

9 — 11, узел индикации 12.

Устройство работает следующим образом.

В начальный момент сдвигающий регистр б находится в нулевом состоянии, первый триггеу 7 — в нулевом состоянии, второй триггер 8 — в единичном состоянии.

Сигнал вызова очередной команды вырабатывается, например, узлом микрокоманд в последнем такте каждой команды.

Поступающий сигнал записывает «1» в первый разряд сдвигающего регистра 6 и через первый элемент И 9 опрашивает координатные регистры 1, 2 и коммутатор 5, вызывая очередную команду с временем выполнения, например, IV такта. Продвижение «1» в сдвигающем регистре б осуществляется тактовыми им пульсами. Сигнал с перьвого выхода сдвигающего регистра 6 устанавливает в «1» первый триггер 7 и на входе первого элемента И

9 устанавливается сигнал, запрещающий прохождение сигнала вызова очередной команды на координатные регистры 1, 2 и коммутатор 5. Запрет снимается сигналом со второго выхода сдвигающего регистра 6, который через третий элемент И 11 устанавливает первый триггер 7 в «О».

Затем поступает сигнал вызо|ва очередной команды.

Предположим, что произошел одновременный запуск двух команд с временем выполнения V u VI тактов. По окончании первой команды ароизойдет вызов очередной команды, после окончания второй команды сигнал вызова очередной команды не поступает на координатные регистры 1, 2 и коммутатор 5, так как отсутствует разрешение на входе первого элемента И 9. Сигнал через второй элемент И 10 устанавливает второй триггер 8 в «О», что приводит к снятию разрешения с входа третьего элемента И 11 с одновременной индикацией характера неисправности.

Отсутствие разрешения на входе третьего элемента И 11 не позволяет сигналу со второго выхода сдвигающего .регистра 6 установить в «0» первый триггер 7 и сигнал вызова

4 очередной команды не поступает на координатные регистры 1, 2 и коммутатор 5. Таким образом прекращается несанкционированное выполнение программы.

Для того, чтобы разрешить поступление сигнала вызова очередной команды на координатные регистры 1, 2 и коммутатор 5, HcoGxoдим сигнал запуска извне.

Таким образом, изобретение, основанное на анализе временного распределения сигналов в устройстве управления, позволяет осуществить контроль при незначительных затратах оборудования (7 — 8 ячеек при реализации на феррит — транзисторной системе элементов, или 5 — 6 корпусов серии 155 системы элементов ИМС), предотвратить нежелательные последствия несанкционированного выполнения программы, сократить время поиска неисправности, что в конечном итоге, приводит к существенному повышению надежности работы устройства.

Формула изобретения

Устройство управления по авт. св.

М 213421, отличающееся тем, что, с цслью повышения надежности его работы, оно содержит сдвигающий регистр, два триггера, три элемента И и узел индикации, причем

30 вход сдвигающего регистра соединен с первым входом устройства и с первыми входами первого и второго элементов И, первый и второй выходы сдвигающего регистра соединены соответственно с единичным входом первого

35 триггера и с первым входом третьего элемента И, второй вход и выход которого соединены соответственно с единичным выходом второго триггера и с нулевым входом первого триггера, нулевой выход которого соединен че40 рез первый элемент И с управляющими входами координатных регистров и коммутатора, единичный выход первого триггера через второй элемент И соединен с нулевым входом второго триггера, нулевой выход и единичный

43 вход которого соединены соответственно со входом узла индикации и со вторым входом устройства.

533927

Составитель P. Арешев

Текрсд В. Рыбакова корректор Н. Аук

Редактор В. Левятов

Типография, пр. Сапунова, 2

Заказ 2312/1 Изд. М 17!б Тира>к 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений п открытий

113035, Москва, Ж-35, Раугиская наб., д. 4/5