Фазовый дискриминатор

Иллюстрации

Показать всеРеферат

=нт - о"

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (,, 53403I

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 02.06.75 (21) 2139657/21 с присоединением заявки № (23) Приоритет

Опубликовано 30.10.76. Бюллетень № 40

Дата опубликования описания 10.11.76 (51) М. Кл."- Н 03К 9/Оа

Государственный комитет

Совета Министров СССР (53) УДК 621.374(088.8) по делам изобретений и открытий (72) Авторы изобретения

В. Н. Семенычев и В. В. Смирнов (71) Заявитель (54) ФАЗОВЫЙ ДИСКРИМИНАТОР

Изобретение относится к измерительной технике и может быть использовано для измерения фазовых сдвигов импульсных сигналов, в системах автоподстройки частоты автогенераторов.

Известен фазовый дискриминатор электрических сигналов, содержащий формирователи прямоугольных импульсов, соединенные с разделительными каскадами, логические элементы И, ИЛИ вЂ” НЕ и цепь временной селекции, подключенную к триггерному блоку (1).

Однако такой дискриминатор не определяет опережение (или отставание) одного сигнала относительно другого, кроме того, надежность его низкая.

Известен также фазовый дискриминатор, содержащий соответственно соединенные логические элементы (2).

Надежность этого дискриминатора также низкая вследствие того, что он содержит значительное количество многовходовых логических элементов.

Наиболее близким техническим решением к предлагаемому изобретению является фазовый дискриминатор, содержащий входные и выходные зажимы, потенциальный статический триггер с раздельными входами и два логических элемента НЕ, причем для потенциального статического триггера и логических элементов HE соединены с соответствующими входными зажимами, два двухвходовых логических элемента И и два двухвходовых логических элемента ИЛИ, выходы каждого плеча триггера через элементы И соединены с разными входами соответствующих элементов ИЛИ, а выходы элементов ИЛИ являются выходами фазового дискриминатора (3.)

Недостатки такого фазового дискриминатора — низкая надежность и сложность схемы.

Цель изобретения — повышение надежности при сохранении удвоенной частоты пульсации.

Это достигается тем, что в предлагаемый фазовый дискриминатор введены дополнительный потенциальный статический триггер и два двухвходовых логических элемента

И вЂ” НЕ, причем входы дополнительного потенциального статического триггера соединены с выходами логических элементов НЕ, а его

20 выходы соединены с первыми входами дополнительных двухвходовых элементов И вЂ” НЕ, вторые входы которых соединены с соответствующими выходами потенциального статического триггера, а их выходы — с выходными

Б зажимами.

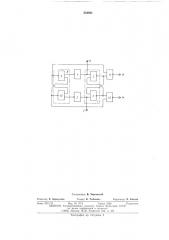

На чертеже представлена электрическая схема предлагаемого фазового дискриминатора.

Фазовый дискриминатор содержит потенЗо циальный статический триггер 1 с раздельны534031

35

М 1328031, 3 ми входами, выполненный на двух двухвходовых логических элементах И вЂ” НЕ 2, 3, перекрестно соединенных между собой, и логические элементы НЕ 4, 5. Входы логических элементов 2 — 5 соединены с соответствующими входными зажимами 6, 7. Выходы логических элементов 4, 5 соединены с соответствующими входами дополнительного потенциального статического триггера 8, выполненного на двух двухвходовых логических элементах И вЂ” НЕ 9, 10, перекрестно соединенных между собой. Выходы логических элементов

9, 10 соединены с первыми входами двухвходовых логических элементов И вЂ” HE 11, 12, вторые входы которых соединены .с выходами соответствующих логических элементов

И вЂ” НЕ 2, 3. Выходы логических элементов

И вЂ” HE 11, 12 являются выходными зажимами 13 и 14 фазового дискриминатора.

Фазовый дискриминатор работает следующим образом.

Импульсы положительной полярности со скважностью, равной двум, сформированные из опорного синусоидального напряжения, подаются на зажим 6, а импульсы, сформированные из рабочего синусоидального напряжения, подаются на зажим 7.

Если сигнал на зажиме 6 опережает сигнал на входном зажиме 7, то в этом случае на выходе логического элемента И вЂ” НЕ 2 формируется инвертированный опорный импульсный сигнал, на выходе логического элемента

И вЂ” НЕ 3 формируются импульсы низкого уровня, длительность которых пропорциональна отклонению фазы от 0 .

Инвертированные входные сигналы с выходов логических элементов НЕ 4 и 5 поступают на входы триггера, выполненного на логических элементах И вЂ” НЕ 9 и 10, при этом на выходе логического элемента И вЂ” HE 9 формируется прямой опорный импульсный сигнал, а на выходе логического элемента И вЂ” НЕ 10 формируются импульсы низкого уровня, длительность которых пропорциональна отклонению фазы от 0, кроме того, эти импульсы сдвинуты во времени на полпериода опорной частоты относительно импульсов с выхода логического элемента 8.

Сигналы с выходов логических элементов 2 и 9 поступают на логический элемент 11. Поскольку .поступаемые сигналы являются прямыми и инвертированными опорными сигналами, то на выходе логического элемента 11 импульсы отсутствуют, при этом на его выходе поддерживается положительный потенциал.

Сигналы с выходов логических элементов 3 и 10 поступают на логический элемент 12, в результате чего поочередно через каждые полпериода опорной частоты на выходе логического элемента 12 формируются положительные импульсы, длительность которых пропорциональна отклонению фазы от 0 .

Таким образом, при изменении фазового сдвига между входными сигналами в преде4 лах от 0 до 180 на выходе логического элемента 11 поддерживается положительный потенциал, а на выходе логического элемента 12 формируются положительные импульсы, частота повторения которых равна удвоенной опорной частоте, а длительность импульсов пропорциональна отклонению фазы от 0 .

Если сигнал на зажиме 7 опережает сигнал на зажиме 6, то выходной импульсный сигнал формируется на выходе логического элемента 11, а на выходе логического элемента 12 поддерживается положительный потенциал. Длительность положительных импульсов на выходе логического элемента 11 при изменении фазового сдвига в пределах от

180 до 360 тем меньше, чем больше отклонение фазы от 180 .

При фазовом сдвиге, равном 180, ни в одном из логических элементов 11 и 12 совпадения положительных импульсов не происходит, и, следовательно, на выходах дискриминатора поддерживается положительный потенциал; при фазовом сдвиге, не равном 180, фазовый дискриминатор имеет удвоенную частоту пульсаций по сравнению с частотой опорного сигнала и позволяет получать как непрерывную информацию о фазовом сдвиге между входными сигналами, так и информацию о взаимном опережении (или отставании) сигналов.

Кроме того, уменьшение числа используемых логических элементов позволяет повысить надежность дискриминатора, уменьшить его габариты и стоимость.

Формула изобретения

Фазовый дискриминатор, содержащий входные и выходные зажимы, потенциальный статический триггер с раздельными входами и два логических элемента НЕ, причем входы потенциального статического триггера и логических элементов НЕ соединены с соответствующими входными зажимами, о т л и ч а юшийся тем, что, с целью повышения надежности при сохранении удвоенной частоты пульсации, в него введены дополнительный потенциальный статический триггер и два двухвходовых логических элемента И вЂ” НЕ, причем входы дополнительного потенциального статического триггера соединены с выходами логических элементов НЕ, а его выходы соединены с первыми входами дополнительных двухвходовых элементов И вЂ” НЕ, вторые входы которых соединены с соответствующими выходами потенциального статического триггера, а их выходы — с выходными зажимами.

Источники информации, принятые во внимание при экспертизе:

1. Патент США ЛЪ 3469196, кл. 328 — 133, 04. 10. 69.

Патент Великобритании кл. НЗА, 03.06.71.

3. Авт. св. СССР Ко 413614, кл. Н 03к 9/04, 04.01.72, 534031

Составитель В. Чернявский

Редактор Е. Караулова Техред В. Рыбакова Корректор Л. Котова

Заказ 2311/12 Изд. ¹ 1713 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открыт й

1!3035, Москва, Я-35, Раушская паб., д. 4/5

Типография, пр. Сапунова, 2