Декодирующее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (i i) 534039

Совэ Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 30.07.73 (21) 1955096/24 с присоединением заявки № (5I) М. Кл.2 Н 04Ь 1/00

Совета Министров СССР по лелам изобретений ОпУбликовано 30.10.76. Бюллетень № 40 (53) УДК 621.391.28:

: 691.391.254 (088.8) и открытий

Дата опубликования описания 18.11.76 (72) Авторы изобретения

Ю. Ф. Коробов и Ю. Д. Иванов

Одесский электротехнический институт связи им. А. С. Попова (71) Заявитель

ГосУларственный комитет (23) 1-триоритет

Изобретение относится к области вычислительной техники и может быть использовано в системах передачи дискретной информации с решающей обратной связью (POC).

Известны устройства (1) и (2), предназначенные для декодирования корректирующих кодов. Недостатком известных устройств является то, что информация, получаемая при проверках принимаемого корректирующего кода, не используется.

Известно также устройство (3), предназначенное для мажоритарного декодирования циклического кода с разделенными проверками, которое является ближайщим аналогом изобретения. Зто устройство содержит переключатель, выход которого соединен со входом буферного регистра, выходы которого соединены со входами соответствующих сумматоров по модулю «два» и мажоритарный блок, выход которого соединен со вторым входом переключателя, первый вход которого соединен со входом устройства.

Недостатком известного декодирующего устройства (3) являются ограниченные функциональные возможности, в частности то, что в нем отсутствует сигнализация об обнаруженных ошибках, а это не позволяет использовать известное устройство в системах передачи дискретной информации с РОС.

Целью изобретения является повьппение помехоустойчивости приема сигналов в системе с РОС за счет расширения функциональных возможностей декодирующего устройства.

Указанная цель достигается тем, что в декодирующее устройство введены выходной регистр, блок формирования сигнала обратной связи, счетчик сигналов о недостоверных проверках, блок формирования сигналов отключения и блок обнаружения недостоверных

1о символов, вход которого соединен с первым входом переключателя, а выход — с нулевым входом блока формирования сигналов отключения и входом счетчика сигналов о недостоверных проверках, один из входов блока фор15 мирования сигналов отключения соединен с нулевым выходом буферного регистра, другие входы блока формирования сигналов отключения соединены с выходами сумматоров по модулю «два», а выходы — с соответствую20 щими входами мажоритарного блока, выход которого соединен с первым входом выходного регистра, второй вход которого соединен со вторым выходом блока формирования сигнала обратной связи, вход которого соединен с

25 выходом счетчика сигналов о недостоверных проверках.

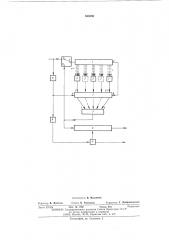

На чертеже представлена блок-схема описываемого декодирующего устройства.

Устройство содержит буферный регистр 1, 30 сумматоры по модулю «два» 2, мажоритарный

534039

1О

15 блок 3, выходной регистр 4, переключатель 5, блок обнаружения недостоверных символов 6, блок формирования сигналов отключения 7, счетчик сигналов о недостоверных проверках

8 и блок формирования сигнала обратной связи 9.

Вход буферного регистра 1 соединен с выходом переключателя 5, а 1..., п — 1-ый выходы соединены со входами соответствующих сумматоров по модулю «два», выходы которых соединены с 1,..., б — 1-ым входами блока формирования сигналов отключения 7, 6 вход которого соединен с 0 выходом буферного регистра 1, а выходы соединены с 1,..., б входами мажоритарного блока 3, выход которого соединен со вторым входом переключателя 5 и первым входом выходного регистра

4, второй вход которого соединен со вторым выходом блока формирования сигнала обратной связи 9, вход которого соединен с выходом счетчика сигналов о недостоверных проверках 8, вход которого соединен с нулевым входом блока формирования сигналов отключения 7 и выходом блока обнаружения недостоверных символов 6, вход которого соединен с первым входом переключателя 5.

Устройство работает следующим образом.

Принятая кодовая комбинация длины п поступает одновременно на вход блока обнаружения недостоверных символов 6 и через первый вход переключателя 5, находящегося в положении а (режим приема), на вход регистра 1. После того, как вся кодовая комбинация окажется записанной в регистре 1 переключатель 5 переводится в положение в (режим декодирования). С п выходов регистра 1 согласно алгоритму, определяемому корректирующим кодом, кодовые символы поступают на соответствующие входы сумматоров 2.

Операции суммирования кодовых символов по модулю «два», производимые в сумматорах 2, являются проверками данного циклического кода, количество которых равно 6. Результаты проверок через блок формирования сигналов отключения 7 поступает на вход мажоритарного блока 3. Блок 7 согласно сигналам, поступающим из блока обнаружения недостоверных символов 6 на его нулевой вход, производит формирование сигналов отключения проверок, в состав которых входят недостоверные символы, определяемые блоком 6. Поэтому на вход мажоритарного блока 3 поступают проверки, которые не содержат недостоверных символов. Декодированная кодовая комбинация, содержащая К информационных символов, поступает в выходной регистр 4, выход которого является выходом декодирующего устройства. Если число проверок, опре20

3О

35 ао

55 деляемых счетчиком сигналов о недостоверных проверках 8, равно или превышает количество проверок 6, то блок формирования сигнала обратной связи 9 вырабагывает сигнал, поступающий по каналу обратной связи на передатчик и производит стирание декодированных символов, находящихся в выходном регистре 4.

Таким образом, отключение проверок, в которых обнаружены недостоверные символы и одновременно использование сигналов отключения для запроса искаженных кодовых комбинаций, позволяет в описанном устройстве повысить помехоустойчивость приема сигналов.

Формула изобретения

Декодирующее устройство, содержащее переключатель, выход которого соединен со входом буферного регистра, выходы которого соединены со входами соответствующих сумматоров по модулю «два», и мажоритарный блок, выход которого соединен со вторым входом переключателя, первый вход которого соединен со входом устройства, о тл и ч а ющ е е с я тем, что, с целью повышения помехоустойчивости приема сигналов, в него введены выходной регистр, блок формирования сигнала обратной связи, счетчик сигналов о недостоверных проверках, блок формирования сигналов отключения и блок обнаружения недостоверных символов, вход которого соединен с первым входом переключателя, а выход — с нулевым входом блока формирования сигналов отключения и входом счетчика сигналов о недостоверных проверках, один из входов блока формирования сигналов отключения соединен с нулевым выходом буферного регистра, другие входы блока формирования сигналов отключения соединены с выходами сумматоров по модулю «два», а выходы — с соответствующими входами мажоритарного блока, выход которого соединен с первым входом выходного регистра, второй вход которого соединен со вторым выходом блока формирования сигнала обратной связи, вход которого соединен с выходом счетчика сигналов о недостоверных проверках.

Источники информации, принятые во внимание при экспертизе:

1. Патент США Кю 3718905, кл. G 06F 11/12, 1973.

2. Патент ФРГ K 1210908, кл. 21 а 17/06, 1966.

3. Мирончиков Е. Т, и др. Декодирование циклических кодов. М., «Связь», 1968., стр. 113.

534039

Составитель В. Максимов

Техрсд В. Рыбакова

Редактор В. Левятов

Корректор T. Добровольская

Заказ 2373(8 Изд. № 1766 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2