Матричный коммутатор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

И ЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 18.08.75 (21) 2 165381/2 1

Союз Советских

Социалистических

Республик () )) 53 487 1 (51) М, Кл.т

Н 03 К 17/60 с присоединением заявки №

Государственный комитет

Совета Министров СССР но делам нзооретеннй н открытий (23) Приоритет (43) Опублнковано05.11.76,Бюллетень № 41 (4б) Дата опубликования описания21.02.77 (53) УДК 681. 374 (088,8) (72) Автор. изобретения

В. А. Горохов

Всесоюзный заочный электротехнический институт связи (71) Заявитель (54) МАТРИЧНЫЙ КОММУТАТОР

Изобретение относится к автоматике и ттеле механике, Известны матричные коммутаторы, содержащие тиристорные ключи и схемы управ,ления: и выборки (l) .

Эти устройства содержат большое число ,элементов.

Известен .,также . матричный коммутатор, содержащий g двухпроводных информацион- 10 ных входных каналов и М двухпроводных нформационных выходных каналов, М уп- авляющих горизонтальных проводов и М уй авляютцих вертикальных проводов, матри-

К+И тиристоров, источники питания анод- (5

ык цепей тиристоров, Й+ М согласующих стройств передатчиков, каждое из которьос одержит делитель напряжения, и К+ М сргласующих устройств приемников, каждое из

oTDpblx содержит ключ-инвертор, подсоединю 20 енных попарно к каждому входному и вы- иодному информационньп4 каналам, K+M двусторонних точек коммутации на тиристоре, ттодключенном анодом к одному из управля- тощих горизонтальных проводов и катодом 25

2 ( к общей точке, цепь управления состояние 1 тиристора и транзисторы (2).

Это устройство сложно и потребляет боФь Шую мощность.

Бель изобретения - упрощение схемы и

1 уменьшение потребляемой мощности — дос

: гигается тем, что в матричном коммутато-! 1 ре, содержащем Й двухпроводных информационных входных каналов и М двухпрово,. ых информационных выходных каналов,, тт равляющих горизонтальных проводов и М

1 авляюших вертикальных проводов, матицу К + М тиристоров, источники питания

; нодных цепей тиристоров, N + М согласу !

Ьших устройств передатчиков, каждое из ко.торых содержит делитель напряжения, и N+! + М согласующих устройств приемников, каждое из которых содержит ключ-инвертор, одсоединенных попарно к каждому входному выходному информационным каналам, К+М

1. двусторонних точек коммутации, каждая ив которых содержит тиристор, подключенный .анодом к одному из управляющих г оризонтальнЬа

1 ! проводов и катодом к обшей точке, цепь управления состоянием тиристора и транзис534871 торь:, согласующее устройство передатчика каждого канала через первый информационый провод подключено к базам одной груть! пь. транзисторов данного канала, а согласующее устройство приемника этого канала

t ерез второй информационный провод подлючено к коллекторам другой группы тра Ьисторов данного канала, эмиттеры тр узис1 оров из каждой группы объединены попар- но и каждая пара эмиттеров подсоединена р р одному иэ анодов тирис горов данного канала, причем цепь управления каждого тиистора содержит последовательно соединен ь>й дополнительный диод, а каждый вертиальнь и управляющий провод через допол- 5 ительно введенные диод и ключ подсоединен обшей точке, каждый горизонтальный уп равляющий провод через дополнительныйдиод резистор подключен к источнику анодного питания. О

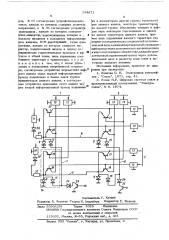

Схема устройства изображена на чертеже.

Матричн.:." коммутатор содержит И aaykпроводных информационных входных каналов

1, 2 и М двухпроводных информационных вь -Ь ходных каналов 3, 4, И вЂ” управляющих го-ризонтальных проводов 5, 6 и М управлякнших вертикальных проводов 7, 8 матрицу тиристоров 9, источники анодного питания

10, 11 анодных цепей тиристоров, Й+М c+> йасуюших устройств передатчиков, каждое з которых содержит делитель напряжения

3.2, и Й + М согласующих устройств прием ников 13, каждое из которых содержит клк чертор подсоединенных попарно I: Kayo му входному и выходному информационным

}каналам 1-4, К+М двусторонних точек комМутации 14, каждая из которых содержит тиристор 9, подключенный анодом к одному, иэ управляющих горизонтальных проводов

5, 6 и катодом к общей точке, цепь управдения состоянием тиристора 15 и транзисторы 16-23, согласующее устройство nepei датчика на делителе 12 каждого канала под ключено к базам одной группы транзисторов

16, 18 данного канала, а согласующее устройство приемника 13 этого канала — к колiremopy другой группы транзисторов 17, 19 данного канала, эмиттеры транзисторов 16

17 и 18, 19 из каждой группы объединень > опарно и каждая пара эмиттеров подсоедина к одному из анодов тиристоров 9 дан- ного канала, причем цепь управления каждого тиристора содержит последовательно соеди- юенный дополнительный диод, а каждый верб (гикальный управляющий провод 7, 8 через дополнительно введенные диод 24 и транзисI гор 25 подключен к общей точке, каждый

: горизонтальный управляющий провод 5, 6 1

:через дополнительный диод 26 и резистор

27 подключен к источникам 10, 11, Устройство работает следующим образом, В исходном состоянии все тиристоры 9 выключены, Двоичные импульсно-потенциал ые сигналы, поступающие по информацион- ным горизонтальному и вертикальному прово дам из передатчиков на делитель 12, не вызывают изменения состояния транзисторов

16 и 18, транзисторов 19 и 21, так как I

i тиристоры 9, включенные в цепи эмиттеров этих транзисторов, представляют большое сопротивление (выключены), и базовые от пираюшие токи практически равны нулю.

Соединения между входящими и исходящими каналами устанавливаются следующим образом.

Ймпульсный сигнал управления поступает на транзистор 25 и на источник питания

10 анодных цепей тиристоров.

В результате включается источник 10, на аноды тиристоров 9 подается напряжение, а кх управляющие электроды подключаются через тиристор 15 и открытый транзистор

25 к общей точке. Поэтому через управля ощий электрод тиристора 9, соединенного

Р транзисторами 18, 19, начинает проте- кать управляющий ток, и он включается, на пряжение на анодах остальных тиристоров

I падает до остаточного напряжения на открь roM тиристоре, I

Длительность управляющего импульса для установления соединения, подаваемая на транзистор 25 и источник питания 10 анодных. цепей, должна превышать сумму времен включения источника питания. Импульс питания должен заканчиваться до поступления следующего сигнала управления установления doeдинения. Источник питания 10 должен быть включен в течение всего времени соединения канал ов.

Сигнал отбоя поступает на источник 101 результате тиристор. 9 обесточивается и переключается в закрытое состояние. Такий образом, каналы оказываются разомкнутыми. В качестве источников питания 10 и 11 мо1 гут быть использованы триггеры со счетным входом.

Формула изобретения т

Матричимй:: Коммутатор, содержащий Й двухдройфйьа..итнформационных входных ка алов и .М. и@ухЩ Оводных информационных выходных кй49лсе,.,й управляющих горизоц тальных проводов":и М управляющих верти- кальных проводов, матрицу К+М тиристоров, источники питания анодных цепей тиристо534871

Составитель Г. Кутний

Редактор Б. Федотов Техред Н. Андрейчук . Корректор С. Щекмар

Заказ 5530/258 Тираж. 1029 Подписное

UHHHHH Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент, r. Ужгород, ул. Проектная, 4 ров, N +М согласующих устройствпередат» чиков, каждое. иэ которых содержит делитель напряжения, и N +М согласуюшни устройс и приемников; каждое из которых содержит люч -инвертор, подсоединенных попарно к d аждому входному и выходному информашиным каналам, K+M двусторонних. точек комутации, каждая из которых содержит тиристор; подключенный анодом к одному из! пр&вляюших горизонтальных llpoBogoB и ка- !О одом к обшей точке, цепь управления сос . тоянием тиристора и транзисторы, о т л и-. а ю ш и и с я тем, что, с целью упро- ) ,щения и уменьшения потребляемой,мощнос! 5 тии согласующее устройство передатчика кв кого канала через первый информационный ровод подключено к базам одной группы транзисторов данного канала, а согласуюi

joe устройство приемника этого канала че ез второй информационный провод подключе6 о к коллекторам другой группы транзистор

I ов данного канала, эмиттеры транзисторов

I у э каждой группы объединены IIDTIBpHD и каж:дая пара эмиттеров подсоединена к одному кз анодов тиристоров данного канала, приИем цепь управления каждого тиристора со- держит последовательно соединенный дополнительный диод,а каждый вертикальный управляю- ( щий провод через дополнительно введенные диод и ключ подсоединен к общей точке, каждый горизонтальный управляющий провод через дополГ нительный диод и резистор подк.;очен к источнику анодного питания, Источники информации, принятые во: вни мание при экспертизе:

1. Иванова О, Н. Электронная коммутф. ция . "Связь", 1971, стр. 41.

2, Поляк М,У, цифровая система связи а пространственной коммутацией. "Электро,связь", % 8, 1974,