Устройство для обнаружения ошибок в преобразователе циклического кода

Иллюстрации

Показать всеРеферат

(6)) Дополнительное к авт. Саид-ву (51) М. Кл. (-(O4 (8!O2 (22) Заявлено 26,12.74 (2j) 2088834/24 с присоединением заявки №

Государственный иемитет

Сонета Министров СССР еа делам нзе6ретений и етнрытий (23) Приоритет (43) 0 тубликовано05, 1.75о.Бюллетень № 41 (53) УДу 881 828 (Д88 88) ((4О) ((атв ОП1«бли«- GB H?IR ash,.:,",«ч (- 1 г, «

A. Л. (еля,.<ов, (:3,. ., <алев-;в. „(!-;, Г ;;;.;,. ева

«

Л ?(Мике @an ò и Л д 1. ч (т (72) Авторь изобретения

: ентральныи на- чно-исследовательскпи институт связи (О 4) v< (РО (((ВО, ((Я;,"(Й P ; с1., t. (-!"|,,,(?(О(ДИВО(В ПРЕОЬРАЗОВ47:. )}., Б(((;ЛИ -«т С О (Р " О-iy

Изобретение относится к области передачи данных по каналам связи.

Известны устройства для обнаоуженияошибОк В преООразователях циклическОГО кода.

Одно из известных устоойств содержит деЬ шифратор, элементы И, ИЛИ и НЕ (1) Недостатком такого устройства является то, что решение об ошибке В кодопреобразователе не может быть приня-,о быстрее, чем;о истечении времени т= 2(т, + 4> 3, Где время распространения сигнала по прямому или обратному каналу связи, t, — время реакции приемника оконечного пункта на полученный сигнал или кодовую комбинацию, Наиболее близким техническим решением

А «3 к данному изобретению является устройство, которое содержит блок управления, два триггера, четыре элемента И, элемент ИЛИ. При этом выходы первого триггеоа соединены " первыми Входами первогс и второго э-reìåê- О тов И, выходы которых соединены со входами элемента ИЛИ (2)

В этом устройстве решение Об отказе преобразователя циклического кода принимается при несовпадении сформированных про- рВ

Верочных разядов " ожидаемыми проверочными разрядами для заранее известной кодовой комбинации, поступление которой навход и зеобразователя циклическогс кода является с Tajgaòj-" èþì неправ * льной раООты самОГО преобразователя и реакции на этот факт противо

1. ОложнОГО ОконечнОГО пункта связи.

Недостатком этого устройства является необходимость значительного времени для фор верования сигнала an отказе преобразователя.

Белью изобретения является повышение быстродействия устройства.

С этой целью в предложенное устройство введены группа элементов И, регистр и элемент 1.(— НЕ, поичем ВходОм устройстВа является Второй вход первого элемента И, Выход элемента ИЛИ является первым выходом устройства и соединен со входомпреОбразователя циклического кода, Первый выход блока управления соедичен с единичным

Входом первого тр Гггера и с первыми входами гру элементов И вторыевходы которых соединены с прямыми выходами преобразо534877 вателя циклического кода. Выходы группы элементов И соединены со входами регистра, выход которого соединен со вторымвходом второго элемента И. Второй выход блока управления соединен с нулевыми входами 5 первого и второго триггеров. Инверсные выходы преобразователя циклического кода соединены со входами третьего элемента И, выход которого соединен с единичным входом второго триггера и с первым входом элемента И-HE. Единичный выход второго триггера соединен со вторым входом элемента И-НЕ, выход которого соединен с первым входом четвертого элемента И. Третий выход блока управления соединен со вторым входом четвертого элемента И, выход которого является вторым выходом устройства.

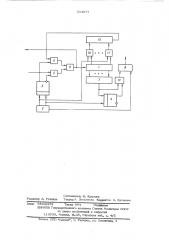

На чертеже изображена блок-схема устройства для обнаружения ошибок в преобразователе циклического кода.

Устройство содержит преобразователь циклического кода 1, блок управления 2, триггеры 3 и 4, элементы И 5-8 и элемент ИЛИ 9. Выходы триггера 3 соединены с первыми входами элементов И 5,6, вы25 ходы которых соединены со входами элемента ИЛИ 9.

Кроме того, устройство содержит группу элементов И (на чертеже изображены первый 10 и последний 11 элементы И гру30 пы), регистр 12 и элемент И-НЕ 13. Вход устройства ("информация от абонента" ) соединен со вторым входом элемента И 5.Выход элемента ИЛИ 9 соединен с первым выходом устройства ("информация в канал связи ) и со входом преобразователя 1,первый выход блока управления 2 ("конец информации") соединен с единичным входом триггера 3 и с первыми входами группы элементов И, вторые входы которых соединены с прямыми выходами триггеров преобразователя 1. Выходы группы элементов И соединены со входами регистра 12, выход которого соединен со вторым входом элемента И 6. Второй выход блока управления 2 ("начало слова") соединен с нулевыми входами триггеров 3 и 4. Инверсные выходы триггеров преобразователя 1 соединены со входами элемента И 7, выход которого соединен с единичным входом триггера 4 и с первым входом элемента И-НЕ 13. Единичный выход триггера 4 соединен со вторым входом элемента И-НЕ 13, выход которого соединен с первым входом элемента И 8. Третий выход блока управления 2 ("конец слова") соединен со вторым входом элемента И 8, выход которого соединен со вторым выходом устройства ("авария преобразователя" ). бО

Устройство работает следующим образом.

В исходном состоянии триггеры преобразователя 1 и регистра 12 находятся в нулевом состоянии, а триггеры 3,4 — в единичном. Перед поступлением информации от абонента по сигналу "начало слова" со второго выхода блока управления 2 триггеры 3 и 4 устанавливаются в нулевое состояние.

При этом сигнал разрешения с пулевоговыхода триггера 3 поступает на элемент И 5, сигнал запрета с единичного выхода триггера 3 — на элемент И 6, а сигнал запрета с единичного выхода триггера 4. — на элемент И-HE 13, с выхода которого сигнал разрешения поступает на элемент И 8. Таким образом, состояние устройства после сигнала начало слова таково, что при появлении на входе элемента И 8 сигнала

"конец слова с третьего выхода блока управления 2 на выходе элемента И 8 сформировался бы сигнал авария цреобразователя, поступающий на второй выход устройства. Но при отсутствии неисправностей во входных цепях и в преобразователе на преобразователь 1 после сигнала "начало слова" через элементы И 5, ИЛИ 9 начинает поступать информация, которая, кроме того, с выхода элемента ИЛИ 9 выдается на первый выход устройства в канал связи. При поступлении в преобразователь хо тя бы одной "единицы" информации нулевое состояние по крайней мере двух триггеров преобразователя изменяется на единичное, и на выходе элемента И 7 появляется сигнал, по которому триггер 4 устанавливается в единичное состояние (на чертеже показаны первый и последний входы элемента И 7). С единичного выхода триггера 4 на элемент И-НЕ 13 поступает сигнал разрешения, что является признаком отсутствия неисправности во входных цепях и служит одним из условий для определения исправности преобразователя.

B соответствии с теорией циклических кодов после окончания обработки информации в триггерах преобразователя 1 образуются проверочные разряды, при этом спервых прямых выходов триггеров, находящихся в единичном состоянии, на соответствующие входы группы элементов И поступают сигналы разрешения.

Число триггеров в преобразователе 1, регистре 12 и число элементов И в группе зависят от степени образующего полинома кода.

По сигналу конец информаций» с первого выхода блока управления 2 проверочные разряды параллельным кодом через соответствующие элементы И группы лере534877

О Устройство для обнаружения ошибок в преобразователе циклического кода, содержащее блок управления, qaa триггера, четыре элемента И, элемент ИЛИ, выходы первого триггера соединены с первыми входами перво-о и второго элементов vl, выходы которь(х соединены со входами элемента ИЛИ, о т (и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в устройство введены группа элементов И, регистр и элемент

И-НЕ, причем входом устройства является второй вход первого элемента И, выход элемента ИЛИ является первым выходом устройства и соединен со входом преобразователя циклического кода; первый выход блока управления соединен с единичным входом гервого триггера и с первыми входами группы элементов И, вторые входы которых соединены с прямыми выходами преобразователя циклического кода; выходы группы элементов И соединены со входами регистра, выход которого соединен со вторь;м входом второго элемента И; .второй выход блока управлепия соединен с нулевыми входами первого и второго триггеров; инверсные выходы преобразователя циклического кода соединены со входами третьего элемента И, выход которого соединен с единичным входом второго триггера и с первым входом элемента И-ПЕ; единичный выход второго триггера соединен со вторым входом элемента И-HF, выход которого соединен с первым входом четвеотого элемента И; третий выход блока управления соединен со вторым входом четвертого элемента И, выход котооого является вторым выходом устройства. писываются в регистр 12. Кроме того, по сигналу " конец информации" триггер 3 гереключается в единичное состояние, и сигнал запрета с нулевого выхода триггера 3 запрещает прохождение сигналов через элемент И 5, а сигнал разрешения с единичного выхода этого триггера разрешает прохождение сигналов через элементИ 6.

После этого проверочные разряды из регистра 12 поступают через элементы И 6, (ИЛИ 9 вслед за разрядами информации на первый выход устройства в канал связи и на вход преобразователя 1, который, начиная с этого момента, работает подобно декодируюшему устройству для циклических кодов.

Согласно теории циклических кодов после декодирования информационных и проверочных разрядов в декодиоующем устройстве должен образоваться нулевой остаток. Применитель- " но кданному устройству это означает, что все триггеры преобразователя 1 при исправной работе всего устройства, должны находиться в нулевом состоянии. При этом на выходе элемента И 7 появляется сигнал разрешен(я, гоступающий на вход элемента

И-НЕ 13, На выходе элемента И- г(Е 13 появляется сигнал, запреп. гющий прохождение чеоез элемент V. 8 сигнала "конец слова" с третьего выхода блока управления 2, по котооому с выхода элемента И 8 на второй выход устройства поступает сигнал "авария преооразова.(-еля", При неиспоавности в преобразователе 1 существует большая вероятность того, что хотя бы один из триггеgl.; ров треобразователя 1, по окончании операции вывода проверочных разрядов из регистч ра i2 будет находиться в единичном состоянии, и на вход элемента И 7 поступит сигнал с инверсного вь(хода три(-гера. находяшегося в едини (ном cD ) си((ни. (. этом с((учае на выход- элемента И 7 появляется сигнал запрета, поступаю(ций н; вход элемент(т(—,(,,-1 З та И-(-, (3. С вь(хода злемен-.а И-HF 13 сигнал разрешения поступает на элемент И 8, 46 и при пос плении сигнала "конец слова" с третьего выхода блока управления 2 с выхода элемента. И 8 на второй выход устоой1 ства поступает сигнал "авария преобразователя".

66

Таким ооразом, предлагае лое устройство гозволчет обнаружить ошибочну(о оаботу

i преобразователя циклического кода в случае непоступления информации на его вход или в случае неисправности в самом преобразователе сразу после возникновения ошибок, что значительно повышает его быстродействие.

Формула изобретения

Источники информации, принятые во внимание при экспертизе.

l. Иляпоберский В. И. Основы техники передачи дискретных сооб(цений, М., "Связь", 1973 г, стр. 470, рис. 10.2

2. Авторское свидетельство СССР

¹ 277588, Я. кл, G 06 F 5!00, 1969 г.

534877

Составитель В. Крылова

Редактор Л. Утехина Техред А. Демьянова Корректор H. Бугакова

Заказ 5503/252 Тираж 864 Подписное

ЫНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113С35, Москва, Ж-35, Раушскаи наб., д. 4/5

Филиал ППП»Патент», г. Ужгород, ул. Проектнщ 4