Устройство выхода мдп интегральных схем на индикатор

Иллюстрации

Показать всеРеферат

(») 5350I0

ОПИСАНИЕ

-ИЗОБР ЕТЕ Н И Я

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик,(61) Дополнительное к авт. сзид-av— (22) Заявлено 14,11.74 (21) 2075539/26-21 (51) Ч.1хл. Н 03 К 17/60 с присоединением за явки №вЂ”

Государственный комитет

1 6âåòà Министров СССР (23) Приоритет— (43) Опубликовано 30.09.78. Бюллетень ¹ 36 (45) Дата опубликования описания 07,09.78 (53) УДК 621.374.33 (088.8) ло делам, изобретений и открытий (72) Авторы изобретения

1О. В. Таякин, В. П. Сидоренко, А. Я. Сирота, 10. В. Прокофьев и А. М. Копытов (71) З.аявслтель (54) УСТРОЙСТВО ВЫХОДА МДП ИНТЕГРАЛЬНЫХ

СХЕМ НА ИНДИКАТОР

Изобретение отнооится к устройствам выхода информации с последовательным выводом на осчове схем динамической логики.

Известны устройства выхода МДП интегральных схем на индикатор, содержащие повторитель и .выходчой трансформатор.

Эти устройства потребляют значительную мощность, что обусловлено протеканием тоха в момент совпаденпля входных и тактовых импульсов (1).

Известны та кже устройства выхода ЧДП внтегральных схем на индикатор, содержащие,повторитель, выполненный на двух транзисторах, причем затвор первого транзистора соединен с:первой тактовой шиной, а сток второго — с второй тактовой шиной, и выходной транзистор (2).

Недостаточном этих устройств является перекрытие,по фронтам соседних (во времени) импульсов включения.

Цель изобретения — уменьшение потребляемой мощности и устранение перекрытия по фронтам соседних (во времени) импульсов включесчия.

Эта цель достигается тем, что в предложенное устройство введены зарядный и разрядный транзисторы, сток зарядного транзт стора соединен с выходом повторптеля, исток — со стоком разрядного транзистора и с затвором выходного транзистора, а затвор — с второй тактовой шиной. Исток разряд ного транзистора соединен с общей шиной, а запвор — с шиной разрядных пм5 пульсов. Сток первого транзистора повторителя соединен с входной шиной.

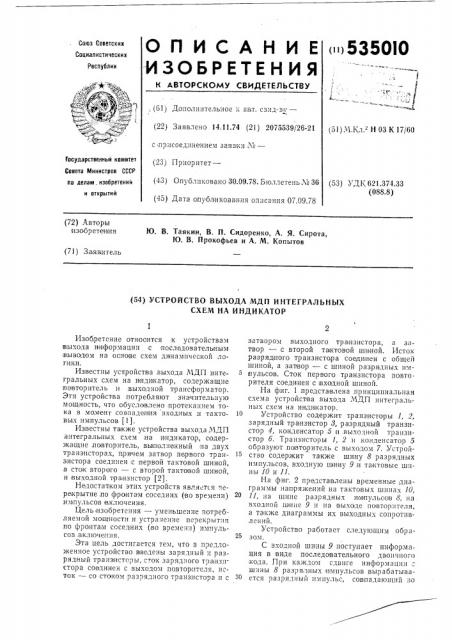

На фиг. 1 представлена .принципиальная схема устройства выхода ЧДП интегральных схем íà индикатор.

Устройство содержит транзисторы 1, 2, зарядный транзистор 8, разрядный транзистор 4, конденсатор 5 и .выходной транзистор б. Транзисторы 1, 2 и конденсатор 5 образуют повторитель с выходом 7. Устройство содержит также шину 8 разрядных импульсов, входную шину 9 и тактовые шины 10 и 11.

На фиг. 2 представлены временные диаграммы напряжений на тактовых шинах (О, 20 11, на шине разрядных импульсов 8, на входной шнне 9 и на выходе повторителя, а также диаграммы их выходных сопротивленийй.

Устройство работает следующим образо,м.

С входной шины 9 поступает информация в виде последовательного двоичного кола. При каждом сдвиге информации = шины 8 разрядных импульсов вырабатывается разрядный импульс, совпадающий во

535О1О

Г 1

Ю У-1 (s ) Pun f времени с одним из тактавых импульсов шины 10, который открьпвает транзистор 4.

При этом происходит разряд емкости затвора транзистора 6, и транзистор 6 закрывается. Одновременно с этим на входйую шину 9 поступает нсвая информация. Напряжение с входа передается на затвор транзистора 2 через транзистор 1 во время действия им пульсав с шины 10, При поступлении логического «0» на входную шину 9 1о емкость затвора транзистора 2 и конденсатор 5 к концу тактового импульса с шины

10 разряжаются, транзистор 2 запирается.

В результате ппънпульсы с транзистора 3 не проходят на выход 7 повторителя. П ри этом 15 заряда емкости затвора транзистора 6 не происходит, и он остается закрытым.

При поступлении логической «1» происходит заряд емкости затвора транзи".тора

2 и конденсатора 5. Транзистор 2 открыва- 20 ется и пропускает им пульсы с шины 11 на выход 7 по вторителя. Импульсы с выхода повторителя через транзистор 3 заряжают ем кость затвора транзистора 6, который за кр ыв а ется, 25

Таким образом в устройстве выхода

МДП интегральных схем на индикатор мощность потребляется только на перезаряд ку емкостей, а также иоключается перекрытие,по фронтам соседних (во времени) з0 им пульсов включения различных выходов, так ка к включение и выключение выходных транзисторов разнесено во времени.

Формула изобретения

Устройство выхода МДП ппнтегральных

cxeM I B индикатор, содержащее;повторитель, вьпполнеHíüãé на двух транзисторах, причем затвор первого транзистора соединен с первой тактовой шиной, а сток второго — со IBTopой та ктовой шиной, и выходной транзистор, отличающлйся тем, что, с целью уменьшения,потребляемой мощности III устра нения перекрытия по фронтам соседйих (во времени) импульсоз включения, введены зарядный и разрядный транзисторы, причем сток зарядного транзистора соединен c выходом .повторителя, исток — со стоком разрядного транзистора и с затвором выходного транзистора, а затвор — с второй тактовой шиной; при этом исток разрядного транзистора соединен с общей шиной, а затвор — с шиной разрядных им пульсов, сток пер ваго транзистора повторителя соединен с входной шиной.

Источники информации,,принятые во внимание при экопертизе:

1. Букреев И. Н, Мансурав Б. М., Горячев В. И. Мияроэлектрояные схемы цифровых устройств, М., «Саветокое,радио», 1973, с. 254. рис. 7, 8(в).

2. Кобболд Р. Теория aI применение полевых транзисторов, «Энергия», Л., 1975, с. 254, рис. 156.

9чг ччг

1Г—

7уг

Редактор Т. Колодиева

Подписное

Заказ 673/1001 Изд. № 647 Тираж 1263

НПО Государственного комитета Совета Министров СССР ио делам изобретений и открытий

Москва, 5К-35, Раушская наб., д. 4/5 Тии. Харьк фнл. пред. «Патент»

RB I» чг

Rgp„» чг

Составитель В. Трубников

Техред И. Рыбкина Корректор И. Симкнна