Преобразователь напряжение-код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ »> 535730

Сею Советских

Сециалиотичесхих

Ресаублии (61) Дополнительное к авт. свид-ву (22) Заявлено 15.09.75 (21) 2171772/21 (51) М. Кл."- Н ОЗК 13/02 с присоединением зая вки №

Совета Министров СССР но девам изобретений и открытий (53) УДК 681.325 (088.8) Опубликовано 15.11.76. Бюллетень № 42

Дата опубликования описания 22.11.76 (72) Авторы изобретения

Н. T Хромяк, В. А. Бердинских и В. М. Сахошко (71) Заявитель (54) П РЕОБРАЗОВАТЕЛ Ъ НАПРЯЖЕН И Е-КОД

Государственный комитет (23) Приоритет

Преобразователь напряжение-код предназначен Д,1я использования в вычислительнои

И ИЗМЕрИтЕЛЬНОт1 ГЕХНИКЕ И аВтОМатИКЕ, В Частности в входных устроисгвах управляющих

Нв1т1, цИ<ррОВЫХ ВОЛЬтМЕтраХ, ОнстЕМаХ автоматизированного контроля и регистрации параметро|в.

1звес гны преобразователи напряжение-код, состоящие из элементов памяти, схемы сравнения, нреооразователя код-напряжение и логических элементов управления ii). педостатком иэвостных у троиств является сравнительно невысокая надежность преОоразования. лроме того, известны преобразователи напряжение-код, содержащие генератор гактоВых импульсов, подключенныи к одному из

ВХОДОВ ьХЕМЫ ЗВПРЕта, ПРЕООРаэо ватЕЛЬ КОДНаПРЯ?КЕНИЕ, ВХОДЬI КО ГОРОГО ООЕДИНЕНЫ единичными выходами и элементов памяти, ВыхОд преобразователя код-Hdlipsl?KQHHB соединен с одним Входом схемы сраВнени?1, В1Оамон вход ко1орои подключьч1 к шине входного .шнала, d Выход соединен с Входами венгилси сороса, Выходы которых подключены к первым нулевым Входам элемен roB памяч и, причем вторые нулевые входы всех элементов памяти, кроме п-го, а также единичный вход и-ro элемента памяти подключены к шине начальной установки (2).

Однако извесгные преобразователи имеют сложную схему управлени> преооразователя код-напряжение, состоящую из п элементов памяти и и-разрядного сдвигающего ре1ист5 ра, предназначенного для управления элеисн ГНМИ ПаМЯГИ.

С целью упрощения схемы и повышения надежности преооразователя напряжение-код

В НЕГО ВВЕДЕНЫ ВЕНТИЛИ ПЕРЕНОСа, ВЕНТИЛИ Установки, триггер управления и вентиль триггера управления, при этом Выход тр11ггера уп раВ 1ения соединен с другич1 Входом схемы апрета, а его входы —,с шинои начальнои

15 установки и через вентиль триггера управления с единичным выходом пер|вого элемента памяти, а также с выходом схемы запрета и входами вентилеи переноса соро а и установки первого элемента памяти, Выход вентиля переноса каждого оолее младшего pddряда элемента памяти подключен к входам

Венiнлеи сороса переноса и установки элемен га памяти смежного сгаршего разряда, кроме п-го, а та|кже к входу Вентиля сороса и-10 элемента намя1 и, причем единичньш выход каждого элемента памяти, кроме первого, подключен к единичному входу предыдущего элемента памяти через соответствующий вентиль установки, а нулевой выход

30 каждого элемента памяти. кроме п-го, — к

535730

15

65 другому входу соответствующего вентиля переноса.

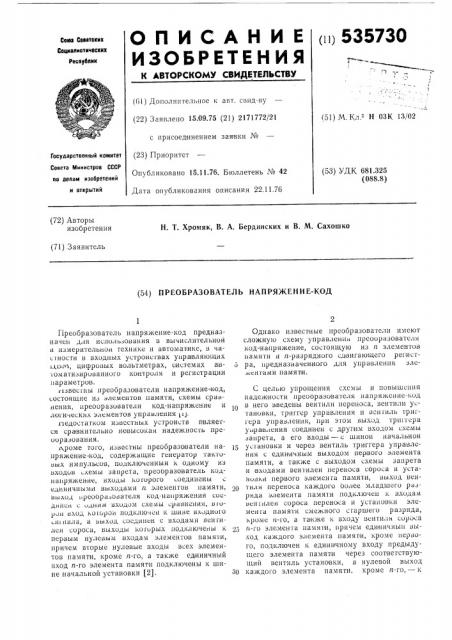

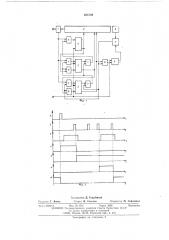

На фиг. 1 изображена структурная схема предлагаемого преобразо ватсля напряжениекод; на фиг. 2 — диаграмма его работы.

Преобразователь напряжение-код (фиг. 1) состоит из схемы 1 сравнения, преобразо вателя 2 код-на пряжение, и элементов 3 памяки, и вентилей 4 сброса, схемы 5 запрета, генератора 6 тактовых импульсов, и — 1 вентилей 7 переноса, n — 1 вентилей 8 установки, триггера 9 управления и вентиля 10 триггера у,правления.

11реобразователь напряжение-код начинает преобразование при поступлении импульса начальной установки (фиг. 2, а), по переднему фронту которого и-и элемент 3 памяти устанавливается в состояние «1» (фиг, 2, г), остальные элементы 3 памяти и триггер 9 управления находятся в состояние «0» (фиг. 2,д, е, ж). Потенциал с триггера 9 управления разрешает прохождение тактовых импульсов (фиг. 2,б) от генератора 6 тактовых импульсов через схему 5 запрета на вход вентилей 7 переноса. По потенциалу с единичного выхода

n ro элемента 3 памяти включается и-й разряд преобразователя 2 код-напряжение, а на вход схемы 1 сравнения поступает эталонное напряжение.

Предположим, что напряжение от источника входного сигнала меньше выработанного эталонного напряжения, при этом схема 1 сравнения формирует потенциал (фиг. 2, в), который по заднему фронту первого такто вого импульса с выхода вентиля 7 переноса через вентиль 4 сброса устанавливает и-й элемент 3 памяти в состояние «О» (фиг. 2, г).

Одновременно по зад нему фронту первого тактового импульса через вентиль b установки (n — 1)-й элемент 3 памяти устана вливается в состояние «l» (фланг. 2, д). 11о потенциалу с ед и н ичного выхода (n — 1) -:го элемента Л памяти включается (n — 1) -й разряд преобразователя 2 код-напряжение, при этом на вход схемы 1 сра внения поступает эталонное напряжение.

П редположим, что напряжение от источника входного сигнала больше выработанного эталонного напряжения, при этом на выходе схемы 1 сравнения (фиг. 2, в) отсутствует потенциал по пр иходу второго тактового импульса, (n — 1) -й элемент 3 памяти остается в со стояни и «1» (фиг. 2, д), а (и — 2)-й элемент 3 памяти устана вли вается в состояние «1».

Аналогично работают элементы схемы преобразователя при поступлении третьего, четвертого и т. д. (n — 1)-го тактового импульса.

По заднему фронту и-го тактового импульса изменяется или не изменяется (в зависимости от соотношения между входным и эталонным напряжением) состояние первого элемента памяти, и триггер 9 управления через вентиль 10 устанавливается в состоян ие

«1» (фиг. 2, д), причем схема 5 запрета запрещает дальнейшее прохождение тактовых импульсов íà вентили 7 переноса. Процесс прео бразован ия заканчивается. Благодаря использованию предлагаемого преобразо вателя напряжен ие-код, в котором управление процессом преобразования осуществляется элементами памяти без использования специального сдвигающего регистра, за счет экономи и триггеров и лопичеоких элементов существенно снижается стоимость и вес устрой ства (на 10 — 15%) по сра в нению с существующими на такой же элементной базе, кроме того, повышается надежность его работы.

Формула изобретения

Преобразователь напряжение-код, содержащий генератор тактовых импульсов, подключенный к одному из входов схемы запрета, преобразователь код-напряжение, входы которого соединены с единичными выходами и элементов памяти, а выход преобразователя код-напряжение соединен с одним входом схемы сравнения, второй вход которой подключен к шине входного сигнала, а выход соединен с входами вентилей сброса, выходы которых подключены к первым нулевым входам элементов памяти, причем вторые нулевые входы всех элементов памяти, кроме п-го, а также единичный вход и-ro элемента памяти подключены к шине начальной установки, отличающийся тем, что, с целью упрощения схемы и повышения надежности работы устройства, в него введены вентили переноса, вентили установки, триггер управления и вентиль триггера управления, при этом выход триггера управления соединен с другим входом схемы запрета, а его входы— с шиной начальной установки и через вентиль с единичным выходом первого элемента памяти, а также с выходом схемы запрета и входами вентилей переноса, сброса и установки первого элемента памяти, выход вентиля перено.а каждого более младшего разряда элемента памяти подключен к входам вентилей сброса, переноса и установки элемента памяти смежного старшего разряда, кроме n-ro, а также к входу вентиля сброса и-го элемента памяти, причем единичный IBbIход каждого элемента памяти, кроме первого, подключен к единичному входу предыдущего элемен i а памяти через соответствующий вентиль установки, а нулевой выход каждого элемента памяти, кроме и-го — к другому входу соответствующего вентиля пе. рено са.

Источникй йнформацйй, прийятые во ййй-. мание при экспертизе:

1. Патент Франции № 2150548 кл. Н 03К

13/00, 1973 r.

2. 3. И. Гитис «Преобразователи информации для электронных цифровых вычислительных машин», М, 1975 г., стр. 298 — 300, рис, 7 — 7а (прототип) .

535730

Фиг.1

Составитель Д. Голубоакин

Техред М. Семенов

Корректор М. Лейзермаи

Редактор Т, Янова

Типография, пр. Сапунова, 2

Заказ 2359/ll Изд. М 1751 Тираж 1029 Подписное

Ц1-1ИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4j5