Дешифратор рекуррентных последовательностей

Иллюстрации

Показать всеРеферат

< п 53573l

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз СоветскихСоциалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 05.03.73 (21) 1893745/09 с присоединением заявки № (23) Приоритет

Опубликовано 15.11.76. Бюллетень № 42

Дата опубликования описания 20.04.77 (51) М. Кл. Н ОЗК13/258

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.391.256 (088.8) (72) Авторы изобретения

Ф. Г. Гордон и Л. Х. Нурмухамедов (71) Заявитель (54) ДЕШИФРАТОР РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ яф gg «g ЕЯ "Iу

И =.Ж ff eye-гг

УЕ =ЮЮZS =У1ВУ1-кО М - n.

Mph - h ðМ

И=уй-к 9St /2

Изобретение относится к импульсной технике, предназначено для обработки и передачи данных и может быть использовано, например, в устройствах обмена служебными командами по каналам связи в автоматических системах управления.

Рекуррентную последовательность, генерируемую регистром с логической обратной связью, можно рассматривать как булеву функцию вида где у — значения функции в фиксированные моменты времени

Д+ — логическая операция «отрицание равнозначности».

Данная функция является периодической, максимальный период составляет 2" — 1 тактов.

Известно устройство (1) для дешифрации указанных последовательностей путем проверки входной информации на соответствие закону формирования рекуррентной последовательности, при этом входная информация yt с помощью регистра задерживается на k и и тактов и поступает на схему, осуществляющую логическую операцию «отрицание равнозначности»

- Далее сигналы zt сравниваются с входной информацией на схеме сравнения, осуществляющей также операцию «отрицание равнозначности»

После схемы сравнения сигналы Ut подаются на интегратор, выход которого является выходом дешифратора. Отсутствие «единиц» в последовательности Ut в течение т тактов при наличии информации на входе дешифра20 тора свидетельствует о том, что входная информация является рекуррентной последовательностью вида

Однако известное устройство обеспечивает дешифрацию рекуррентной последовательности только на одной, заранее установленной, 30 скорости передачи.

535731

У- =у .-кe yf -n уу -М-гк У - г, 25

И л = И -к — " ®У1 — 2n (3) зо

35 (4) (5) Так как

yt =й — к -n ©Уй-rr — rr

Вместс с тем, в автоматизированных системах управления при ухудшении качества каналов связи возникает необходимость понижать скорость передачи команд, например передавать служебные команды по стандартным каналам тональной частоты не на скорости

1200 бод, а на скорости 600 бод.

С целью обеспечения возможности работы на двух кратных скоростях передачи без соответствующего изменения в два раза тактовой частоты дешифратора в нем входы второго сумматора по модулю два подключены к отводам 2А и 2п сдвигового регистра.

Сущность предлагаемого изобретения состоит в том, что для рекуррентных последовательностей вида справедливо выражение,УЕ =Ю-к ЧУЯ-и =Я-Як®у -2л ° (2) При задержке исходной последовательности выражения (1) на Й тактов справедливо выражение (2).

Аналогично исходная последовательность выражения (1), задержанная на птактов,,может быть представлена выражением

И п =У г-n©У1 — 2л ф

Суммируя по модулю два выражения (3) и (4), получим у — к@gf л =У1 2кЮУ1- -n ЮУ -.,-л УŠ— 2л то из выражения (5) получим У1 У6-lгЕУЬ-л =УЕ-гк ЭЦЬ - гл

Таким образом, регистр с логическими обратными связями с разрядов 2k и 2п может быть использован в качестве дешифратора рекуррентной последовательности вида

yt=yt — x{+)yt — п при скорости передачи, равной тактовой частоте дешифратора. При скорости передачи в два раза меньшей, чем тактовая частота дешифратора, каждая информационная «единица» преобразуется в приемном - устройстве в комбинацию вида

«10», а каждый «О» — в комбинацию вида

«00», поэтому 2п-разрядный регистр с логическими обратными связями с разрядов 2k и

2п может рассматриваться как и-разрядный регистр с логическими обратными связями разрядов Й и п, если скорость передачи в два раза меньше, чем тактовая частота дешифратор а.

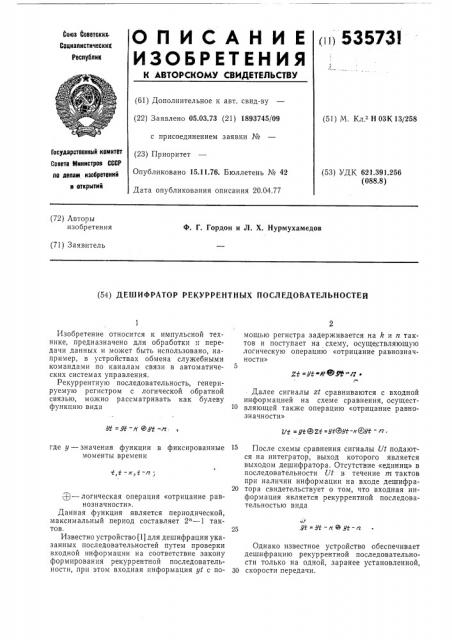

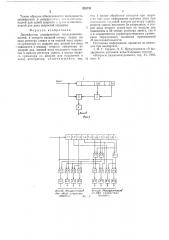

На фиг, 1 показана блок-схема предлагаемого устройства; на фиг. 2 — пример использования этого устройства в приемнике служебных команд и контрольных тестов аппаратуры управления.

Предлагаемый дешифратор содержит регистр 1, схемы 2 — 4 сложения по модулю два, интеграторы 5 и 6.

При скорости передачи, равной тактовой частоте дешифратора, устройство позволяет осуществлять проверку входной информации на соответствие закону формирования рекуррентной последовательности вида которая идентична последовательности вида, f =gt к©У - rz

При скорости передачи в два раза меньшей, чем тактовая частота дешифратора, устройство также осуществляет проверку входной информации на соответствие закону формирования рекуррентной последовательности вида

В регистре 1 логические обратные связи осуществляются, например, с разрядов 1 — 6, 1 — 7, 1 — 10 (фиг. 2). Выходы интеграторов

4-1 — 4-р являются выходами дешифраторов р рекуррентных последовательностей для одной (более высокой) скорости передачи. В приведенном на фиг. 2 примере выход интегратора 4-1 является выходом дешифратора последовательности yt=yt — 7{3 yt — 10 с периодом 2" — 1=1023 тактов.

Выходы интеграторов 4-2, 4-3, ... 4-р являются выходами дешифраторов рекуррентных последовательностей yt=yt — 5{ )у1 — 9 (период 2 — 1=511 тактов), последовательностей

yt=yt — 3(+) yt — 7 (период2 — 1=127тактов) и последовательностей yt= yt — 4(+)yt — 7 (период 2 — 1=127 тактов) соответственно.

Выходы интеграторов 6=1 — 6=0 являются выходами дешифраторов рекуррентных последовательностей для двух скоростей передачи, а именно: дешифратор 6-1 для последовательности yt=yt — 3(+)у1 — 5 (период 2 — 1=31 такт); дешифратор 6-2 для последовательноти

yt=yt — 1(+)yt — 3 (период 2 — 1=8 тактов); дешифратор 6-3 для последовательности у/= yt — 1 (+) yt — 4 (период 24 — 1 = 15 тактов); дешифратор 6-д для последовательности

yt=yt — 2+iyt — 5 (период 2 — 1=31 такт), 535731

Вход

Фиг,1 —

0p&l rPp0 0ðод я Лу crr gpbrmyg

:iРр ебЫi" дыхс3ы деиа<рр юаро3 длн вднх скоростпи л@рсрд". а/ Ф.;, z

Таким образом обеспечивается возмо>кность дешифрации р рекуррептпь. . последогательностей для одной скорости и г1 последовательностей для двух скоростей передачи.

Формула изобретения

Дешифратор рекуррентных последовательностей, в котором входной сигнал подан на вход регистра сдвига и на первый вход первого сумматора по модулю два, второй его вход

° подключен к выходу второго сумматора по модулю два, первый вход последнего подключен к выходу регистра сдвига, а выход первого сумматора по модулю два подключен к входу интегратора, отличающийся тем, что, с целью обработки сигналов при скоростях пер;дачи информации кратных двум при пеи=мснпой тактовой частоте регистра сдвига, регистр сдвига выполнен 2п разрядным, а второй вход второго сумматора по модулю два подключен к 2k отводу регистра сдвига, где и и k определяются характеристическим уравнением образующего полипом а принимаемой

М-последовательности.

10 Источники информации, принятые во внимание при экспертизе.

1. Ф. Г. Гордон, Л. Х. Нурмухамедов «О фазировании датчиков испытательных тестов».

«Вопросы радиоэлектроники», сер. XI, 1965, 15 вып. 6.