Цифровой коррелятор

Иллюстрации

Показать всеРеферат

<и) 536492

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Х АВТОР СХОМУ СВИДЕТЕЛЬСТВУ

Своз Сооетских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 24.07.74 (21) 2047504/24 с присоединением заявки— (23) Приоритет— (43) Опубликовано 25.11.76. Бюллетень М 43 (45) Дата опубликования описания 07.01.77 (51) М.Кл.2 G 06 F 15/34

Госуларстеонный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.323:519 2 (088.8) (72) Авторы изобретения

В. А. Гайский, О. М. Макаров и А. И. Ленин (71) Заявитель Морской гидрофизический институт АН Украинской ССР (54) ЦИФРОВОЙ КОРРЕЛЯТОР

Изобретение относится к вычислительной технике и предназначено для использования в измерительных информационных и вычислительных системах.

Известны корреляторы, содержащие блок согласования, запоминающее устройство, арифметический блок и блок управления (1).

Однако в таких корреляторах увеличиваетсч время анализа при увеличении числа определяемых ординат корреляционной функции.

Известен также цифровой коррелятор, содержащий блок согласования, блок умножения и блок накапливающих сумматоров (2).

его недостатком является низкая пропускная способность, а ее повышение требует пропорционального увеличения всего оборудования, в том числе блоков умножения, которые наиболее сложны в реализации.

Цель изобретения — повышение быстродействия коррелятора.

Для этого предлагаемый коррелятор содержит блок разложения кодов первого сигнала, блок разложения кодов второго сигнала и блок свертки, подключенный выходом к блоку накапливающих сумматоров, а входом— к выходу блока умножения, две группы входов которого соответственно соединены с выходами блоков разложения кодов первого и второго сигналов, входы этих блоков подключены к соответствующим выходам блока согласования.

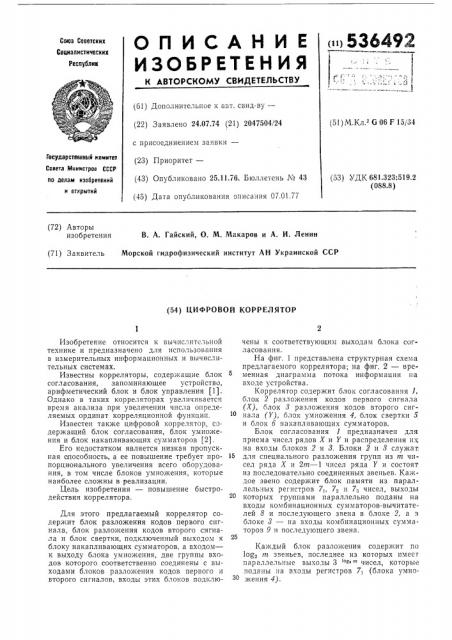

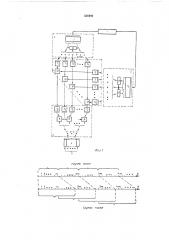

На фиг. 1 представлена структурная схема предлагаемого коррелятора; на фиг. 2 — временная диаграмма потока информации на входе устройства.

Коррелятор содержит блок согласования 1, блок 2 разложения кодов первого сигнала (Х), олок 8 разложения кодов второго сигнала (Y), олок умножения 4, блок свертки 5 и блок б накапливающих сумматоров.

Блок согласования 1 предназначен для приема чисел рядов Х и Y и распределения пх на входы блоков 2 и 8. Блоки 2 и 8 служат, 16 для специального разложения групп из т чисел ряда X и 2т — 1 чисел ряда Y и состоят из последовательно соединенных звеньев. Каждое звено содержит блок памяти из параллельных регистров 7ь 7, и 7, чисел, выходы которых группами параллельно поданы на входы комбинационных сумматоров-вычитателей 8 и последующего звена в блоке 2, а з блоке 8 — на входы комбинационных сумматоров 9 и последующего звена.

Каждый блок разложения содержит по

log m звеньев, последнее из которых имеет параллельные выходы 3 в чисел, которые поданы на входы регистров 7> (блока умно30 жения 4) 536492

Зо

Выходы входных регистров 7, блока умножения 4 от чисел разложения ряда Х соединены с первыми входами ячеек умножения

10 блока 4, а от чисел разложения У вЂ” со вторыми входами ячеек 10.

Выходы блока умножения 4 соединены с входами блока свертки 5, состоящего из последовательно соединенных звеньев, каждое из которых содержит узел памяти из параллельных регистров 7ь 7> и 7З, выходы которых группами параллельно соединены с входами комбинационных сумматоров-вычитателей 8, сумматоров 9 и входами последующего звена.

Блок свертки содержит log> m звеньев, т выходов последнего из которых поданы на входы накапливающих сумматоров блока б. На внешние выходы 11 коррелятора поданы старших разрядов накапливающих сумматоров блока б.

Элементы временной задержки и вентили, необходимые для перемещения информации между звеньями в блоках, цепи управления и блок управления на чертеже не показаны.

Коррелятор реализует специальный алгоритм умножения вектора размерностью N на матрицу Ганкеля размерностью m >< N и деУ ления произведения на v = logq — —. т

Достоинством алгоритма является высокое быстродействие и меньшее число операций умножения по сравнению с известными.

Коррелятор работает следующим образом.

Перед началом работы все регистры памяти обнулены. Из блока согласования 1 на входы первых звеньев блоков разложения 2 и 8 поступают параллельно m чисел ряда Х и

2m — 1 чисел, ряда Y соответственно. Далее работа коррелятора осуществляется по тактам, с каждым из которых происходит параллельный сдвиг информации последовательно через звенья блоков разложения 2 и 8, блока умножения 4 и блока свертки 5.

B êàæäîì звене блока разложенпя 2 происходит формирование трех групп чисел из каждой группы чисел, поступившей на вход звена, причем первая и третья группы образуются разделением входной группы на две половины, а вторая группа образуется вычитанием чисел первой половины из чисел второй половины в блоке комбинационных сумматоров-вычитателей 8.

В каждом звене блока разложения 8 происходит формирование трех непересекающихся групп чисел из каждой группы чисел, поступившей на вход звена, причем вторая группа образуется непосредственно из входнои второй подгруппы чисел, а первая и третья группы — путем суммирования чисел перьой и третьей подгрупп с числами второй подгруппы в блоках сумматоров 9.

Через log т тактов информация проходит все звенья блоков разложения 2 и 8 и поступает на ячейки умножения 10 блоков 4, с выходов которых поступает далее в блок свертки 5. В каждом звене блока свертки происходит формирование группы чисел из трех входных групп чисел суммированием чисел первой и второй групп и на блоке сумматоров 9 н вычитанием чисел второй группы из чисел третьей группы в блоке сумматоров-вычитателей 8.

Через 2+ 21og> m тактов информация поступает с выхода блока свертки 5,на входы накапливающих сумматоров блока б в виде суммы m частных значений корреляционной функции.

Новые группы чисел рядов Х и У подаются на входы блоков 2 и 8 уже,во .втором такте, 1N как это показано на фиг. 2. Через (— +

Щ

+ 21og т + 2) тактов вычисление заканчивается, при этом m значений корреляционной функции снимаются с v старших разрядов накапливающих сумматоров.

Вычисление автокорреляционной функции производится аналогичным образом при вводе в блоки 2 и 8 одного ряда чисел Х. Продолжительность одного такта работы коррелятора равна максимальному времени прохождения информации через звено разложения, умножения или свертки.

Формула изобретения

Цифровой коррелятор, содержащий блок согласования, блок умножения и блок накапливающих сумматоров, отличающийся тем, что, с целью повышения быстродействия, коррелятор содержит блок разложения кодов первого сигнала, блок разложения кодов второго сигнала и блок свертки, подключенный выходом к блоку накапливающих сумматоров, а входом — к выходу блока умножения, две группы входов которого соответственно соединены с выходами блоков разложения кодов первого и второго сигналов, входы этих блоков подключены к соответствующим выходам блока согласования.

Источники информации, принятые во внимание при экспертизе:

1. Мирский Г. Ч. Аппаратурное определение характеристик случайных процессов. Энергия, М., 1972.

2. Грибанов Ю. И., Веселова Г. П., Андреев В. Н. Автоматические цифровые корреляторы. Энергия, М., 1972, стр. 148 (прототип).

536492

7 !

1

1

Г

Г

I

1 !

I

1 ! !

Ф 4 е ° л

1

° °

4 vz. 7

/ pynnni чисел! г ° ° г т За ° ° 4m ° e e x

o ° o i Y

, 3m, °, Zrn г ° . °

ennui чисел