Устройство поэлементного фазирования приемников дискретных сигналов

Иллюстрации

Показать всеРеферат

< и 5366!2

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ссез ьсеетсеих

Сощиалистичесиии

Респу1лии (61) Дополнительное к авт. свид-ву— (22) Заявлено 13.09.74 (21) 2060087/09 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 25.11.76. Бюллетень № 43 (45) Дата опубликования описания 16.02.77 (51) М.Кл Н 04 L 7/08

1асудерстеенныи комитет

Ссеета Миннстрев СССР ле делам нз0сретений и Открытий (53) УДК 621.394.662 (088.8) (72) Автор изобретения

Ю. И. Попше (71) Заявитель ц" С,41@ ;! *т т Д (54) УСТРОЙСТВО

ПОЭЛЕМЕНТНОГО ФАЗИРОВАНИЯ ПРИЕМНИКОВ

ДИСКРЕТНЫХ СИГНАЛОВ

Изобретение относится,к технике связи и может использоваться при передаче данных.

Известное устройство поэлементсного фазирования содержит перемножители входного сигнала на весовые функции, соединенные с интегратор ом произведений, и блок сравнения результатов интегрирования.

Это устройство имеет пониженную точность фазирования особенно при наличии во входном сигнале исскажений типа «преобладаний».

Известно также устройство поэлементного фазирования, содержащее запоминающий элемент и задающий генератор, соединенный через делитель с селектором опережения и селектором отставания, другие входы которых подключены к входному блоку, а выходы селектора опережения и селектора отставания со ответственно через блок добавления и блок вычитания соединены с входами делителя.

Однако известное устройство не обеспечивает высокую устойчивость синхронизации приемников дискретной информации.

Цель изобретения — повышение устойчивости синхронизации приемников дискретной информации.

Для этого в устройство поэлементного фазирования, содержащее запоминающий элемент и задающий генератор, соединенный через делитель с селектором опережения и селектором отставания, другие входы которых подключены к входноМу блоку, а выходы селектора опережения и селектора отставания соответственно через блок добавления и блок вычитания соединены с входами делителя, введены дополнительные селектор опережения и селектор отставания, при этом соответствующие выходы делителя соединены с входами блока добавления и блока вычитания соответственно через дополнительные селектор опережения и селектор отставания, объединенные входы которых подключены к выходу входного блока, а другие входы — к выходам селектора опережения и селектора отставания соответственно через за|поминающий элемент.

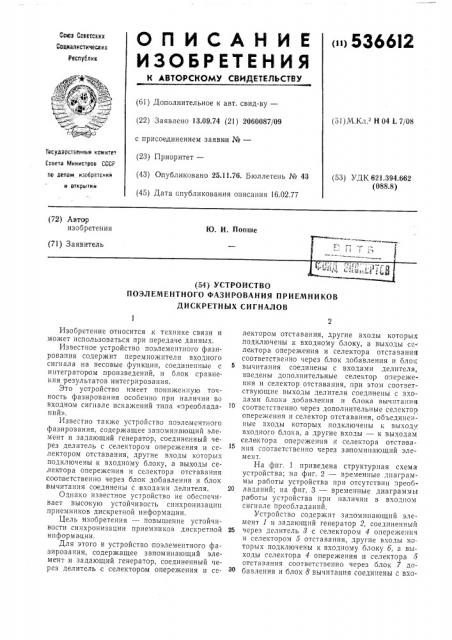

На .фиг. 1 приведена структурная схема устройства; на фиг. 2 — временные диаграммы работы устройства при отсутствии преоб20 ладаний; на фиг. 3 — временные диаграммы работы устройства при наличии в входном сигнале преобладаний.

Устройство содержит запоминающий элемент 1 и задающий генератор 2, соединенный

25 через делитель 8 с селектором 4 опережения и селектором 5 отставания, другие входы соторых подключены к входному блоку 6, а выходы селектора 4 опережения и селектора э отставания соответственно через блок 7 добавления и блок 8 вычитания соединены с вхо10

Зо

45 дами делителя 8, дополнительные "eJtåêòoð 9 опережения и селектор 10 отставания, при этом соответствующие выходы делителя 8 соединены с входами блока 7 добавления и блока

8 вычитания соответственно через дополнительныг селектор 9 опережения и селектор 10 отставания, ооъединенные входы которых подключены к выходу входного олока, à друг te входы —,к выходам селектора 4 опережения и селектора 5 отставания соотвгтствгнно через запоминающий элемент l.

Работа устройства при отсутствии преобладаний (см. фиг. 2).

В качестве входовой двоичной последовательности выбраны точки (см, фнг. 2 в), а за рабочий принят условно положительный сигнал. Определяющим сигналом для селекторов

4, 5, 9 и 10 являются соответствующие полупгриоды (см. фиг. 2 а, б) выходной частоты делителя 8. Входной блок б выделяет отдельно по обоим фронтам посылок короткие импульсы (см. фиг. 2 г, д). За основные приняты импульсы, формированные по положительным фронтам посылок (см. фиг. 2 г), а за дополнительные — по отрицательным (см. фнг. 2д). Все основные импульсы поступа!Ог через селектор 4 и селектор 5 на блок 7 илн блок 8 импульсов, ведущих подстройку фазы выходного сигнала делителя 8, и ta запоминающий элемент 1 с двумя устойчивыми состояниями, например, триггер с раздельными входами (диаграмма работы приведена на фиг. 2е, ж). Дополнительные нмпуль. ы поступают на дополнительные електор 9 и селектор 10, представляющие собой трехвхздовые схемы «И», управляемыг запоминающим элементом 1. На выходе дополнительных селектора 9 и селектора 10 импульсы, поступающие вместе с основны|!и (см. фнг. 2з) на блох 7 и блок 8, появляются тольхо в случае попадания этих импульсов в одноименную зону с предшествующими им основными импульсами, например, в зону отставания (см. фиг. 2), что определяется с помощью заломинающего элемента 1 и тех же сигналов с выхода делителя 8, которые поступают на селектор 4 и селектор 5. В этом случае подстройка фазы ведется,по обоим фронтам посыл ки.

Работа устройства при наличии в входном сигнале прго!бладаний (см. фиг. 3).

Она аналогична диаграммам, приведенным на фиг. 2, но в данном случае бестокозая .посылка преобладает над токовой (см. фиг. 3 в). Основ tt te импульсы попадают в зону отставания и соотзетственно на блок 8 вь!чигания и на запоминающий элеме !т l, которыи запоминает результат отставания. Запоминающий элемент 1 дает разрешаюгций потенциал HB дополнительный селектор 10 и запрещающий — на вход дополнительного селектора 9. Так как импульсы, выделенные по отрицательному фронту посылки (см. фиг.

3 д) попадают в зону опережения, а работа селектора 9 запрещена запоминающим элементом 1, они не попадают на блок 7 добавления, и по ним подстройки фазы нг произойдет.

Устройство функционирует аналогичным образом и при наличии преобладаний с о братным знаком.

Формула изобретения

Устройство поэлементного фазирозания прием!!ииов дискретных сигналов, содержащее запоминающий элемент и:àäàþùèé генератор, соединенный через делитель с селектором опережения н селектором отставания, другие входы хоторых подключены .х входному блоку, а выходы селектора опережения и селектора отставания соответственно через блок дооавления и блок вычитания соединены с входами делителя, о т л и ч а ю щ е ес я тем, что, с целью повышения устойчивости синхронизации прнемннхов дискретной информации, введены дополнительные селектор опережения и селектор OTcTBBBHttH, при этом соответствующие выходы делителя соединены с входами блока добавления н оло a вычитания соответственно через дополнительные селектор опережения и селектор отстава ния, ооъединенные входы которых подключены к выходу:входного блока, а другие входы— и выходам селектора опережения и селектора отставания соответственно через запоминающий элемент.

P rz 1.,(, у g,ò ã;òò-(, с ууд (i

Я (1 Г ! ( (! !! ! !! !

Г!!! с / ! ( ((I (.(, (! — !— ( ( (!! (!!! (1 ! I! !

\ ( (1!

Фу2. 2

J — — Ч () ! I !

I ( (А; ! !! () I (,.(с (!

"!! с!! ! !

) (!! ((! ((! ! (( (( ( (I — - — — —.

1 1 (I :::1