Ячейка памяти

Иллюстрации

Показать всеРеферат

оатеитте т м

Ятефрфтф щ iVi

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ (ii) 537388

Союз Советски)б

Социслистическик

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 20.09.74 (21) 2062200, 24 с присоединением заявки № (23) Приоритет

Опубликовано 30.11.76. Бюллетень № 44

Дата опубликования описания 22.12.76 (51) М, Кл. б 11С 11/40

Государственный комитет

Совета Министров СССР (53) УДК 681.327.66 (088.8) по делам изобретений и открытий (72) Автор изобретения

И, H. Кабанов (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ

Изобретение относится к области вычислительной техники, в частности к запоминающим устройствам.

Известна ячейка памяти, используемая в запоминающих устройствах динамического типа, выполненная на биполярных и МДП-транзисторах. Однако эта ячейка имеет довольно низкое быстродействие в режиме считывания.

Известна также ячейка памяти, наиболее близкая по технической сущности к изобретению, содержащая МДП-транзистор записи, исток которого соединен с разрядной шиной, затвор — с числовой шиной записи, сток — с затвором транзистора считывания, сток которого подключен к базе буферного биполярного транзистора, числовую шину считывания.

Данная ячейка памяти обладает малым быстродействием, так как ток считывания мал, кроме того, при записи «О» требуется вывести из насыщения биполярный транзистор.

Цель изобретения — повышение быстродействия ячейки.

Это достигается тем, что исток МДП-транзистора считывания подключен к числовой шине считывания, коллектор буферного биполярного транзистора соединяется с подложкой

МДП-транзистора считывания, а эмиттер — с разрядной шиной. В результате этого ток считывания, протекающий через МДП-транзистор считывания, усиливается биполярным транзистором, а также отсутствует насыщение бипслярного транзистора, что повышает быстрсдействие.

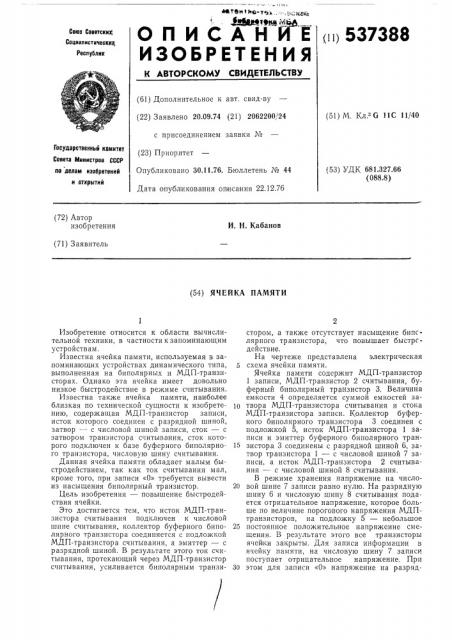

На чертеже представлена электрическая

5 схема ячейки памяти.

Ячейка памяти содержит МДП-транзистор

1 записи, МДП-транзистор 2 считывания, буферный биполярный транзистор 3, Величина емкости 4 определяется суммой емкостей затвора МДП-транзистора считывания и стока

МДП-транзистора записи. Коллектор буферного биполярного транзистора 3 соединен с подложкой 5, исток МДП-транзистора 1 записи и эмиттер буферного биполярного тран15 зистора 3 соединены с разрядной шиной б, затвор транзистора 1 — с числовой шиной 7 записи, а исток МДП-транзистора 2 считывания — с числовой шиной 8 считывания.

В режиме хранения напряжение на число20 вой шине 7 записи равно нулю. На разрядную шину 6 и числовую шину 8 считывания подается отрицательное напряжение, которое больше по величине порогового напряжения МДПтранзисторов, на подложку 5 — небольшое

25 постоянное положительное напряжение смещения. В результате этого все транзисторы ячейки закрыты. Для записи информаци и в ячейку памяти, на числовую шину 7 записи поступает отрицательное напряжение. При

30 этом для записи «О» напряжение на разряд537388

Формула изобретения

Составитель В. Фролов

Техред М. Семенов Корректор Т. Добровольская

Редактор И. Грузова

Заказ 2590/18 Изд, Хв 1830 Тираж 723 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ной шине 6 равно нулю, а при записи «1» на ней образуется высокий отрицательный уровень напряжения.

Емкость 4 перезаряжается до напряжения на разрядной шине 6 через открытый МДПтранзистор записи.

В режиме считывания на числовой шине 8 считывания устанавливается нулевое напряжение. При хранении на емкости 4 высокого отрицательного потенциала («1») МДП-транзистор считывания открывается, вследствие чего открывается и биполярный буферный транзистор 3. При этом напряжение на разрядной шине 6 становится близким к нулю.

Если же емкость 4 была заряжена незначительно (т. е, хранила «0»), то МДП-транзистор считывания не открывается и напряжение на разрядной шине 6 не изменяется.

Применение в интегральном динамическом запоминающем устройстве данной ячейки памяти вместо ячейки на трех МДП-транзисторах позволит повысить ее быстродействие при тех же размерах кристалла и сравнительно простой технологии.

Ячейка памяти, содержащая МДП-транзистор записи, исток которого соединен с раз10 рядной шиной, затвор — с числовой шиной записи, сток — с затвором МДП-транзистора считывания, сток которого подключен к базе буферного биполярного транзистора, и числовую шину считывания, отличающаяся

Гб тем, что, с целью повышения быстродействия ячейки, исток МДП-транзистора считывания подключен к числовой шине считывания, коллектор буферного биполярного транзистора соединен с подложкой МДП-транзистора счи20 тывания, а эмиттер — с разрядной шиной.