Двухтактный п-разрядный сумматор накапливающего типа

Иллюстрации

Показать всеРеферат

. теитно-тех им изскМ нет библиотека МБА

ОП HCAHHE

Союз Советских

Социалистических

Республик у (11) 53S365

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву(22) Заявлено 22.04.74 (21) 2018498/24 с присоединением заявки №(23) Приоритет— (43) Опубликовано05.12.76,Бюллетень №45 (45) Дата опубликования описания 30.03.77 (51) М. Кл и

906 7/50

Госудааственный комитет

Совета Министров СССР па делам иэаоретений и открытий (53) УДK 681.332 (088.8) (72) Автор изобретения

Б. М. Власов (71) Заявитель (54) ДВУХТАКТНЫЙ п -РАЗРЯДНЫЙ СУММАТОР

НАКАПЛИВАЮЩЕГО ТИПА

Изобретение относится к области автоматики и цифровой вычислительной техники и может быть использовано при реализации технических средств UBM.

Известны двухтактные накапливающие 5 сумматоры (1), выполненные на триггерах со счетным входом, на логических элементах И, ИЛИ, НЕ. Недостатком известного устройства является его сложность.

Наиболее близким техническим решением 1О к данному изобретению является двухтактный n — разрядный сумматор накапливающего типа, содержащий в каждом (. -ом разряде (ь = 1,2, ... n ) триггер типа

К вЂ” 5, установочные входы которого подклю- чены к выходам двух элементов "И", одни из входов которых соединены между собой и подключены к выходу первого элемента

"ИЛИ, выход второго элемента "ИЛИ" соединен с другим входом первого элемента 20

"И" и через элемент "HE" с другим входом второго элемента "И", выход которого подключен через второй элемент "НЕ" ко входу третьего элемента "И и с одним из входов четвертого элемента "И", соответствуюшие входы второго элемента "ИЛИ" соединены с выходом третьего элемента

"И", другие входы которого подключены к первой шине управления и инверсному выходу триггера соответственно, со второй шиной управления и с выходом первого элемента "И", элементы "И", "ИЛИ", а также цепь формирования сквозного переноса и шины управления работой сумматора PQ.

Недостатком этого устройства является наличие триггеров со счетным входом и элементов задержки сигналов, что усложняет устройство и снижает его быстродействие.

Целью изобретения является упрощение устройства и повышение его быстродействия.

Поставленная цель достигается тем, что в предложенном устройстве входы первого элемента "ИЛИ" соединены с выходами пятого и шестого элементов "И", первые входы которых подключены к соответствующим шинам управления. Второй вход пятого элемента "И" соединен с одним из входов седьмого элемента "И", другой вход которого подключен к инверсному

538365 выходу триггера, и с информационной шиной устройства, а другой вход шестого элемента соединен со вторым входом четвертого элемента "И" и с шиной переносов ((. + 1}го разряда. Выходы четвертого и седьмого элементов "И" подключены ко входам третьего элемента "ИЛИ, третий вход которого соединен с выходом первого элемента "ИЛИ (- — 1)-го разряда.

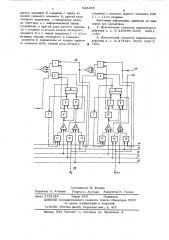

На чертеже приведена функциональная ® схема двухтактного сумматора (для двух разрядов).

Сумматор содержит элементы "И" 1,2, элемент "ИЛИ" 3, триггеры 4, элементы

"И" 5,6, элементы "HE" 7,8, элементы

"ИЛИ" 9, 10, элементы "И 11-13, шину разрешения инвертирования кода 14, шину управления 15, шину логических операций и гашения переноса 16, шину выдачи кода второго слагаемого 17, шину инвертирова20 ния кода сумматора 18, информационную шину 19, шину переноса из i — 1 разряда

20.

Устройство работает следующим образом.

В исходном состоянии код первого слага 25 емого хранится в регистре сумматора ! триггеры 4). Код второго слагаемого поступает в сумматор по шине х

По первому временному такту выполняется элементарная операция сложения по модулю 2, Для ее выполнения на шину

14 подается разрешающий потенциал, а на шину 17 — исполнительный импульс.

Если в триггере 4 хранится код нуля, то на входе элемента И 11 имеет место сов падения трех сигналов низкого (высокого) уровня . Соответственно на выходе элемента И 11 будет сигнал, который через элемент ИЛИ 9 поступает на вход элемен- > та И 6. На потенциальном входе элемента И 5 сигнал отсутствует, так как элемент HE 8 инвертирует единичный сигнал с выхода элемента ИЛИ 9. Если код второго слагаемого в рассматриваемом раз- 4 ряде равен единице, то исполнительный импульс по цепи: элемент И 12, элемента ИЛИ 10, поступает на входы элементов И 5,6. Так как на входах элемента

И 6 совпали два единичных сигнала, то 50 исполнительный импульс поступает на единичный вход триггера 4 и устанавливает его в единичное состояние. Предварительный импульс с выхода элемента И

6 поступает на вход элемента ИЛИ 9 и 55 далее на вход элемента И 6, что обеспечивает поступление исполнительного импульса только на единичный вход триггера 4. Таким образом, переключение триггера из одного состояния в другое не 60 вызывает изменения условий управления элементов И 5, 6 и 1. Кроме рассмотренной цепи, импульс с выхода элемента ИЛИ

10 i --го разряда поступает на вход элемента ИЛИ 3 младшего разряда. В связи с тем, что триггер 4 переключался из нулевого в единичное состояние, импульс с выхода элемента ИЛИ 3 младшего разряда через элемент И 1 не проходит.

Если в исходном состоянии в триггере

4 хранился код единицы, то исполнительный импульс по цепи: элемент И 12, элемент ИЛИ 10, элемент И 5, поступает на нулевой вход триггера 4 и переключает его в нулевое состояние. Условия прохождения импульса только на нулевой вход триггера 4 обеспечены тем, что на входе элемента И 11 нет совпадения трех сиг налов, на выходе элемента И 11 — нулевой потенциал, а на входе элемента И 5 — высокий потенциал за счет инвертирования нулевого потенциала элементом НЕ 8. IIeреключение триггера 4 в нулевое состояние не изменяет условия управления потенциальными входами элементов И 5,6, так как поступивший на нулевой вход триггера импульс через элемент НЕ 7 запрещает на время длительности этого импульса работу элемента И 11. И в этом случае условия управлением входами элементов И

5,6 и 1 сохраняются независимо от переключения триггера 4. Импульс с выхода элемента ИЛИ 10 через элемент ИЛИ 3 младшего разряда поступает на вход элемента И 1 и проходит в следующий старший разряд до переключения триггера 4, что сокращает время распространения переноса на время переключения триггера. Это повышает быстродействие работы устройства.

По второму временному такту формируется результат суммирования двух чисел. Как бьгло отмечено выше, формирование и рас..ространение переноса в (, -ом разряде начинается сразу же после появления первого исполнительного импульса.

Формирование поразрядного и сквозного переноса в i -ом разряде сумматора соответствует следующему логическому выражению

Р„=Х-„Y, VI (У 0,„У VY > где И,, — значение сигнала шины управле ния инвертированием; !

Y — сигнал на нулевом входе триг гера 4;

Y, — сигнал на единичном входе григгера 4.

538365 пульса на шину передачи инверсного кода. В этом случае исполнительный импульс через элемент ИЛИ 10 поступает на элемент И 5 и устанавливает в нулевое

S состояние триггер 4, т. е. в единичном состоянии остаются только триггеры тех разрядов, в которых значение кода второго сомножителя равно единице.

После распространения сигнала перено са на шину 15 подается импульс сложения. Если в i -й разряд поступил перенос из (L + 1)-го разряда, то импульс сложения по цепи: элемент И 13, элемент

ИЛИ 10, поступает на входы элементов И

5, 6 и производит инвертирование триггера 4. Если до прихода импульса сложения в триггере 4 хранился код единицы, сит нал переноса по цепи: элемент И 1, эле- 10 мент ИЛИ 3 поступает в старший разряд.

Если в i -ом разряде хранился код нуля, а второе слагаемое к „. равно единице, то при переключении триггера 4 прекращается выдача сигнала переноса в старший ра ряд, что при определенных обстоятельствах может привести к сбою работы устройства.

В рассматриваемом устройстве наличие связи выхода элемента ИЛИ 10 со входом элемента ИЛИ 3 исключает влияние

20 переключения триггера 4 на формирование переноса на время, равное длительности импульса сложения, что повышает надежность работы устройства.

Рассмотрим выполнение логических и вспомогательных операций, До начала выполнения логического сложения первое слагаемое хранится в регистре (триггер 4), а второе слагаемое поступает по шине Х . Для выполнения логического сложения на шину 16 подается потенциал разрешения выполнения этой операции, на шину 17 - исполнительный импульс. Если код второго слагаемого равен единице, то исполнительный импульс по цепи: элемент И 12 элемент ИЛИ 10 и элемент И 6, поступает на единичный вход триггера 4. Если код второго слагаемого равен нулю, то состояние триггера 4 не изменяется. Таким образом, сумматор реализует следующее логическое выражение: соответствующее логическому сложению кодов двух чисел.

До начала выполнения логического умножения первый код хранится в триггерах

4, а второй код поступает по шине х „

Как правило, в устройствах, выполняющих операции сложения и вычитания, предусматриваются логические элементы И для передачи прямого и инверсного кодов, хра- 55 няшихся в приемном регистре (на чертеже не показан). При наличии логического. элемента для передачи инверсного кода операция выполняется за один временный такт за счет подачи исполнительного им- 60

С целью сокрашения временных задержек в цепях переносов широко применяются схе мы групповых переносов сигналов. Для ускорения выключения логических элементов в цепях переносов применяются цепи гашения переносов. Для гашения гереносов в каждом разряде требуется как минимум один диод.

Предложенное устройство не требует дополнительного оборудования для выполнения этой вспомогательной операции, гашение переносов во всех разрядах осуществляется за счет подачи сигнала на шину 16.

Предложенное устройство выполнено только на трех типах логических элементов (И, ИЛИ, НЕ) и содержит один триггер на каждый двоичный разряд. При этом обеспечено повышение быстродействия и расширение функциональных возможностей устройства.

Формула изобретения

Двухтактный n — разрядный сумматор накапливающего типа, содержащий в каждом

1,-ом разряде (=1,2, ...n) триггер типа R- S, установочные входы которого подключены к выходам двух элементов И, одни из входов которых соединены между собой и подключены к выходу первого элемента ИЛИ. выход второго элемента ИЛИ соединен с другим входом первого элемента И и через элемент НŠ— с другим входом второго элемента И, выход которого подключен через второй элемент НЕ ко входу третьего элемента И и с одним из входов четвертого элемента И, соответствующие входы второго элемента ИЛИ соединены с выходом третьего элемента И, другие входы которого подключены к первой шине управления и инверсному выходу триггера соответственно, со второй шиной управления и с выходом первого элемента И, элементыИ,ИЛИ, отличающийся тем, что, с цепью упрощения устройства и повышения быстродействия, в нем входы первого элемента ИЛИ соединены с выходами пятого и шестого элементов И, первые входы которых подключены к соответствующим шинам управления; второй вход

5383

7 пятого элемента И соединен с одним из входов седьмого элемента И, другой вход которого подключен к инверсному выходу триггера, и с информационной шиной устройства, а другой вход шестого элемента — соединен со вторым входам четвертого элемента И и с шиной переносов (L+ 1)-ro разряда; выходы четвертого и седьмого лементов И подключены ко входам третьего элемента ИЛИ, третий вход которого 1О

8 соединен с выходом первого элемента ИЛИ (i- — 1)-го разряда.

Источники информации, принятые во внимание при экспертизе:

1. Двухтактный сумматор параллельного действия а. с. № 238890 СССР, 06

7/50.

2. Двухтактный сумматор параллельного действия а. с. № 275527, СССР, 506 6

7(50.

Составитель В. Белкин

Редактор Л. Утехина Техред Q. Луговая Корректор И. Гохсич

Заказ 5721/29 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4