Многопороговый логический элемент четности

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ биотока,"Ф,=! (11) 538490

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву(22) Заявлено 24.11.75 (21) 2192060/21 с присоединением заявки № (23) Приоритет— (51) Я. Кл

Н 03 К 19/12

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (43) Опубликовано05.12.76.БюллетЕнь №45 (53) УДК 621,373. 8 (088.8) (45) Дата опубликования описания 30.03.77

B. И. Потапов и И. A. Пальянов (72) Авторы изобретения (71) Заявитель

Омский политехнический институт (54) МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЧЕТНОСТИ

Изобретение относится к области импу .ьсной техники.

Известен многопороговый логический элемент содержащий прследовательно соединенные сумматор, функциональный преобразователь и дискриминатор.

Функциональный преобразователь содержит токовые переключатели, через диоды подключенные к дискриминаторам 1 1).

Данный элемент не может быть использован для большого числа входных сигналов.

Наиболее близким по технической сущности и достигаемому результату к изобретению является многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных диодов и резисторной матрицы, подключенный через разделительные диоды к резистивному делителю, соединенному с одними входами логических элементов И-НЕ, образующих многопороговый дискриминатор, второй вход каждого из которых соединен с выходом последующего логического элемента И-НЕ 52) Недостаток порогового логического элемента заключается в недостаточной точности при большом числе входных сигналов, 5 11ель изобретения — повышение точности при большом числе входных сигналов.

Поставленная цель достигается тем, что в многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных диодов и резисторной матрицы, подключенный через разделительные диоды к резистивному делителю, соединен15 ному с одними входами логических элементов И-НЕ, образующих многопороговый дискриминатор, второй вход каждого из которых соединен с выходом последующего логического элемента -HE, введен RS-триг20 гер, выполненный на двух дополнительных логических элементах И-НЕ, один вход триггера соединен с выходом последнего логического элемента -HE, входящего в многопороговый дискриминатор, второй его

25 вход соединен с источником стробируюше538490 становится достаточным для появления на выходе элемента 32 низкого уровня напряжения. На выходе 51 многопорогового логического элемента в этом случае появляется высокий уровень напряжения. При наличии положительных потенциалов на трех входах линейного сумматора срабатывает элемент 31, имеющий значение порога

Т = 7, при этом на выходе 51 многопорогового логического элемента устанавливается низкий уровень напряжения. Ток от источника питания через резистор 28 и диод 19 протекает через резисторы 3447 37 до тех пор, пока триггер на элемен р тах 38, 39 не изменит своего состояния на противоположное. А это произойдет в том случае, когда на входы линейного сумматора поступит 4 или более положительных сигналов. При этом на выходе р) логического элемента 30, имеющего значения порога Т = 8, установится низкий потенциал, триггер изменит свое состояние на противоположное. После этого ток через резистор 28 от источника питания

25 переключится в цепь диода 10, а на выходе 51 многопорогового логического элемента для реализации функции четности установится значение сигнала, определяемое входным воздействием. го сигнала, а выход триггера подключен к одному из входов линейного сумматора.

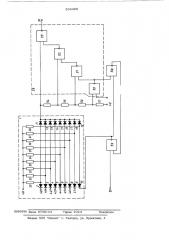

Структурная электрическая схема описываемого элемента приведена на чертеже

Многопороговый логический элемент четности содержит линейный сумматор 1, состоящий из диодов 2-19 и резисторов

20-28, образующих резистивную матрицу, многопороговый дискриминатор 29, состоящий из двухвходовых логических элементев И-НЕ 30-33, резистивный делитель из резисторов 34-37, триггер, образованный дополнительными логическими элементами И-HE 38, 39. На входы 40линейного сумматора поданы входные сигналы, на входы 48,49 — напряжение питания, на вход 50 — стробирующий импульс. Выходные сигналы снимаются с вы хода 51. Источник питания на чертеже не показан.

Принцип работы логического элемента заключается в следующем. В исходном состоянии диоды 2-9, связанные с входами 40-47, проводят ток от источника питания через соответствующие резисторы

20-27. Ток через резистор 28 от положи тельного полюса источника питания и диод

19 поступает в цепь последовательно соединенных резисторов 34-37 и далее к отрицательному полюсу источника питания. На выходе многэпэрэговэгэ лэгическзго элемента и выходах элементов И-НЕ 30-33 в этом случае присутствует уровень логической единицы„Входные сигналы в форме положительных потенциалов напряжения за- Ж пирают в любых комбинациях диоды 2-9.

Одновременно с поступлением входных сигналов на вход 50 поступает стробирующий импульс напряжения с амплитудой, эквивалентной логической единице, и длительностью, равной длительности входных сигналов.

Если положительный потенциал присутствует только на одном из входов линейного сумматора 1, то соответствующий диод запирается, и ток от источника питания через соответствующие резисторы 20-27 и соответствующие диоды 11-18 переключаются в цепь резисторов 34-37. При этом по- щ тенциал на выходе сумматора 1 становится достаточным для появления на выходе 51 низкого уровня напряжения, соответствующего логическому нулю. При наличии положительных потенциалов на двух входах ли- у нейного сумматора 1 соответствующие диоды 2 — 8 запираются и ток через резисторы 20 — 27 и диоды 11 — 19 от истэчника питания переключается в цепь резисторов 34 — 37. При этом потенциал @>

Формула изобретения

Многопороговый логический элемент четности, содержащий линейный сумматор, состоящий из входных диодов и резисторной матрицы, подключенный через разделительные диоды к резистивному делителю, соединенному с одними входами логических элементов И-НЕ, образующих многопорого вый дискриминатор, второй вход каждого из которых соединен с выходом последующего логического элемента И-НЕ, о т л ич ающийс я тем,что, с цельюповышения точности при большом числе входных сигналов, в него введен R5 -триггер, выполненный на двух дополнительных логических элементах И-НЕ, один вход триггера соединен с выходом последнего логического элемента И-НЕ, входящего в многопороговый дискриминатор, второй его вход соединен с источником стробируюшего сигнала, а выход триггера подключен к одному из входов линейного сумматора.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 438120, кл. Н 03 К 19/02 от 28.12.72, 2. Авторское свидетельство СССР № 319077, кл. Н 03 К 19/42 от 02.10.68. (прототип).

538490

1

I

Т

L ь М ? Мъ Со.Ф 4 Ч

) ЦНИИПИ Заказ 5730/34 Тираж 1024 Подписное

Филиал ППП "Патент" г. Ужгород, ул. Проектная, 4