Устройство индикации моментов, соответствующих началу и концу фронта импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ (;1(539373

Союз Советских

Социалистических

Республик.

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свил-ву (22) Заявлено 03.01.75 (21) 2092280,21 с присоединением заявки М (23) Приоритет

Опубликовано 15.12.76. Бюллетень ¹ 46

Дата опубликования описания 20.12.76 (51) М. К,1. - Н ОЗК 5, 153

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.378.18 (088.8) (72) Авторы изобретения

А. М. Коломацкий и Е. В. Сказочкин (71) Заявитель (54) УСТРОЙСТВО ИНДИКАЦИИ МОМЕНТОВ, СООТВЕТСТВУЮЩИХ НАЧАЛУ И КОНЦУ ФРОНТА ИМПУЛЪСОВ

Изобретение о(1(осится к области радиопзмерительной техники и может быть использовано в составе прибора для автоматического измерения длительности фронта импульсов.

Известно устройство, содержащее усилительный каскад, выход которого соединен со входами двух блоков сравнения непосредственно и через регуляторы уровней сравнения, выполненную в виде линии задержки (1).

Однако применение линии задержки в качестве схемы для получения уровня сравнения позволяет получить на выходах схем сравнения импульсы, соответствующие только минимуму и максимуму исследуемых импульсов формы, близкой к косинусоидальной, и не дает возможности исследовать импульсы произвольной формы и регистрировать момент начала и конца фронта импульса на любом уровне (не только в минимуме и максимуме).

Это объясняется тем, что линия задержки 20 только сдвигает исследуемый сигнал во времени и не позволяет регулировать уровни срабатывания.

Цель изобретения — исследование импульсов произвольной формы и регистрация мо- 25 ментов начала и конца импульса на любом уровне.

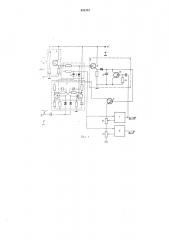

Это достигается тем, что в устройстве индикации моментов, соответствующих началу и концу фронта импульса, содержащее усили- 30 тель!(L(è 1 аcк;(д 11 два олоl а cpавпеп(!я, дополнительно введены коммутатор, блок управления коммутатором, например триггер с счетным входом, элемент памяти с разрядным ключом, согласующий каскад и регуляторы уровней сравнения, причем выход усилительного каскада через коммутатор соединен с входом элемента памяти и с первыми входами блоков сравнения, вторые входы которых через регуляторы уровней сравнения п согласующий каскад соед(шены с выходом элемента памяти, выход первого блока сравнения соединен с управляющим входом разрядного ключа элемента памяти, прп этом управляющие входы коммутатора соедш(ены с выхода>(1(блока управления ком ыутато1>оз(. вход которого соединен с шиной тактовых импульсов.

На фпг. 1 приведена схема предлагаемого устройства; на фиг. 2 — диафрагмы напряже(ПШ.

Устройство содержит усилительный каскад

1, коммутатор 2, триггер 3 со счетным входом, диоды 4, 5, элемент 6 IIQìÿò((, блоки 7, 8 сравнения, зарядный транзистор 9, конденсатор

10, транзистор 11 согласующего каскада, регуляторы 12, 13 уровней сравнения. дпфференцирующую цепочку 14, разрядный транз!(стор

15 и шину 16 тактовых импульсов.

1, Bb((O 1% (CI(.II(TC I »IIOCO 1 а с(.а1;l 1 IIO 11(IIOчсны регуляторы 12, 13 уровней cp;II(I(v((1»l, 539373 которые работают таким образом, что производят сравнение определенных частей амплитуды предыдущего импульса с нарастающим в течение фронта напряжением последующего импульса. Это достигается за счет того, что с выхода усилительного каскада 1 исследуемый сигнал подается па коммутируемый вход коммутатора 2. Сигналы управления коммутатором в виде положительного и нулевого потенциалов,поступают с выходов триггера 3. На его счетньш «ход от внешнего исто1)п ка по шине 1б подаются тактовые импульсы, следующие с частотой исследуемых импульсов и расположенные в промежутках времен. 1 между ними. На выходах триггера формируются импульсы с частотой следования, в два раза меньшей частоты исследуемых импульсов, и фронтами, соответствующими поступлению тактовых пмпугьсов (см. фпг. 2). Зги импульсы поочередно запирают диоды 4 и 5. Исследуемый импульс появляется па открытом выходе коммутатора.

Исследуемые импульсы поо«ередно пода:отся па вход элемента памяти 6 и на входы блоков 7 и 8. При поступлении исследуе.,(ого импульса па базу транзистора 9 конденсатор 10 заряжается до напряжения амплитуды импульса. )То папряяение подается па базу транзистора 11 согласующего каскада ii co) раняется там до прихода следукпцего импульса.

Соответственно, на входы блоков 7 и 8 сравнения поступают напряжения, составляющие определенную часть амплитуды измеряемых импульсоь н определяемые полояепияi»l ползунков регуляторов 12 и 13. Следующий из последовательности исследуемый импульс поступает на входы блоков 7 и 8. По мере нарастания напряжения в течение фронта, опо сравнивается с уровнями, определяемыми регуляторами 12 и 13. В соответствии с этим, íll выходах блоков сравнения появляются положительные импульсы, начало которых соответствует началу п концу фронта исследуемых импульсов на заданных уровнях. Положительный перепад, возникающий на выходе блока 7 сравнения и соответствующий концу фронта. через дифференцирующую цег..очку 14 подается »а базу разрядного транзистора !5, который открывается и разря)кает конденсатср 10, подготав;швая его к «запоминанию» амплитуды следун)щего импульса.

Необходимым условием сохранения неизменной амплитуды импульса на конденсаторе 10 до прихода следующего импульса, будет:

С,„, Rax(») >) т

R x(tI) = (Л(а) + Я((з)11)(») Т вЂ” максимальный период повторения исследуемых импульсов;

1)(») — коэффициент передачи по току транзистора 11. и где с1) ор м ул а изобретения

Источники информации, принятые во внп45 мыше прп экспертизс:

1. Патент ФРГ ¹ 1235992. кл. 21а, 19б7 (прототип).

Устройство ш)днкацllil моментов, соотвстст20 вующих началу и «овцу фронта импульсов, содержащее усилигельный каскад и два блока сравнения, отл и чаю щееся тем, что, с целью исследован»я»мпульсов произвольной формы II pCI.IICi.pBII,IIII моментов IIB IB;IB II кон25 ца импульса па л)обом уровне, в него дополнительно введены, коммутатор, блок управления коммутатором, например триггер с счетным ьходом, элемент памяти с разрядным ключом, согласующий каскад и регуляторы

3р уровней сравнения, причем выход усилительно о каскада через коммутатор соединен с в.,одом элемента памяти и с первыми входами олоков сравнения, вторые входы которых через регуляторы уровней сравнения и согласу35 ю1цпй каскад соединены с выходом элемента пам5)т, выход первого блока сравнения соеJIIIIQII с управляющим входо vl разрядного

I1л1Оч1! э Ic:51cíòà па A15ITII, 111) ll этом 1) ПР1)вл51ющие входы коммутатора ссединены с выхода40 ми блока управле);ия коммутатором, вход которого соединен с )ниной тактовых импульсов.

539373 Us». & сравни

1иВ . (a) cла» ((8о » (7) l ковда

Аlг. г

Ссставитель В. Лякишев

Редактор Н, Каменская Техред М, Семенов Корректор Л. Котова

Заказ 2766,, 16 Изд. ¹ 1852 Тираж 1029 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Я-35, Раушская наб., д. 4/5

Типография. пр. Сапунова, 2