Устройство для счета по переменному модулю

Иллюстрации

Показать всеРеферат

GnиС

ИЗОБРЕ

Союз Советских

Сацналистичесннх

Реслублни

К АВТОРСКОМУ (61) Дополнительное к а (22) Заявлено 17.04.75 (21) 2125136/21 с присоединением заявки № (23) Приоритет

Опубликовано 15.12.76. Бюллетень № 46

Дата опубликования описания 14.12.76 (51) М. Кл з Н ОЗК 21/34

Государственный комитет

Совета Министров СССР ло делам изобретений н OTKpblTNIl (53) УДК 621.375(088.8) (72) Лвторы изобретения

Ю. П. Дарменко и С. Е. Токовенко (71) Заявитель Украинский республиканский центр метрологии и стандартизации (54) УСТРОЙСТВО ДЛЯ СЧЕТА ПО ПЕРЕМЕННОМУ МОДУЛЮ

Изобретение относится к области импульсной техники.

Известно устройство для счета по переменному модулю, состоящее из счетчика из двоичных ячеек, логических элементов «И» и

«ИЛИ» дополнительных двоичных элементов, программных переключателей, инверторов и блоков дешифрации (1).

Недостаток этого устройства — сложность.

Известно наиболее близкое по технической сути к предлагаемому устройство, содержащее последовательно соединенные счетные разряды с дешифратором состояний первого разряда и схемами объединения на входах остальных, триггер записи, управляющий вентилями сброса и вентилями счета — записи, блок переключателей (в случае многопрограммного устройства — дополненный коммутатором программ) для поразрядной установки числа М-модуля пересчета, схему формирования выходного сигнала, включаюшую в себя схему совпадения, схему объединения и триггер (2). Недостатком этого у стройства является неоднозначность модуля пересчета.

Цель изобретения — уменьшение неоднозначности модуля пересчета.

Достигается это за счет введения в устройство логического элемента «И†HE», дополнительного триггера, дополнительного вентиля и блока задержки, причем входы логпческого элемента «И вЂ” НЕ» соединены с выходами дешифратора и блока программных переключателей, а его выход соединен с соответствующим входом многовходового элемен5 та «И», входы дополнительного триггера соединены с выходом первого разряда счетчика и выходом устройства, выход дополнительного триггера соединен с одним пз входов дополнительного вентиля, второй вход которого

10 соединен с выходом старшего разряда счетчика, выход дополнительного вентиля соединен со входом вентиля, второй вход которого сосдинен с выходом многовходового элемента

«И», а блок задержки включен между Bblxo15 дом дешифратора и входами одного из вентилей и триггера записи.

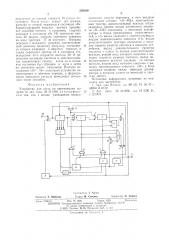

Электрическая структурная схема описываемого устройства приведена на чертеже.

Устройство содержит счетчик пз последо20 вательно соединенных разрядов 1 — 3, логические элементы 4, 5 «ИЛИ», включенные между старшнмп разрядами счетчика, дешифратор 6 состояний младшего разряда, входной вентиль 7 с блоком 8 управления, триггер 9

25 записи, вент .*ли 10 — 13, блок 14 программных переключателей, элемент 15 «II», блок формирования выходного сигнала, состоящий пзлогического элемента 16 «ИЛИ», триггера 17 и логический элемент 18 «И — HE», блок блоки30 ровни переноса, состоящий из дополнптсльно5) 39380 го трппсра 19 и до(.:ол:I,ITccl:лого i;с ;нтиг!» 20. блок 21 задержки.

Индекс»)1 22 обозна lclt вход, я индексом

23 †вых устройства.

1 ябо 1 ) cTpoilcTBB 32!< 110 иl(.Tc51 B !»)1, »1()

B пропсссс 3BIIItcJJ c12ришс разряды с с! )нкя

ПРЕДУСтаиаBЛ1JBBIOTCß !3 COCTO> (ИЯ,;loll»(II!5(toщи с до «9» число ксlждОГО i! 3 стсlр П1 !1х р 23 р 51дов модуля пересчета. В дальнеин,ем, в процсссс cчстя ltpoilcxoдит досчс i, IO l x Iló.!1013»l »

c0с 1 Ояи1iя. 1 (cрBы11 )кс )) сlз p5!, 1 ) стяпBв;1!I вя сTся в пулевое состояние и впослс,lcTB!ill после

ДОСЧЕТ2 !10 Н ) ЛЕВЬ(Х COCГОЯнпй 13 СТсl()lil!l. Р 13j)ЯД2Х, ЛИ ОO ПО СНГН2 1У НУЛСВЫХ 31!сl ICIJ! Iй III

СЕЛ В СТ".PШИ P23j)ЯД2Х Ыо, Ц ЛЯ ПСPСС 10ТЯ, когда пересчет старшими разрядами Ilc требуется, в нем происходит досчст !10 зяд;lllltot состояния, после чего форм!)рустся выходной сш.нал устройства. Для устранения погрешности пересчета старшими разрядами,,)аьч ой сдIIIIIIIIc, а с учетом нснредустанавливасмог» первого разряда — десяти, I!а вход 13торого разряда через вентиль 12 после прсдустаповки Годастся од:ш корректпрующш! и:,шульс досчетя.

Предустановка старших разрядов .1роисходит в процессе счета устройством первых дес»п) входных импульсов. Режим работы выбран так, что на входы старших разрядов в этот период через вентиль 13 поступает пачка выходных импульсов, а на входы сброся через блок 14 — сигналы с дсшифрятора, соответствующие состояниям первой декады, именуемые в дялы)сйшем константами. В IlpoULccc счета указанной пачки импульсов (процесс

Зс7ПИСИ) Ка КДаЯ ДЕК2Д2 СТЯР!НИХ Рс73РЯДОВ проход IT последовательно Всс cocTO»I!ия от

«О» до «9». Если в процессе записи прои320ст)! сброс сс одной из констант, например, константой «2», то очевидно, что по окончании записи декада окмкстся в состояии;! «7».

В качестве генератора пачки импульсов записи используется первый разряд счетчика в сочеташш с триггером 9 записи. В качестве сшпала досчета используется од:ш импульс константы «9», задержанный во 13ремсни.

Рассмотрим работу устройства, начи!Гяя с момента формирования очередного вых».I!!»i сигнала на выходе триггера 17, При этом, первый разряд устапош!тся в состояние «0», триггер 9 — в состояние «1», а трип.ср 19 в состояи!)е «О», при котором вен.п)ль 20 оказывается закрытым. Блок 8 управления закрывает вентиль 7 в случае однократного режима работы, обеспечивая начало работы с приходом внешнсг0 запускающего импульса. В случае цикличсской работы устройства, венTl1ëü 7 пе закрывается. Установка триггера 9 в состояние «1» обеспечивает открывянисвснтилсй 10 — 13.

Зходпыс сигналы устройства пос(уll(!107 на вход младшего разряда, а через вентиль 13— на входы всех старших разрядов. Чсрсз вентили 10 — 11 на входы сброса старших разрядов иоступгнот с выходя дени!(()ряторя согляся

1(1

I 0 )2

3:)

42 ,)О

55 ()0

Ii0 il0,lO):. . l(; lC ) :!, !iO !BTP,1(й О, IOКB -i, !1 )

»О IJC*!JJBJIC 3 ill!ICB Co(."Ò»ßИНII В С. 2.)! 1:!(РсlзРЯДЬ1, B 00»Т!3ЕТС B !J ll С 17)СО) С ОИ 1 Р(;I W"< тановкой. (5 конце цикла записи задсржя!.иый посредство I блока 21 импульс констант:il

<<9>> IPpC3 J3C t!TJ! II B 1 I!OCT!) 112C I 112 B):o;I н1«»р;)го разряда 13 качеств0 коррсктиру(о 0! 0

ll

3ХО,(но l O:I М I!) )! ЬСЯ !(!Л2Диliill .) 1 IP)IД (. !»Ьсl

11 сl;О (И ГСЯ 13 ! CЛС!30М COСTОЯИ! I II, cl B C (Р— ших —.13 результат(Iц! кла Записи — .! ;90!13?30;! с112:I )СJ 1 01 сl!И13i(2. Сl ГНЯ. 1 ИСРСИОСB, С001 301 ст13) о ци;"1 десятому импульсу, сос-Il!TB BBåòcÿ !

Ггорым разрядом, я также устанавливает 1p и Bcp . 9 в состОЯППС << 1 », к<)Top ь! й>;3 013010

0<1(рсдь, открывает ьснтиль 20. Когдс7 в );<),.сссс дальнейшего счета произойдет .(c,cite J в ст2Р ни(х I) 23() 5JIIBx IO 1!УлсЗОГО c(ic10ЯППЯ, и ()льс ПCi)c:Ioëtlcï!J)t счетч;Il(2 чсрсз вс.IT!J,!ь

20 и элсмсснг 16 31!10 пиястся тр!Гггером 17. ! (OCI<0Л1И(, 13 ЭТОТ 31(). !Сс(Т 3151(J J, J с1» 30Кс1;1с .

1 iахo+IJ !С51 Тяк;кС 13 l i, IС3031 сос 1 ОЯ111!! l, Т» 13 слу IBc, если 13 младп, см;)азряде модуля i. ñ()СС - CTcl ) C! BiIOB;ICII ll) Л,:Ь, ЧТО СОО! ВЕТСТВ) СТ

1 стсl!1Овке Г:еРсключатсл» этОГО ))23P51JB иа константу «О», этот снп!ал поступит на трш;ер 17 !1 произведет переброс его в исходнос состояние; при этом сформируется выход)!ой

cèã»à t устройства. В случае значащей цифры

13 младшем разряде модуля пересчета яна loГичный процесс псрсброса триггера 17 11 (pop)IIIp0BBIIII51 ВыхОДПО(0 СПГП2ла ПроизоидСТ после досчста первым разрядом соотвстст: ующсго количества импульсов.

В случае установки модуля пересчета (( (! 0 (!1ри Л 4=0) элемент 15, регистрирующ iil нулевые значения старших разрядов ч)1сла ), ь самом начале цикла записи вь:,iaет cttt.lt2.7, который благодаря наличию элем(ита 16 тяк:ке зяпомииаетс51 TpHI BCpol(I 17.

Г(сйст!3!и!0!i>t!о. B исходном состоянии .,cкадя младшего разряда установлена в состо)ишс

«0», снпгал:!улевой константы иостуг:ает li;! одш. из входов элемента 15, с выхода э te31011тя 18 также поступает единичный t:oòCølti(!II, тяк как Iiсрсключятсль первого разряда 13 блоке 14 установлен на значагцую цифру. а па остальные входы элемента 15 поступают спг:!алы нулевой конст;шты в соотзетствии с устBIIOBJ(011 нулей 1)а переключателях старших разрядоз блока 14. Поэтому после отсчета младшим разрядом Л входных импульсоВ соответствующая константа с дешифраторг через блок 14 поступит Iià тр:!п ер 17, ус-.;1!)овит Cto» ttcxoptloe состояние it c())opiittруст выходной сигнал устройства. (. с(ай 1 CTBII0131(ll )10Д ч, 15! ИСРЕСЧСТс .

=-10" (н — количество псрссчетных р23р5;доз), отл!Гчястся от описанного выше ()) ( ()0! тем, что переключатель младшего разряда в блоке 14 также установлен на конcT2ïòó «0». При этом на оба входа элемента

18 посту;)яют сигналь: нулевой константы i! в

539380

Составитель Т. Артюх

Техред М. Семенов

Редактор Э. Шибаева

Корректор О. Тюрина

Заказ 2768/19 Изд. ¹ 1836 Тираж 1029 Подиисиюс

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и от: рытий

113035, Москва, Ж-35, Раушская иаб., д. 4,5

Типография, пр. Сапунова, 2 результате II;I выходе элемента 15 сигнал отсутствует. После цикла записи все декады, начиная со второй, окажутся в состоянии «9».

Корректирующии импульс досчета произведет сквозной перенос и установку старших разрядов в состояние «О». Но поскольку вентиль 20 закрыт, импульс сквозного переноса на вход триггера 17 не поступит. Импульс переноса с младшего разряда, соответствующий десятому входному импульсу, сосчитается вторым разрядом в обычном порядке, а также опрокинет триггер 19 в состояние «1», вследствие чего откроется вентиль 20. В результате состояние счетчика в действительности соответствует такому, когда он в исходном состоянии был сброшен в нули и затем им сосчитано десять импульсов. Поэтому оставшиеся «10" — 10» импульсов устройство пересчитывает в обычном порядке, а формирование выходного сип1ала происходит описанным выше способом.

Формула изобретения

Устройство для счета по переменному модулю по авт. свид. № 31140б, отл и ч а ю ще— еся тем, что, с целью уменьшения неоднозиа шости модуля пересчета, в него введены логическш1 элемент «И — НЕ», дополнительный триггер, дополнительный вентиль и блок задержки, причем входы логического элемен5 та «И вЂ” НЕ» соединены с выходами децшфратора п блока программных переключателей, a его выход соединен с соответствующим входом многовходового элемента «И», входы дополнительного триггера соединены с вы.;о10 дом первого разряда счетчика и выходом устройства, выход дополнительного триггера соедIIIIcii с одним из входов дополнительного вентиля. второй вход которого соединен с выходом старшего разряда счетчика, выход до15 полнительного BciITIIëÿ соединен со входом вентиля, второй вход которого соединен с выходом многовходового элемента «И», а блок задержки включен между выходом дешпфратора и входами одного из вентилей п триг20 гера записи.

Источники информации, принятые во внимание при экспертизе:

1. Лкц. 3-ва Японии, кл. 98 (5) Fl № 47—

48860, 8.12.72.

25 2. Авт. свид. № 311406, кл. Н ОЗК 21, 1. 12. 1971.