Последовательный обнаружитель

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Со!оз Советских

Социалистических

Республкк ф «М (61) Дополнительное к авт. свид-ву (22) Заявлено 01.11.74 (21) 2072888/09 с присоединением заявки № (23) Приоритет

Опубликовано 25.12.76. Бюллетень № 47

Дата опубликования описания 08.02.77 (51) М. Кл. G 01$7/28

Н ОЗК 5/153

Государственный комитет

Совета Министров СССР (53) УДК 621.396 962 3 (088.8) по делам изобретений и открытий (72) Авторы изобретения

А. И. Цирлин и Ю. П. Озерский

Московский ордена Трудового Красного Знамен и (Г.; физико-технический институт (71) Заявитель (54) ПОСЛЕДОВАТЕЛЬНЫИ ОБНАРУЖИТЕЛЬ

Изобретение относится к радиотехнике и может использоваться в устройствах, где необходимо выделение повторяющегося импульсного сигнала из шума.

Одним из известных устройств является последовательный обнаружитель, применяемый при поиске и контроле сигнала, содержащий два цифровых счетчика и логические схемы (1).

Известен также обнаружитель бинарноквантованного сигнала, содержащий делитель частоты и реверсивный счетчик, первый выход которого соединен с блоком сравнения с верхним порогом, а второй выход соединен с блоком сравнения с нижним порогом (2), Однако известные последовательные обнаружители обладают низкой помехоустойчивостью, обусловленной резкой зависимостью вероятности правильного выделения сигнальной последовательности импульсов из смеси ее с шумовыми последовательностями от интенсивности сигнала и шума, что приводит к невозможности обеспечения высокой надежности различения сигнала и шума в широком диапазоне изменения их интенсивностей.

Целью изобретения является повышение помехоустойчивости последовательного обнаружителя.

Для этого в последовательный обнаружитель бинарно-квантованного сигнала, содержащий делитель частоты и реверсивный счетчик, первый выход которого соединен с блоком сравнения с верхним порогом, а второй выход соединен с блоком сравнения с нижним порогом, дополнительно введены второй блок сравнения с нижним порогом, вентиль, два элемента И, три элемента ИЛИ и триггер, при этом вентиль включен между выходом блока сравнения с верхним порогом и первым вхо1О дом реверсивного счетчика, первый элемент

ИЛИ включен между выходом делителя частоты и вторым входом реверсивного счетчика, третий выход которого соединен с последовательно включенными вторым блоком сравне15 ния с нижним порогом, первым элементом И, вторым и третьим элементами ИЛИ и триггером, второй вход триггера соединен с выходом блока сравнения с верхним порогом, а между блоком сравнения с нижним порогом и вторым выходом второго элемента ИЛИ включен второй элемент И, причем третий вход реверсивного счетчика соединен с вторым входом третьего элемента ИЛИ, а выходы триггера соединены с вторыми входами элементов И.

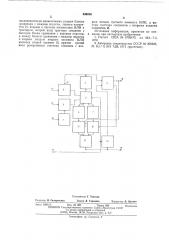

2б На чертеже приведена структурная электрическая схема предложенного обнаружителя.

Последовательный обнаружитель бинарноквантованного сигнала содержит делитель частоты 1 и реверсивный счетчик 2, первый вы30 ход которого соединен с блоком сравнения 3

540230 с верхним порогом, а второй выход соединен с блоком сравнения 4 с нижним порогом (при поиске), между выходом блока сравнения 3 и первым входом, являющимся входом сложения реверсивного счетчика 2, включен вентиль

5, между выходом делителя частоты 1 и вторым входом, являющимся входом вычитания реверсивного счетчика 2, включен первый элемент ИЛИ 6, третий выход реверсивного счетчика 2 соединен с последовательно включенными вторым блоком сравнения 7 с нижним порогом (при контроле), первым элементом И

8, вторым и третьим элементами ИЛИ 9, 10 и триггером 11, второй вход которого соединен с выходом блока сравнения 3, а между блоком сравнения 4 и вторым входом второго элемента ИЛИ 9 включен второй элемент И 12, причем третий вход реверсивного счетчика 2 соединен с вторым входом третьего элемента

ИЛИ 10, а выходы триггера 11 соединены с вторыми входами элементов И, 8, 12. Третий вход реверсивного счетчика 2 является входом его установки в начальное состояние, вход 13 вентиля 5 является входом запрета его, вход

14 — входом анализируемой последовательности импульсов, вход 15 — входом контрольной шумовой последовательности импульсов, вход

16 входом вспомогательной последовательности импульсов, вход 17 — входом запуска, выход 18 — выходом индикации состояния

«поиск» и «контроль», выход 19 — выходом последовательного обнаружителя.

Последовательный обнаружитель работает следующим образом.

Подачей импульса пуска на вход 17 обнаружитель ставится в состояние обнаружения при поиске сигнала. Импульс пуска устанавливает реверсивный счетчик 2 в начальное состояние S (0(S(N — 1), где N — емкость реверсивного счетчика 2, а также, пройдя через элемент ИЛИ 10, устанавливает триггер 11 в состояние «поиск». При этом выходным напряжением блока сравнения 3 вентиль 5 устанавливается в открытое состояние, с выходов триггера 11 на элемент И 12 подается разрешающее напряжение, а на элемент И 8 — запрещающее. На вход сложения реверсивного счетчика 2 через вентиль 5 поступают бинарноквантованные по амплитуде импульсы анализируемой (сигнальной или шумовой) последовательности, а на,вход вычитания через элемент ИЛИ 6 поступает сумма бинарно-квантованных по амплитуде импульсов контрольной шумовой последовательности, подаваемой на вход 15 и поделенной в п раз по частоте в делителе частоты 1 вспомогательной последовательности бинарно-квантованных .по амплитуде импульсов, подаваемых на вход 16, чмеющих частоту повторения обнаруживаемого сигнала и не совпадающих во времени с импульсами анализируемой и контрольной последовательностей. Состояние обнаружения при поиске длится до тех пор пока реверсивный счетчик 2 не достигнет либо своего верхнего состояния N — 1, либо состояния Mn)0.

5 о

Если реверсивный счетчик 1 попадает в состояние Мп, то на выходе блока сравнения 4 с нижним порогом при поиске (абсолютная величина этого по рога равна S — Mn) появляется напряжение, которое через элементы И

12 и ИЛИ 9 поступает на выход 19 обнаружителя, что означает принятие обнаружителем решения об отсутствии сигнала в анализируемой последовательности. Если реверсивный счетчик 2 достигает своего верхнего состояния

N — 1, то на выходе блока сравнения 3 с верхним порогом (абсолютная величина верхнего порога равна N — 1 — S) появляется напряжение, которое, попав на вход триггера 1, .переводит его в состояние «контроль». Изменение напряжения на выходе 18 триггера 11 свидетельствует о принятии обнаружителем решения о наличии сигнала в анализируемой последовательности и о переходе обнаружителя из состояния обнаружения при поиске сигнала в состояние контроля за наличием сигнала в анализируемой последовательности. При контроле с выходов триггера 11 на элемент И 12 подается запрещающее напряжение, а на элемент И 8 — разрешающее напряжение, в результате чего выход 19 обнаружителя отключается от блока сравнения 4 и подключается к блоку сравнения 7 с нижним порогом при контроле. В состоянии N — 1 реверсивного счетчика 2 напряжение с выхода блока сравнения 3 закрывает вентиль 5, чем отключает вход сложения реверсивного счетчика 2 от входа 14 обнаружителя и предохраняет его от переполнения. При контроле реверсивный счетчик 2 может принимать любые состояния от N — 1 до М„+1)0. Если состояние реверсивного счетчика 2 падает до величины М„)

)0, то на выходе блока сравнения 7 появляется напряжение, которое через элемент И 8 и элемент ИЛИ 9 поступает на выход 19 обнаружителя и через элемент ИЛИ 10 на вход триггера 11, который при этом переходит из состояния «контроль» в состояние «поиск», что свидетельствует о принятии обнаружителем решения о .потере сигнала в режиме «контроль» и о,необходимости вести его поиск в другой импульсной последовательности.

Формула изобретения

Последовательный обнаружитель бинарноквантованного сигнала, содержащий делитель частоты и реверсивный счетчик, первый выход которого соединен с блоком сравнения с верхним порогом, а второй выход соединен с блоком сравнения с нижним порогом, о т л и ч а ющи и ся тем, что, с целью повышения помехоустойчивости, в него дополнительно введены второй блок сравнения с нижним порогом, вентиль, два элемента И, три элемента ИЛИ и триггер, при этом вентиль включен между выходом блока сравнения с верхним порогом и первым входом реверсивного счетчика, первый элемент ИЛИ включен между выходом делителя частоты и вторым входом реверсивного счетчика, третий выход которого соединен с

540230

Составитель Г. Теплова

Техред Л. Гладкова

Редактор Н. Скляревская

Корректор Л. Орлова

Заказ 3096/15 Изд. № 392 Тираж 690 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пп. Сапунова, 2 последовательно включенными вторым блоком сравнения с нижним порогом, первым элементом И, вторым и третьим элементами ИЛИ и триггером, второй вход триггера соединен с выходом блока сравнения с верхним порогом, а между блоком сравнения с .нижним порогом и вторым входом второго элемента ИЛИ включен второй элемент И, причем третий вход реверсивного счетчика соединен с вторым входом третьего элемента ИЛИ, а выходы триггера соединены с вторыми входами элементов И.

Источники информации, принятые во вни5 мание при экспертизе изобретения:

1. Патент США № 3702475, кл. 343 — 7.3, 1972.

2. Авторское свидетельство СССР № 309326, М. Кл. G 01S 7/28, 1971 (прототип).