Частотно-фазовый дискриминатор

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (11) 540347

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-вуК 379049 (22} Зз я иле но 18.12,75 (21) 2300648/21 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано 25 12 76 Бюллетень №47 (45} Дата опубликования описания27.07.77 (51) М. Кл.

Н 03 0 13/00

Гасударственный комитет

Совета Министрав СССР

IlD делам изабретений и еткре1тий (53) УДК

621374.33 (088.8) Е. И. Усышкин и В, М. Бедеров (72) Авторы изобретения

Всесоюзный научно-исследовательский кинофотоинститут (71) Заявитель (54} ЧЛСТОТНΠ— ФАЗОВЫЙ ДИСКРИМИНАТОР

Изобретение относится к импульсной технике.

Известен частотно-фазовый дискриминатор, содержащий два триггера, на входы которых подаются входные импульсы, логические элементы

НŠ— И, логические элементы ИЛИ, И, счетчик импульсов, третий триггер и дополнительные логические элементы, осуществляющие контроль знака 11).

Недостатком этого дискриминатора является

его сложность.

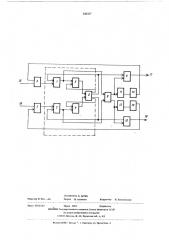

Дискриминатор содержит триггеры 1,2, формирующие триггеры 3,4 логический элемент 5, логические элементы ИЛИ 6,7, RS- трштер 8, логические элементы И 9,10, разностные элементы 11,12, зч элементы задержки 13,14.

Наиболее близким по технической сущности к предлагаемому является дискриминатор, описанный в основном авт. св. Р 379049 и содержащий триггеры, на входы которых поданы сравниваемые сигналы, а выходы которых соединены с входами формирующих триггеров, выходы которых соединены с входами логического элемента, выходы которого соединены соответственно с входами триггеров (2}.

Недостатком этого дискриминатора является отсутствие изменения знака выходного напряжения при изменении знака взаимной фазы входных сигналов, Цель изобретения — обеспечение изменения знака выходного напряжения при изменении знака взаимной фазы входных сигналов. ,Для этого в предлагаемое устройство введены

RSl — триггер, входы которого подключены к выходам триггеров дискриминаторов, два логических элемента И, один вход каждого из которых соединен с выходом логического элемента дискриминатора, а другой с выходом RS — триггера, разност1ð ные элементы, элементы задержки и два логических элемента ИЛИ, одни из входов которых соединены с источниками сравниваемых сигналов, вторые входы через последовательно соединенные элемент задержки и разностный элемент — с выходами

15 я$ — триггера, а выходы KoIopbIx подключены к входам соответствующих триггеров дискриминатдра.

На чертеже приведена структурная электричес. кая схема дискриминатора.

540347

На входы 15,16 поданы сравниваемые сигналы, выходные сигналы снимаются с выходов !7,18.

Принцип работы дискриминатора заключается в следующем.

В предлагаемом дискриминаторе обеспечена воэможность второго фазового режима для случая, когда ведущая частота f, меньше ведомой f,, a такжв обеспечен взаимный переход между первым и вторым фазовыми режимами при изменении знака фазового рассогласования сравниваемых частот.

Ф

Это объясняется тем, что при тенденции к переходу (при f, < f,) из фазового первого во второй частотный режим перебрасывается триггер 8, благодаря чему на входе собственно дискриминатора формируется допблнительный импульс, возвращающий его в фазовый режим. Это режим является уже вторым фаэовым режимом всей системы, поскольку он осуществляется уже при втором состоянии триггера 8, что индуцируется элементами 9 и 10 на выходе устройства..

Сравниваемые сигналы с частотой f, и f поступают соответственно через элементы 6 и 7 на входы триггеров 1 и 2. Принимают, что в начальный момент рассмотрения 1, > 1,. Тогда дискриминатор работает в первом частотном режиме. В этом режиме триггер 2 вырабатывает сигналы, следующие с частотой f и имеющие весьма малую длительность, вследствие чего они на триггер8 не оказывают воздействия (при необходимости для этого применяются блокирующие резисторно-конденсаторные цепочки). В то же время триггер 1 переключается с частотой f,, но не вырабатывает сигналы линейно изменяющиеся по длительности с частотой

f, — f Эти сигналы устанавливают и фиксируют триггер 8 в первое положение, при котором сигналы с выхода элемента 5 появляются на выходе элемента 9. При этом сигнал на выходе 18 устройства отсутствует. С увеличением частоты f z частоты fq и f q. сравниваются, а затем при f» < f, взаимная фаза и разность частот меняет знак, что обусловливает перевод дискриминатора в однофаэный режим При изменении взаимной фазы дискриминатор имеет тенденцию к переходу во второй частотный режим, в котором триггеры 1 и 2 как бы меняются местами. Однако первый же импульс, поступающий на триггер 8 от триггера 2, перебрасывает его во второе состояние,. При этом раэностный элемент 11 вырабатывает дополнительный сигнал, поступающий на вход триггера и возвращающий дискриминатор в фазовый режим, Этот режим является вторым фазовь.м режимсм и отличается от первого фазового режима тем, что триггер 8 установлен во второе положение, при котором выходные сигналы собственно дискриминатора поступают с выхода элемента 10, а не элемента 9, как в первых режи-!

О мах.

При сохранении условия f» < f> дискриминатор переходит во второй частотный режим, поскольку триггер 8 предшествующим процессом уже установлен во втором положении и лишь дополни-! я тельно в нем фиксируется.

При изменении условия f, < f, íà f, > f процессы происходят в обратном порядке, Таким образом, при изменении ведущей частоты f, данный дискриминатор обрабатывает "отри20 цательную" величину рассогласования частот и фаз сравниваемых сигналов.

Формула изобретения

Частотно-фазовый дискриминатор по авт. св.

Р 379049, отличающийся тем, что, с целью обеспечения изменения знака выходного напряжения при изменении знака взаимной фазы входных сигналов, в него введены RS-триггер, входы которого подключены к выходам триггеров дискриминатора, два логических элемента И, один вход каждого из которых соединен с выходом логического элемента дискриминатора, а другой — с выходом IRS òðèããåðà, разностные элементы, элементы

Q задержки и два логических элемента ИЛИ, одни иэ входов которых соединены с источниками сравниваемых сигналов, вторые входы через последовательно соединенные элемент задержки и раэностный элемент — с выходами RS — триггера, а выходы

40 .которых подключены к входам соответствующих триггеров дискриминатора.

Источники информации, принятые во внимание при эксперти"е:

О

1. Патент ГДР N 80465, кл. 21а 36/18 от

45 12.03.71 г.

2. Авторское свидетельство СССР N 379049, М.кл. Н 03 0 13/00, 21,03.71. (прототип) .

540347

Составитель А. Артазх

Техред И. Асталош

Редактор В. Кис .,;ва

Корректор Н. Золотовская

Заказ 6342/123

Филиал ППП" Патент ", г. Ужгород, ул. Проектная, 4

Тираж 1024 Подписное о

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открьпий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5