Регистр сдвига

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ (ц 540372

Союз СоветскихСациаливтических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 31.01.74 (21) 1991887/21 с присоединением заявки № (23) Приоритет

Опубликовано 25.12,76. Бюллетень № 47

Дата опубликования описания 28.03.77 (51) М. Кл 2 Н ОЗК 13/258

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (53) УДК 621.327(088.8) (72) Авторы изобретения

В. Ю. Березин, Б. А. Котов и В. И. Склизков (71) Заявитель (54) РЕГИСТР СДВИГА

Изобретение относится к импульсной и вычислительной технике и может быть применено в различных устройствах цифровых вычислительных машин для накопления, обработки и преобразования информации.

Известен регистр сдвига, содержащий квазистатические триггеры на МДП-транзисторах одного типа проводимости с нагрузочными

МДП-транзисторами, затворы которых объединены, и генератор тактовых импульсов, тактовые выходы которого соединены с соответствующими тактовыми входами всех квазистатических триггеров, Цель изобретения — уменьшение потребляемой и рассеиваемой мощности — достигается тем, что в регистр сдвига введены генератор импульсов и логический элемент

ИЛИ, причем выход логического элемента

ИЛИ соединен с затворами всех нагрузочных

МДП-транзисторов всех квазистатических триггеров, один из входов логического элемента ИЛИ соединен с выходом генератора импульсов, а другой вход логического элемента

ИЛИ вЂ” с выходом генератора тактовых импульсов.

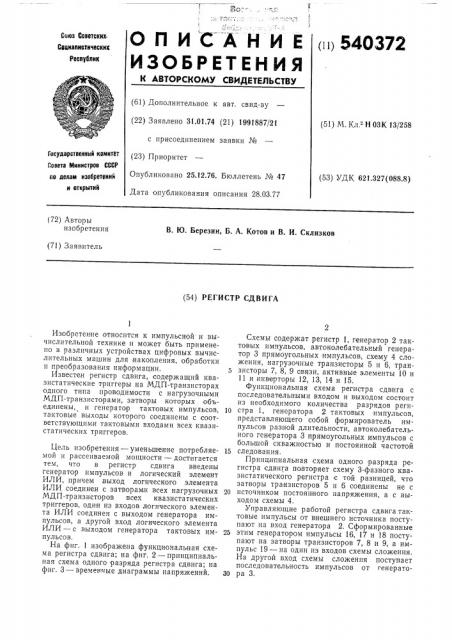

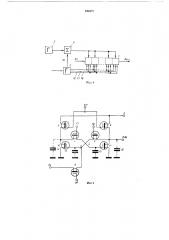

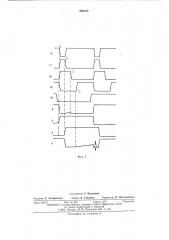

На фиг. 1 изображена функциональная схема регистра сдвига; на фиг. 2 — принципиальная схема одного разряда регистра сдвига; на фиг. 3 — временные диаграммы напряжений.

Схемы содержат регистр 1, генератор 2 тактовых импульсов, автоколебательный генератор 3 прямоугольных импульсов, схему 4 сложения, нагрузочные транзисторы 5 и 6, транзисторы 7, 8, 9 связи, активные элементы 10 и

11 и.инверторы 12, 13, 14 и 15.

Функциональная схема регистра сдвига с последовательными входом и выходом состоит из необходимого количества разрядов реги1о стра 1, генератора 2 тактовых импульсов, представляющего собой формирователь импульсов разной длительности, автоколебательного генератора 3 прямоугольных импульсов с большой скважностью и постоянной частотой

15 следования.

Принципиальная схема одното разряда регистра сдвига повторяет схему 3-фазного квазистатического регистра с той разницей, что затворы транзисторов 5 и 6 соединены не с

20 источником постоянного напряжения, а с выходом схемы 4.

Управляющие работой регистра сдвигатактовые импульсы от внешнего источника поступают на вход генератора 2. Сформированные

25 этим генератором импульсы 16, 17 и 18 поступают на затворы транзисторов 7, 8 и 9, а импульс 19 — на один из входов схемы сложения.

На другой вход схемы сложения поступает последовательность импульсов от генерато30 ра 3.

540372

В основу действия регистра сдвига положена способность триггерной ячейки сохранить информацию в течение некоторого времени при выключенном источнике питания и не разрушать ее при его включении, При этом одновременно используются свойства как триггерной, так и динамической памяти.

В схеме регистра триггерная ячейка образу«тся двумя инверторами, выполненными на элементах 10 и 11. Входы и выходы инверторов соединены между собой через транзисторы

7 и 8. В начальный момент 4 времени средние фронты импульсов всех последовательностей, формируемых генератором 2, совпадают между собой. Затем импульсы последовательности

16 открывают транзистор 9, через который информация начинает поступать на вход первого инвертора. Одновременно с этим импульсы последовательностей 17 и 18 выключают транзисторы 7, 8 между инверторами и на время перезаписи информации статический триггер распадается на две самостоятельные динамические ячейки памяти, образованные паразитными емкостями входа инверторов 12, 13. На вход первой ячейки поступает информация с выхода предыдущего:разряда, а вторая ячейка, сохраняя прежнее состояние, является источником информации для следующего разряда, По окончанию действия импульсов 16 и 17 в момент времени t> (фиг. 3) связь между соседними разрядами прекращается и происходит передача принятой информации внутри каждого разряда через снова включенный транзистор 7. После завершения этого процесса в момент времени 1 выход второго инвертора соединяется через транзистор 8 со входом первого, образуя статический триггер. По окончании переходного процесса в триггере в момент времени 4 импульсы 19 закрывают нагрузочные транзисторы 5, 6 и питание схемы от источника постоянного напряжения прекращается.

В качестве элементов памяти на время хранения записанной информации используются суммарные емкости выхода одного инвертора (14, 15) и входа другого (12, 13). Однако изза существованиия остаточного тока закрытото накала МДП-транзисторов и токов утечки полупроводникового материала интегралыных схем, записанная информация не может сохраняться бесконечно долго. Поэтому необходимо, чтобы источник питания подключался к схеме с частотой не ниже минимально допустимой (f ), т. е. время хранения информации

5 ограничено. Выполнение этого условия позволяет восстана вливать записанную информацию при отпирании нагрузочных транзисторов

5 и 6 импульсами питания. Для обеспечения возможности работы регистра сдвига в стати10 ческом режиме, т, е. хранение информации неограничено долгое время, в схему введен автоколебательный генератор импульсов с фиксированной частотой следования. Полученное на выходе схемы сложения импульсное на15 пряжение обеспечивает следующий режим питания устройства: при частоте тактовых импульсов выше частоты f> потребляемая разрядами регистра мощность возрастает пропорционально частоте, а ниже f — не зависит от

20 частоты тактовых импульсов.

При характерных для современной полупроводниковой технологии токах утечки (10 "—

10 ") А/БИТ выигрыш по потребляемой и рассеиваемой мощности по сравнению с ана25 логичными квазистатическими регистрами при работе с тактовыми импульсами частотой ниже fl составляет 10 — 10 раз при уменьшении помехоустойчивости схемы не более чем на

10О/

Формула изобретения

Регистр сдвига, содержащий квазистатические триггеры на МДП-транзисторах одного

35 типа проводимости с нагрузочными МДПтранзисторами, затворы которых объединены, и генератор тактовых импульсов, тактовые выходы которого соединены с соответствующими тактовыми входами всех квазистатических

40 триггеров, отл и чаю щийся тем, что, с целью уменьшения потребляемой и рассеиваемой мощности, в него введены генератор импульсов и логический элемент ИЛИ, причем выход логическото элемента ИЛИ соединен с

45 затворами всех нагрузочных МДП-транзисторов всех квазистатических тритгеров, один из входов логического элемента ИЛИ соединен с выходом генератора импульсов, а другой вход логического элемента ИЛИ вЂ” с выходом

50 генератора тактовых импульсов, 540372

Фиг. 8

Составитель Т. Богдалова

Техред Л. Гладкова Корректор И. Позняковская

Редактор Е, Скляревская

Типография, пр. Сапунова, 2

Заказ 925/11 Изд. ¹ 364 Тираж 1077 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5