Устройство для вычисления логарифмической функции

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ 0054ПЬУ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (б1) Дополнительное к авт. свид-ву (22) Заявлено 10.08.73 (21) 1952953/24 с пписоединением заявки №вЂ” (23) Приоритет

Опубликовано 30.12.76. Бюллетень № 48

Дата опубликования описания 17.01.77 (51) М. Кл. С 06F 7/38

Государственный комитет

Совета Министров СССР по делам изобретений и OTKpbITHN (53) УДК 681.325.5(088.8) (72) Авторы изобретения

А. Л. Рейхенберг и P. Я. Шевченко 71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ

ЛОГАРИФМИЧЕСКОЙ ФУНКЦИИ

Изобретение относится к цифровой вычислительной технике и может применяться при аппаратном вычислении элементарных функций, в частности в специализированных двоичных цифровых вычислительных машинах с фиксированной запятой.

Известно устройство для вычисления логарифмической функции, а именно гиперболических синуса и косинуса, содержащее блок управления, выходы которого соединены с управляющими входами накопительных и сдвигающего регистров и входом блока памяти, выходы накопительных регистров соединены с входами одноразрядных сумматоров-вычитателей, выходы которых соединены с входами накопительных регистров, второй выход второго накопительного регистра соединен с входом блока определения цифры псевдочастного, выход которого соединен с управляющими входами второго и третьего одноразрядных сумматоров-вычитателей, третий выход второто накопительного регистра соединен через блок определения сходимости и блок сброса с входом блока управления, другие вход и выход которого подсоединены к блоку повторения итераций, второй выход третьего накопительного регистра соединен с входом сдвигающего регистра.

Цель изобретения — расширение класса решаемых задач путем вычисления логарифмической функции.

Для этого в предлагаемое устройство вве. дены два вентиля, одни входы которых соединены с выходами блока памяти, к вторым входам подсоединен выход блока определения цифры псевдочастного, выходы вентилей соединены с вторым входом первого одноразрядного сумматора-вычитателя, а выход сдвигающего регистра соединен с вторыми входами второго и третьего одноразрядных сумма10 торов-вычитателей.

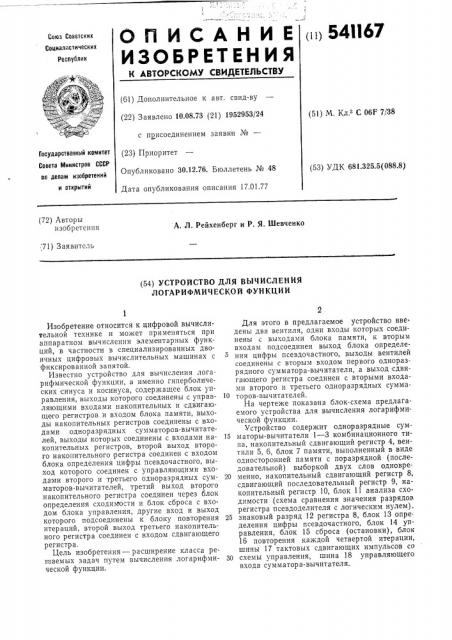

На чертеже показана блок-схема предлагаемого устройства для вычисления логарифмической функции.

Устройство содержит одноразрядные сум15 маторы-вычитатели 1 — 3 комбинационного типа, накопительный сдвигающий регистр 4, вентили 5, б, блок 7 памяти, выполненный в виде односторонней памяти с поразрядной (последовательной) выборкой двух слов одновре20 менно, накопительный сдвигающий регистр 8, сдвигающий последовательный регистр 9, накопительный регистр 10, блок 11 анализа сходимости (схема сравнения значения разрядов регистра псевдоделителя с логическим нулем).

25 знаковый разряд 12 регистра 8, блок 13 определения цифры псевдочастного, блок 14 управления, блок 15 сброса (остановки), блок

16 повторения каждой четвертой итерации, шины 17 тактовых сдвигающих импульсов со

30 схемы управления, шина 18 управляющего входа сумматора-вычитателя, 541167

r„— 0

j 0,1,....,и

Параллельно-последовательная структура устройства, которая обеспечивает оптимальное соотношение между быстродействием и объемом используемой аппаратуры, состоит из трех рециркуляционных ячеек. В каждую рециркуляционную ячейку входят накопительный регистр и одноразрядный сумматор, входы и выходы которых соединены между собой в кольцо. На второй вход сумматора-вычитателя 1 через вентили 5 и 6 подаются по- 10 следовательно, начиная с младшего, значения разрядов константы I и (1+2 ") или In (I — 2 — ") из блока памяти 7. Вентиль 5 открывается при значении цифры псевдочастного q;=+I, вентиль 6 — при цифре q;= — 1. Значение кон- 15 станты I и (1 — 2- ) в блоке памяти записано в дополнительном коде, что исключает режим вычитания в сумматоре-вычитателе 1. Выходы всех разрядов, расположенных после двоичной запятой, накопительного регистра 8 по- 20 даются на блок 11 анализа сходимости, выход которого соединен с входом блока 15 сброса, соединенного с блоком управления 14.

Знаковый разряд 12 регистра 8 соединен с входом блока 13 определения цифры псевдо- 25 частного q, в качестве которого может использоваться триггер и выход которого соединен с входом управления сумматоров-вычитателей 2 и 3. На управляемые входы 18 этих сумматоров-вычитателей подается сигнал с 30 выхода сдвигающето последовательного регистра 9. На выходы сдвига всех регистров и вход чтения блока памяти 7 с шин 17 блока управления 14 поступают тактовые сдвигающие импульсы. 35

В начальном состоянии в регистре 4 находится нулевое значение; в регистре 8 — значение аргумента Х, уменьшенное на единицу; в регистре 10 — единица.

Вычисление логарифмической функции для 40 интервала изменения аргумента

1 < Х = П (1 + q)2 — + > (2

i=o

45 в предлагаемом устройстве основано на параллельном решении в итерационном процессе следующих разностных рекуррентных соотношений:

r, = Х вЂ” 1; ri+I = rJ — д Х,2 — < + >

+1 при r> )О д = signr,= — 1 при r (О

Хо = 1; Ху.> = Х + (. Х)2 "> Хп + Х

Уо =0; Yg, I =- Y>+In(1+q,2) — + > Уи -IпХ

Каждое приведенное соотношение вычисля- 60 ется последовательно за (и+т) тактов (где и — число разрядов аргумента; и — число дополнительных разрядов для компенсации погрешности округления (усечения) при сдвиге). Г>5

Так как при 1(X(2 для цифр псевдочастного q +1, — 1 условие сходимости (исправляемости итераций) итерационного процесса и

r,. (,", Х 2 — >

lг= не выполняется для ряда значений аргумента

Х (например 1, 1+1, 2; 1, 43 — 1, 49, 1, 85), то для устранения зон несходимости необходимо и достаточно повторить по два раза только каждую четвертую итерацию. В этом случае обеспечивается выполнение условия сходимости итерационного процесса, так как

4Еп1 (— j

l X> 2 +" +;, Xi I2 —

A J i =4р где р = 1, 2, 3..., Ent — 1 — номер повто4 ряемой итерации.

В повторяемых по два раза итерациях с порядковыми номерами j=4, 8, 12, 16,... число сдвигов и константа In(l+q,2 — ) не меняются, но значение цифры псевдочастного ф может быть различным.

В любой итерации с блока управления 14 выдается серия сдвигающих тактовых импульсов. По знаку содержимого регистра 8 в блоке 13 вырабатывается очередное значен ие q, дл я следующей итер а ции.

Содержание накопительных регистров рециркуляционных ячеек суммируется или суммируется — вычитается (для сумматоров-вычитателей 2 и 3) с константами In(1+q;2 — ) или со сдвинутым . значением содержания регистра 9. Полученный результат каждой итерации последовательно заносится в освобождающиеся при сдвиге старшие разряды накопительных регистров рециркуляционных ячеек. и

После выполнения и+ Ent — ) + 1 итера4 ций в регистре 4 находится значение логарифмической функции, в регистре 8 — нулевое значение, а в регистре 10 — приближенное значение аргумента.

Однако для большинства значений аргумента итерационный процесс вычисления сходится на итерации, номер которой меньше величины и+ Ent — "1+ 1. При этом в регистре

4.

4 находится точное значение логарифмической функции. В регистре 8 содержание равно нулю, и блок 11 выдает сигнал сброса в блок 15 для остановки процесса вычисления на следующей итерации. Этим обеспечивается асинхронный режим процесса вычисления, и производительность значительно повышается.

Блок 16 повторения по два раза каждой четвертой итерации не изменяет число сдвигов и константу в следующей итерации. Блок повторения итераций состоит из счетчика, дешифратора и логических элементов.

541167

Формула изобретения 1=

J.

/ 7

Составитель Й. Горелова

Техред А. Камышникова

Корректор Е. Хмелева

Редактор С. Заика

Заказ 131/14 Изд. № 1896 Тираж 495 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Для практически требуемой;очности вычислений максимальное время пр це а вычисления в тактах Т(л +7п+12.

Параллельно-последовательная структура предлагаемого устройства состоит из стандартных простых цифровых элементов и обладает однородностью и регулярностью, что соответствует требованиям и возможностям современной интегральной технологии.

Работа устройства проверена путем моделирования на ЦВМ «Минск-22».

Устройство для вычисления логарифмической функции, содержащее блок управления, выходы которого соединены с управляющими входами накопительных и сдвигающего регистров и входом блока памяти, выходы накопительных регистров соединены с входами одноразрядHblx сумматоров-вычитателей, выходы которых соединены с входами накопительных регистров, второй выход второго накопи6 тсльпого регистра соединен с входом блока опредезе :ия,ц: фры псевдочастного, выход которого соединен с управляющими входами второго и третьего одноразрядных сумматоров5 вычитателей, третий выход второго накопительного регистра соединен через блок определения сходимости и блок сброса с входом блока управления, другие вход и выход которого подсоединены к блоку повторения итера10 ций, второй выход третьего накопительного регистра соединен с входом сдвигающего регистра, отличающееся тем, что, с целью расширения функциональных возможностей путем вычисления логарифмической функции, 15 в него введены два вентиля, одни входы которых соединены с выходами блока памяти, к вторым входам подсоединен выход блока определения цифры псевдочастного, выходы вентилей соединены с вторым входом первого

20 одноразрядного сумматора-вычитателя, а выход сдвигающего регистра с вторыми входами второго и третьего одноразрядных сумматоров-вычитателей.