Устройство для умножения

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (ii) 54II70

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Ресоубвик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ф ак (61) Дополнительное к авт. свид-ву (22) Заявлено 09.10.73 (21) 1963215/24 с присоединением заявки №вЂ” (51) М. Кл. - б 06F 7/39

Совета Министров СССР ло делаю изобретений и открытий

Опубликовано 30.12.76. Бюллетень № 48

Дата опубликования описания 19.01.77 (53) УДК 681.3(088.8) (72) Автор изобретения

В. И. Агибалов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

Государственный комитет (23) Приоритет

Предлагаемое устройство относится к области вычислительной техники и может быть использовано при построении специализированных вычислительных устройств последовательного действия, например таких, как цифровые корректирующие фильтры.

Известно устройство для умножения (1), содержащее блок сумматоров, в котором множимое вводится 2т+1 разрядами (т — разрядность числа), множитель т+1 разрядами, а произведение множимого íà (m+1) -й (знаковый) разряд множителя не добавляется, а вычитается из суммы частичных произведений.

Однако это устройство имеет большой объем оборудования при невысоком быстродействии.

Известно также устройство для умножения (2), наиболее близкое по техническому решению к изобретению, содержащее блок су мматоров и блок дополнения кодов отрицательных чисел.

В таком устройстве множимое, первоначально представленое т+1 разрядами, последовательным кодом подается на вход схемы, которая расширяет его íà m разрядов со стороны знакового разряда (на m единиц отрицательных чисел), множитель представлен в специальном регистре параллельным кодом, m+1 разрядами. В процессе умножения значащие разряды кода множителя управляют пропуском последовательного кода множимого (частичные произведения) в блок сумматоров на суммирование и образование суммы частичных произведений, а знаковый, управляя специальной схемой, обеспечивает вычитание из этой суммы соответствующего ему частичного произведения. Цикл умножения применительно к последовательным вычисли10 тельным устройствам включает т+1 периодов цифр для заполнения регистра множителя и 2m+1 периодов цифр для образования собственно произведения. Таким образом, цикл умножения в общей сложности составляет

15 Зот+1 периодов цифр.

Недостатком известного устройства является низкое быстродействие.

Цель изобретения — уменьшение цикла умножения до 2m+1 периодов цифр, т. е. по20 вышение быстродействия устройства.

Это достигается тем, что в устройство введены первый и второй блоки преобразования прямого кода в дополнительный и элемент И.

Первый вход элемента И соединен с первым

25 входом устройства, второй вход — с BTopbIM входом устройства, а выход — с первым входом первого блока преобразования прямого кода в дополнительный и с первым входом второго блока преобразования прямого кода

Зо в дополнительный. Второй вход первого блока

54

3 преобразования прямого кода в дополнительный связан с третьим входом устройства, а выход — с входом блока дополнения кодов отрицательных чисел, выход которого подключен к первому входу блока сумматоров, второй вход второго блока преобразования прямого кода в дополнительный — с четвертым входом устройства, а выход — с вторым входом блока сумматоров, выход которого подключен к выходу устройства.

Блок преобразования прямого кода в дополнительный содержит элемент памяти, динамический триггер, элемент И вЂ” HE и элемент

ИЛИ. Первый вход элемента памяти соединен с первым входом блока и первым входом элемента И вЂ” НЕ, второй вход — с вторым входом блока, а выход — с первым входом элемента ИЛИ, второй вход которого связан с выходом динамического триггера и вторым входом элемента И вЂ” HE, а выход — с входом динамического триггера, выход элемента И—

НŠ— с выходом блока.

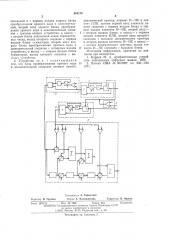

Блок-".хема устройства представлена на чертеже.

Устройство содержит первый 1 и второй

2 блоки преобразования прямого кода в дополнительный, блок 3 дополнения кодов отрицательных чисел, элемент И 4 и блок 5 сумматоров. Блок преобразования прямого кода в дополнительный содержит элемент 6 памяти, элемент 7 И вЂ” НЕ, элемент 8 ИЛИ, динамический триггер 9, Рассмотрим работу предлагаемого устройства в целом.

При умножении положительных чисел код множимого поступает через блок 1 преобразования прямого кода в дополнительный и блок 3 дополнения кодов отрицательных чисел на первый вход блока 5 сумматоров без изменения. Код множителя через блок 2 преобразования прямого кода в дополнительный проходит также без изменения на второй вход блока сумматоров, где последовательно во времени отпирает клапаны своими значащими разрядами. Так как комбинация открываемых клапанов в блоке 5 сумматоров соответствует кодовой комбинации множителя, а на входы каждого последующего сумматора подается результат предыдущего суммирования и задержанный соответствующим обр азом код множимого, то в результате суммирования частичных произведений на выходе блока сумматоров 5 образуется код произведения.

В случае умножения отрицательных чисел код множимого, проходя через блок 1, запущенный знаковым разрядом множителя, преобразуется в дополнительный по отношению к исходному, т. е. в код положительного числа.

Аналогичное пробразование претерпевает код множителя, проходя через блок 2. Дальнейшие операции проходят аналогично предыдущему случаю. При этом на выходе блока сумматоров 5 получают дополнительный код произведения.

1170

5 о

15 зо

4

При умножении чисел разных зубаков 803можны два случая, Когда множимое отрицательно, а множитель положителен, первый и второй блоки преобразования прямого кода в дополнительный не запускаются и соответствующие коды проходят через них без изменения, код множимого поступает на вход блока 3 в виде дополнительного кода отрицательного числа. При этом блок 3 дополнения кодов отрицательных чисел запускается и код множимого приходит на вход блока сумматоров дополненным единицами, следующими во времени за знаковым разрядом, так что в блоке сумматоров. происходит суммирование частичных произведений в следующей форме (т=8, а — зна-чение разрядов множителя, начиная с младшего): а1 (111111111 мантисса а2 ;11111111 мантисса а3 (1111111 мантисса а4>(111111 мантисса а5)(11111 мантисса а6)(1111 мантисса а7Х111 мантисса а8 11 мантисса что соответствует получению результата умножения в виде дополнительного кода отрицательного числа.

Второй случай, когда множимое положительно, а множитель отрицателен, сводится к предыдущему случаю. При этом знаковый разряд множителя запускает блоки 1 и 2, которые преобразуют соответствующие коды в дополнительные по отношению к исходным, после чего множимое становится отрицательным, а множитель — положительным.

Элементы управляемой линии задержки в блоке сумматоров обеспечивают необходимый сдвиг частичных произведений друг относительно друга. Клапаны управляемой линии задержки отпираются импульсами управления в те же моменты, в которые отпираются соответствующие клапаны значащими разрядами множителя. Запирание всех клапанов происходит одновременно, после поступления на первый вход блока сумматоров (2т+1) -го разряда множимого. При построении специализированных устройств, например таких, как цифровые корректирующие фильтры, предлагаемое устройство обеспечивает выигрыш по быстродействию примерно в 1,5 раза.

Формула изобретения

1. Устройство для умножения, содержащее блок сумматоров и блок дополнения кодов отрицательных чисел, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены первый и второй блоки преобразования прямого кода в дополнительный и элемент И, причем первый вход элемента И соединен с первым входом устройства, второй вход — с вторым входом устройства, а выход — с первым входом первого блока преобразования прямого кода в допол541170

Составитель А. Горностаев

Техред А, Камышннкова

Корректор Л. Орлова

Редактор И. Грузова

Заказ 2878/13 Изд, № 1896 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по,делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 нительный и с первым входом второго блока преобразования прямого кода в дополнительный, второй вход первого блока преобразования прямого кода в дополнительный соединен с третьим входом устройства, а выход— с входом блока дополнения кодов отрицательных чисел, выход:которого соединен с первым входом блока сумматоров, второй вход второго блока преобразования прямого кода в дополнительный соединен с четвертым входом устройства, а выход — с вторым входом блока сумматоров, выход которого соединен с выходом устройства.

2. Устройство по п, 1 отличающее ся тем, что блок преобразования прямого кода в дополнительный содержит элемент памяти, 6 динамический триггер, элемент И вЂ” НЕ и элемент ИЛИ, причем первый вход элемента памяти соединен с первым входом блока и первым входом элемента И вЂ” НЕ, второй вход—

5 с вторым входом блока, а выход — с первым входом элемента ИЛИ, второй вход которого соединен с выходом динамического триггера и вторым входом элемента И вЂ” НЕ а выход— с входом динамического три|ггера, выход эле10 мента И вЂ” НЕ соединен с выходом блока.

Источники информации, принятые во внимание при экспертизе:

1. Карцев М. А, Арифметические устройства электронных цифровых машин. 1958.

15 2. Патент США № 3610907, кл. 235 — 164, 1971.