Сумматор

Иллюстрации

Показать всеРеферат

(it) 541172

ОПИСАНИЕ

ИЗО6РЕТЕН И Я

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Ресофчик (61) Дополнительное к авт. свид-ву № 519709 (22) Заявлено 05.04.74 (21) 2015106/24 с присоединением заявки № (23) Приоритет

Опубликовано 30.12.76. Бюллетень № 48

Дата опубликования описания 25.01.77 (51) М. Кл. G 06F 7/50

Государственный комитет

Совета Министров СССР ло делам изобретений н открытий (53) УДК 681.325.5 (088.8) (72) Авторы изобретения

В. А. Грехнев, Н. П. Павлюченков и Ю. 3. Воробьев (71) Заявитель (54) СУММАТОР

Изобретение относится к области автоматики и вычислительной техники.

Известен сумматор по основному авт. св. № 519709, содержащий в каждом разряде счетный триггер, выполненный на элементах

И вЂ” НЕ, и дополнительные элементы И вЂ” НЕ.

В счетном триггере первые входы первого и второго элементов И вЂ” НЕ подключены к тактовой шине, а выходы — к первым входам третьего и четвертого элементов И вЂ” НЕ соответственно. Второй вход третьего элемента И вЂ” НЕ соединен с выходом четвертого элемента И вЂ” НЕ, а второй вход четвертого— с выходом третьего и первым входом пятого элементов И вЂ” HE, второй вход которого подключен к выходу первого, а выход — к первому входу шестого элемента И вЂ” НЕ. Второй вход шестого элемента И вЂ” НЕ подсоединен к выходу, а второй вход — к второму входу второго и входу седьмого элемента И вЂ” НЕ. Выход седьмого элемента И вЂ” НЕ соединен с вторым входом первого элемента И вЂ” НЕ.

Шина слагаемого и шина переноса из младшего разряда подключены к входам первого дополнительного элемента И вЂ” HE, шины инверсии слагаемого и инверсии переноса пз младшего разряда — к входам второго дополнительного элемента И вЂ” НЕ, а выходы дополнительных элементов И вЂ” НŠ— к третьим входам соответственно второго и шестого и первого и пятого элементов И вЂ” HE. Выходы шестого и седьмого элементов И вЂ” НЕ являются выходами переноса и инверсии переноса в старший разряд.

С помощью этого сумматора нельзя производить вычитание двоичных чисел.

Цель изобретения — расширение функциональных возможностей сумматора.

Для этого в каждый разряд сумматора введены два элемента И вЂ” НЕ, первые входы которых объединены и подключены к шине разрешения вычитания, вторые входы подсоединены соответственно к шинам инверсии слагаемого и слагаемого, третьи входы — к

15 шинам переноса и инверсии переноса из младшего разряда, а выходы соединены соответственно с четвертыми входами шестого, второго и первого, пятого элементов И вЂ” НЕ, входящих в состав счетного триггера. Третьи

20 входы дополнительных элементов И вЂ” НЕ объединены и подключены к шине разрешения сложения.

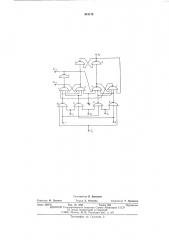

На чертеже представлена функциональная схема одного разряда сумматора.

25 Элементы И вЂ” НЕ 1 — 7 образуют счетный триггер. Шины слагаемого и переноса из младшего разряда подключены к первому и второму входам дополнительного элемента

И вЂ” НЕ 8, шины инверсии слагаемого и пн30 версии переноса из младшего разряда — к

541172

Таблица 1

И вЂ” НЕ

14 I

3 i (t+1) Xl, с; с/+1

5 6 7

10 11

35 первому и второму входам дополнительного элемента И вЂ” HE 9. Третьи входы этих элементов объединены и подсоедипены к шине разрешения сложения. К входам введенного элемента И вЂ” НЕ 10 подключены шины инверсии слагаемого, переноса из младшего разряда и разрешения вычитания, а к входам введенного элемента И вЂ” НЕ 11 — шины слагаемого, инверсии переноса из младшего разряда и разрешения вычитания. Результат суммирования или вычитания y„(t+ 1) будет получен на выходе элемента И вЂ” HE 2, сигнал переноса в старший разряд с;+1 и его инверсия c,+> на выходах элементов И вЂ” НЕ

4 и 3, тактовая шина подключена к входам элементов И вЂ” HE 5 и 6.

В режиме сложения на шину разрешения сложения подан сигнал, равный логической единице, а на шину разрешения вычитания— сигнал, равный логическому нулю. Сигнал переноса в старший разряд и его инверсия формируются элементами И вЂ” НЕ 3, 4, 7 — 11.

Поскольку в начальный момент сигнал на тактовой шине отсутствует, то на выходах элементов И вЂ” НЕ 5 и 6 присутствует сигнал логической единицы и связи с выходов этих

В режиме вычитания на шину разрешения сложения подан сигнал, равный логическому нулю, а на шину разрешения вычитания— сигнал, равный логической единице, Сумматор в режиме вычитания работает аналогичным образом за исключением того, что по шине переноса из младшего разряда поступает инверсия сигнала заема из младшего разряда, а по шине инверсии переноса из

25 элементов на входы эле1иентой И вЂ” НЕ 4 и 7 не влияют на формирование сигнала переноса. В момент изменения состояния счетного триггера под действием тактового сигнала эти связи позволяют «запомнить» предыдущее значение сигнала переноса в старший разряд на время действия тактового сигнала, т. е. сигнал переноса в старший разряд меняет свое значение в тот момент времени, когда отсутствует тактовый сигнал. Изменение состояния элемента И вЂ” НЕ 5 происходит в том случае, если счетный триггер находится в состоянии «1», а значения сигналов переноса из младшего разряда и второго слагаемого не равны между собой; состояние элемента И вЂ” НЕ 6 изменяется тогда, когда счетный триггер находится в состоянии «0», а значения сигналов переноса из младшего разряда, и второго слагаемого так же не рав-. ны между собой. В табл. 1 приведены значе-. ния выходных сигналов элементов И вЂ” HE, а также результат суммирования у;(1+1) в зависимости от предыдущего состояния счетного триггера (у, (L) ) и значений входных сигналов, позволяющие проследить все возможные ситуации, возникающие в процессе суммирования. младшего разряда — сигнал заема из младшего разряда. Значение выходных сигналов элементов И вЂ” HE, а также результат вычитания у;(1+1) в зависимости от предыдущего состояния счетного триггера (у;(1) ) и значений входных сигналов, позволяющие проследить все возможные ситуации, возникаю. щие в процессе вычитания, приведены в табл. 2.

541172

Таблица 2

I ус(1) !! (И вЂ” HE

9 10 11 !

Х1

7 8

О О, 1

0 0 1

0 0 1

О: О 1

О 1 О

О, 1,, О

О 1 О

О 1 О

Таким образом, в данном устройстве за счет незначительного увеличения оборудования расширяются функциональные возможности сумматора, с помощью которого становится возможным вычитание двоичных чисел в прямых кодах. вторые входы подключены соответственно к шинам инверсии слагаемого и слагаемого, третьи входы — к шинам переноса и инверсии переноса из младшего разряда, а выходы соединены соответственно с четвертыми входами шестого, второго и первого, пятого элементов И вЂ” НЕ, входящих в состав счетного триггера, третьи входы дополнительных элементов И вЂ” НЕ объединены и подключены к шине разрешения сложения.

Источник информации, принятый во внимание при экспертизе:

1. Лвт. св. № 519709, кл. G 06F 7/50, 1972 (прототип).

Формула изобретения

Сумматор по авт. св. № 519709, отлич ающи и с я тем, что, с целью расширения его функциональных возможностей, в каждый разряд сумматора введены два элемента

И вЂ” НЕ, первые входы которых объединены и подключены к шине разрешения вычитания, 0

О

1

О

О

1

О

1

О

О

О

О

1

О

О

1

О

О

1

1

1

1

1

1

О

1

1

О

1

1

1

1

О

1

О

О

О

1

1

О

О

1

1

1

О

О

1

1

1

1

1

1

1

1

541172

Составитель В. Березкин

Техред E. Петрова

Редактор И. Грузова

Корректор Т. Гревцова

Типография, пр. Сапунова, 2

Заказ 2897/5 Изд. № 1898 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 5К-35, Раушская наб., д. 4/5