Сумматор

Иллюстрации

Показать всеРеферат

ц 54Ц73

ОП ИСАНИ Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (б1) Дополните чьное к авт свид ву 519709 (22) Заявлено 11.10.74 (21) 2067386/24 с присоединением заявки X (51) М. Кл з G 06F 7/50

Совета йкннистров СССР по лелем изобретений и открытий (53) УДК 681 325 5 (088.8) Опубликовано 30,12.76. Бюллетень № 48

Дата опубликования описания 25.01.77 (72) Авторы изобретения

В. А. Грехнев и H. П. Павлюченков (71) Заявитель (54) СУММАТОР

Государственный комитет (23) Приоритет

Изооретенис озпос тся к вычислительной тсхнике.

По основному авт. св. № 519709 известен сумматор, содержащий в каждом разряде счетный триггер, выполненный на элементах

И вЂ” НЕ и дополнительные элементы И вЂ” НЕ, причем в счетном триггере первые входы первого и второго элементов И вЂ” НЕ подключены к тактовой шине, а выходы — к первым входам третьего и четвертого элементов И—

НЕ соответственно, второй вход третьего элемента И вЂ” НЕ соединен с выходом четвертого элемента И вЂ” НЕ, а второй вход четвертого— с выходом третьего и первым входом пятого элемента И вЂ” HE, второй вход которого подключен к выходу первого, а выход — к первому входу шестого элемента И вЂ” НЕ, второй вход шестого элемента И вЂ” НЕ подключен к выходу второго, а выход — к второму входу второго и входу седьмого элементов И вЂ” НЕ, выход седьмого элемента И вЂ” HE соединен с вторым входом первого элемента И вЂ” HE, шина слагаемого и шина переноса из младшего разряда подключень: к входам первого дополнительного элемента И вЂ” HE, а шины инверсии слагаемого и инверсии переноса из младшего разряда подключены к входам второго дополнительного элемента И вЂ” НЕ, а выходы дополнительных элементов И вЂ” НЕ подключены к третьим входам соответствеино второго и шестого и первого и zioru элементов И вЂ” НЕ, выходы шестого н седьмого элементов И вЂ” НЕ являются выходами переноса и инверсии переноса в старший разряд.

Известный сумматор не позволяет после сложения осуществить сдвиг информации.

Целью изобретения является расширение функциональных возможностей устройства.

Это достигается тем, что в каждый разряд

10 предлагаемого сумматора введены два элемента И вЂ” НЕ, первые входы которых объединены и подключены к шине разрешения переноса, вторые входы подключены соответственно к шинам инверсии переноса и пе15 реноса из младшего разряда, а выходы соединены с четвертыми входами первого и второго элементов И вЂ” НЕ, входящих в состав счетного триггера, а третьи входы дополнительных элементов И вЂ” НЕ объединены и

23 подключены к шине разрешения сложения.

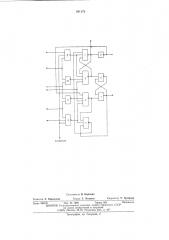

На чертеже изображена функциональная схема i-го разряда сумматора.

Элементы И вЂ” НЕ 1 — 7 образуют счетный триггер; 8, 9 — дополнительные элементы И—

25 НЕ; 10, 11 — вновь введенные элементы И—

НЕ.

Выходы элементов И вЂ” НЕ 7, 1 и 5 являются выходами суммы переноса и инверсии переноса в старший разряд из данного разря3 да. Тактовая шина подключена к входам

541173 элементов И вЂ” НЕ 2 и 3, шины слагаемого и инверсии слагаемого соответственно к входам элементов И HE 8 и 9, шина переноса из младшего разряда †входам элементов

И вЂ” НЕ 8 и 10, шина инверсии переноса из младшего разряда †входам элементов И—

НЕ 9 и 11, шина разрешения сдвига подключена к входам элементов И вЂ” НЕ 10 и 11, а шина разрешения сложения — к входам элементов И вЂ” НЕ 8 и 9.

В режиме сложения на шину разрешения сдвига подан сигнал, равный логическому нулю, а на шину разрешения сложения— сигнал, равный логической единице. Из анализа чертежа видно, что элементы И вЂ” НЕ 1, 4, 5, 8 и 9 образуют комбинационную схему выработки сигнала переноса. Поскольку в начальный момент времени тактирующий сигнал отсутствует, равен логическому нулю, то на выходах элементов И вЂ” НЕ 2 «3 — логическая единица и связи с выходов этих элементов на входы элементов И вЂ” НЕ 1 и 4 не влияют на формирование сигнала переноса, а в момент изменения состояния триггера под действием тактирующего сигнала эти связи позволяют «запомнить» предыдущее значение сигнала переноса на время действия тактирующего сигнала, т. е. сигнал переноса меняет свое значение В тот момент Времени, когда отсутствует тактирующий сигнал, С приходом тактирующего сигнала появление на выходе элемента И вЂ” HE 2 логического нуля происходит в случае, если триггер памяти находится в единичном состоянии, а значения сигналов переноса и второго слагаемого не равны между собой, аналогично, появление логического нуля на выходе элемента И вЂ” НЕ 3 происходит в случае, если триггер памяти находится в нулевом состоянии, а значения сигналов переноса и второго слагаемого опять не равны между собой.

Таким образом, с приходом тактирующего сигнала в триггере образуется результат суммирования предыдущего значения триггера со значениями второго слагаемого и переноса.

В режиме сдвига на шину разрешения сдвига подан сигнал, равный логической единице, а па шину разрешения сложения — сиг5

Зо

45 нал, равный логическому нулю, который закрывает элементы И вЂ” HE 8 и 9. В этом случае значение сигнала на выходе элемента

И вЂ” НЕ 1 совпадает со значением сигнала на выходе триггера и запоминается на время действия тактирующего сигнала. Поскольку. выходы элементов И вЂ” НЕ 5 и 1 предыдущего разряда соединены с входами элементов

И вЂ” НЕ 11 и 10 данного разряда, то с приходом тактирующего сигнала логический нуль на выходе элемента И НЕ 3 данного разряда появится в случае, если триггер этого разряда находится в нулевом состоянии, а триггер предыдущего разряда в единичном состоянии. Аналогично, логический нуль на выходе элемента И вЂ” НЕ 2 данного разряда появится в случае, если триггер этого разряда находится в единичном состоянии, а триггер предыдущего разряда в нулевом состоянии.

Это соответствует сдвигу информации из предыдущего разряда в данный. Процесс сдвига в остальных разрядах происходит аналогичным образом.

Таким образом, данное устройство позволяет не только суммировать коды чисел, но и последовательно сдвигать информацию, находящуюся в триггерах памяти сумматора, что ведет к расширению функциональных возможностей устройства.

Формула изобретения

Сумматор по авт. св. М 519709, о тл и ч аю шийся тем, что, с целью расширения его функциональных возможностей, в каждый разряд сумматора введены два элемента

И вЂ” НЕ, первые входы которых объединены и подключены к шине разрешения переноса, вторые входы подключены соответственно к шинам инверсии переноса и переноса из младшего разряда, а выходы соединены с четвертыми входами первого и второго элементов И вЂ” HE, входящих в состав счетного триггера, третьи входы дополнительных элементов И вЂ” НЕ объединены и подключены к шине разрешения сложения.

Источники информации, принятые во внимание при экспертизе:

1. Авт. св. СССР Мо 519709, кл. G 06F

7/50, 1972 (прототип).

541173

Слсжсиие

Составитель В. Березкин

Техред E. Петрова

Корректор T. Гревцова

Редактор Е. Караулова

Типография, пр. Сапунова, 2

Заказ 2897/6 Изд. № 1898 Тираж 864 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, 7К-35, Раушская наб., д. 4/5